1

The Transaction-Based Verification Methodology

Cadence Berkeley Labs, Technical Report # CDNL-TR-2000-0825, August 2000.

Dhananjay S. Brahme, Steven Cox, Jim Gallo

1

, Mark Glasser, William Grundmann, C. Norris Ip,

William Paulsen, John L. Pierce, John Rose, Dean Shea, Karl Whiting

Keywords verification, simulation, test bench,

transaction, system-on-chip (SoC).

Abstract

This paper summarizes a transaction-based verification

methodology (TBV) that makes functional verification of

RTL descriptions using simulation more effective By raising

the verification effort to a higher level of abstraction, an

engineer can develop and diagnose tests from a system level

perspective. This capability enhances the reusability of each

component in the test benches. It improves the debugging

and coverage analysis process by presenting information in

terms of transactions and their relationships, rather than sig-

nals and waveforms.

Several designs have been verified using this methodol-

ogy. It was found that TBV can be mastered by hardware

engineers in a short time, and the teams were able to iden-

tify and fix design errors quickly.

1. Introduction

Developing an effective test suite for an HDL design is an

arduous process. With exploding design sizes, we need to

generate a large amount of high quality stimulus with a min-

imum of effort. While the test benches should be exercising

the design thoroughly, they should also be self-checking to

avoid manual confirmation of expected operation. It should

be easy to check the activities in a simulation run to identify

problems in the design. It should also be easy to analyze the

resulting coverage of the design to access the quality of the

test suites.

The transaction-based verification methodology (TBV) is

designed to make it easy to create and reuse test benches, to

debug simulation runs, and to analyze coverages by intro-

ducing the concept of transactions to the verification tools.

It was introduced in 1998 [1,2,3] and integrated into a verifi-

cation tool suite in 1999 [4,5]. The corresponding C++

library for transaction-based test bench authoring is released

in 2000 as an open-source licensed software [6,7]. A similar

work can be found in [8].

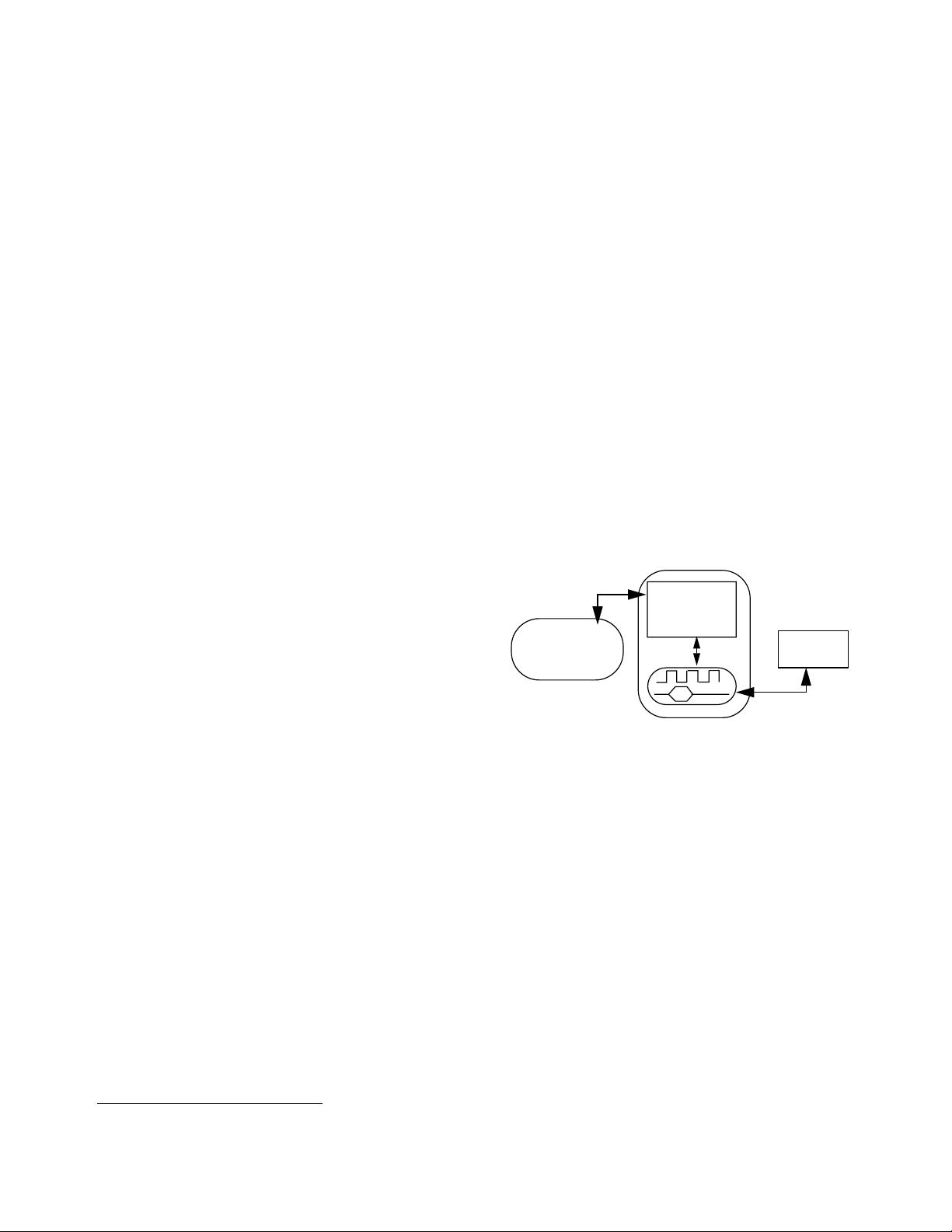

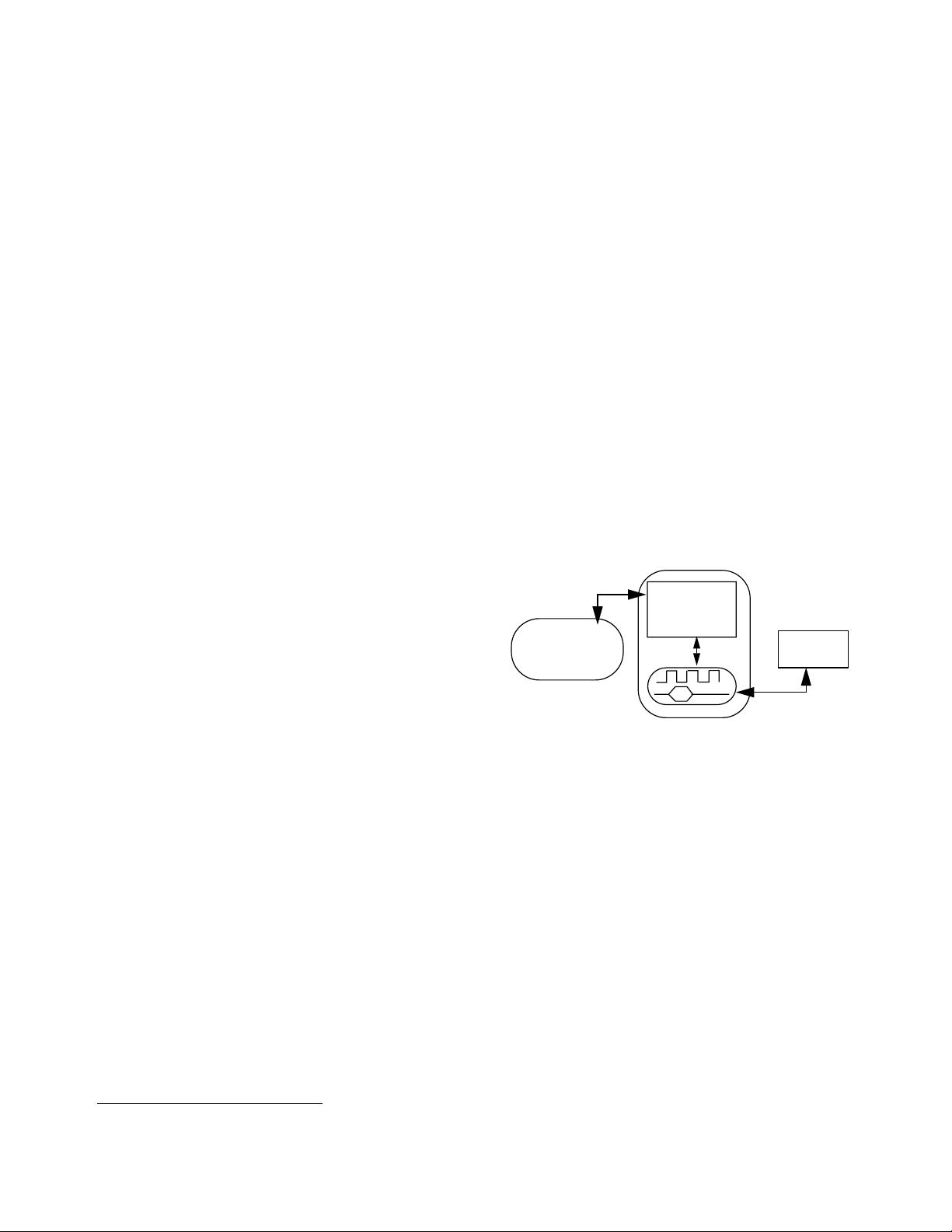

In short, TBV uses the concept of transactions to raise the

verification effort to a higher level of abstraction for the pur-

pose of improved productivity. It fundamentally relies on

separating a test bench into two layers, as shown in Figure

1. The top layer is the tests, which orchestrate transaction-

level activity in the system without regard to the specific

detail of signal-level protocols on the design's interfaces.

The bottom layer is the transaction verification model

(TVM), which provides the mapping between transaction-

level requests made by the tests and detailed signal-level

protocols on the design's interfaces.

Figure 1: A layered test bench

With the separation of responsibility into these two lay-

ers, many new and complex tests can be developed quickly,

as the detailed protocols are already captured in the TVM

layer. Although this separation of responsibility can be per-

formed manually on any test bench authoring tool, it is

much easier to use a test bench authoring tool that explicitly

supports transactions, to speed up the learning process, to

guide the user to model their test benches in an appropriate

style, and to simplify the coding. This strategy allows reuse

of individual components in the test bench. Similar discus-

sion in reusability can be found in [9,12].

Furthermore, a better productivity gain can be obtained if

the debugging tools and the coverage tools can communi-

cate and work with the test bench authoring tools in terms of

transactions. With these tools, a user can

■ write new self-checking tests easily in terms of

transactions, and pass this information to other tools,

1. no longer with Cadence (work done while at

Cadence Design Systems, Inc.).

proc.doRead;

proc.doWrite;

...

design

signals

doRead

addr = 0xFF

data = 0xF

transactions

test

transaction

verification model (TVM)

Cadence Design Systems, Inc.