FPGA时钟电路设计:减小时钟偏差策略

"本文主要介绍了基于FPGA的时钟电路设计,强调了FPGA时钟树的特性和重要性,特别是在使用DCM和BUFGMUX等特殊资源时如何手动搭建时钟电路以减小时钟偏差对电路时序的影响。"

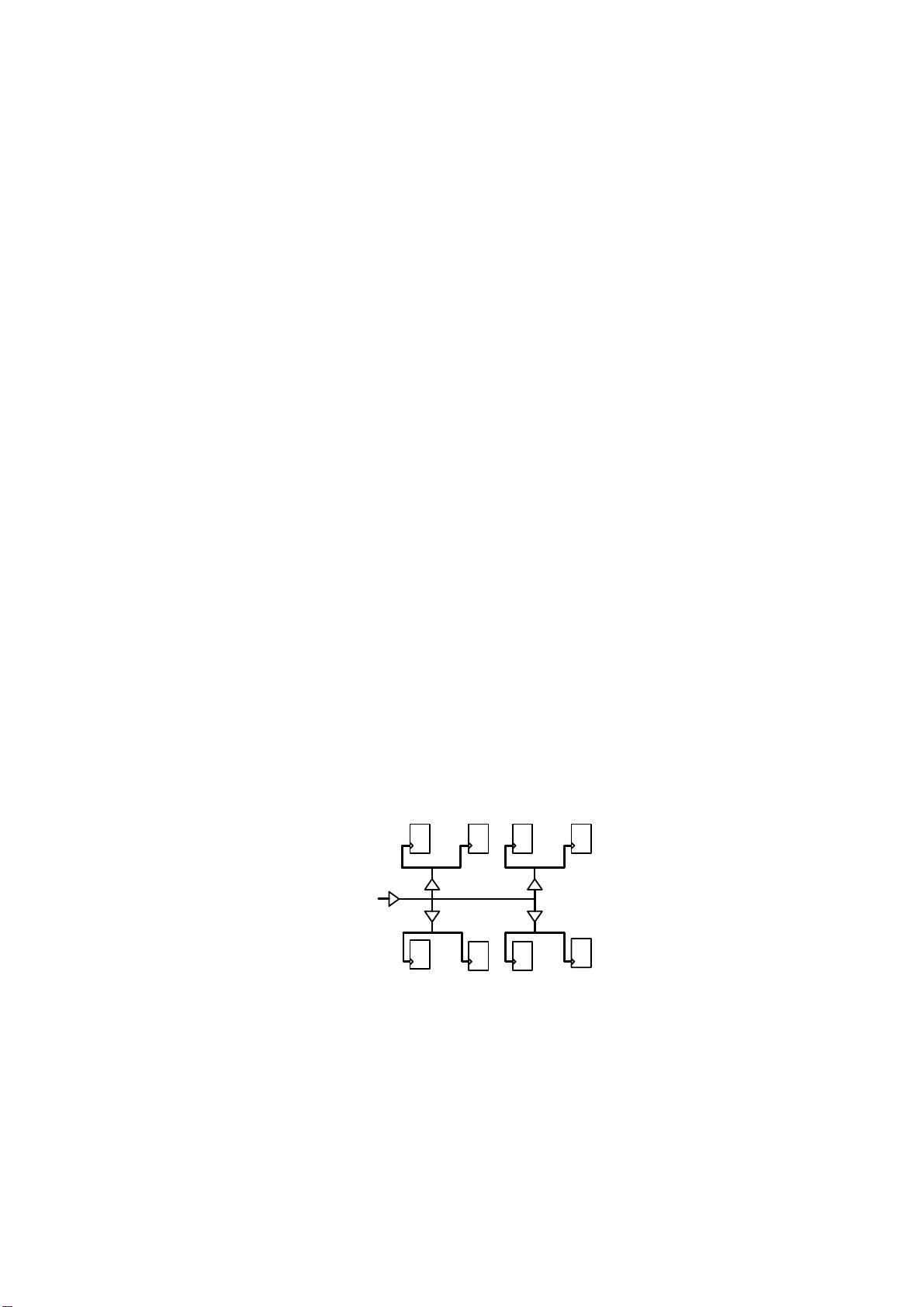

在数字集成电路设计中,时钟管理是至关重要的,尤其是对于基于FPGA的系统。FPGA(现场可编程门阵列)提供了专用的时钟资源,如数字时钟管理单元(DCM)和全局时钟选择缓冲器(BUFGMUX),以帮助设计者构建高效的时钟电路。与ASIC(专用集成电路)不同,FPGA的时钟设计需要特别考虑,因为它们的内部连线延迟相对于门延迟较大,这使得简单的自动化方法无法有效地解决时钟偏差问题。

在ASIC设计中,时钟树通常由自动布局布线工具动态构建,确保时钟信号到达所有寄存器的时间大致相等。但在FPGA中,由于内部连线的预定义性,这种方法不再适用。相反,设计者需要利用FPGA提供的特殊资源来手动优化时钟树,以减少时钟偏差对电路性能的影响。

DCM是FPGA中用于时钟管理和调理的关键组件。它能提供时钟分频、倍频、反相和相位移位等功能,以生成多个不同频率和相位的时钟,满足系统中不同模块的需求。通过精确控制DCM,设计者可以降低时钟偏移,保证整个系统内的同步性。

BUFGMUX则是全局时钟选择缓冲器,用于分配全局时钟信号到FPGA的不同部分。它允许设计者根据需要选择不同的时钟源,或者在不同时钟域之间切换,以适应灵活的系统需求。通过巧妙地配置BUFGMUX,可以进一步减少时钟路径的延迟差异,从而改善时钟同步。

时钟偏差对电路时序的影响不容忽视,它可能导致数据采样错误和逻辑错误。为了最大限度地减少这些影响,设计者需要理解和掌握FPGA特有的时钟管理策略,包括正确使用DCM和BUFGMUX。此外,理解并优化时钟树的结构,如确保时钟信号路径的均衡,也是提高FPGA设计性能的关键。

FPGA时钟设计是一项复杂但至关重要的任务,需要深入理解FPGA内部工作原理和特性。通过合理利用DCM和BUFGMUX,结合手动优化时钟树结构,可以实现高效且时序可靠的FPGA系统。对于FPGA开发者而言,掌握这些知识是确保设计成功的关键步骤。

点击了解资源详情

279 浏览量

318 浏览量

2021-09-20 上传

154 浏览量

2012-12-09 上传

200 浏览量

481 浏览量

178 浏览量

o悟空o

- 粉丝: 0

最新资源

- ITween插件实用教程:路径运动与应用案例

- React三纤维动态渐变背景应用程序开发指南

- 使用Office组件实现WinForm下Word文档合并功能

- RS232串口驱动:Z-TEK转接头兼容性验证

- 昆仑通态MCGS西门子CP443-1以太网驱动详解

- 同步流密码实验研究报告与实现分析

- Android高级应用开发教程与实践案例解析

- 深入解读ISO-26262汽车电子功能安全国标版

- Udemy Rails课程实践:开发财务跟踪器应用

- BIG-IP LTM配置详解及虚拟服务器管理手册

- BB FlashBack Pro 2.7.6软件深度体验分享

- Java版Google Map Api调用样例程序演示

- 探索设计工具与材料弹性特性:模量与泊松比

- JAGS-PHP:一款PHP实现的Gemini协议服务器

- 自定义线性布局WidgetDemo简易教程

- 奥迪A5双门轿跑SolidWorks模型下载