UVM实战学习笔记:factory、TLM、phase与sequence解析

需积分: 50 8 浏览量

更新于2024-07-18

4

收藏 1.16MB PDF 举报

"UVM实战笔记,主要涵盖了UVM的基础知识,包括factory机制、TLM传输、phase机制以及sequence和sequencer的相关内容。笔记参考了《UVM实战(卷1)》第1版以及《uvm1.1应用指南及源代码分析》PDF,结合UVM源代码和书中示例进行学习。"

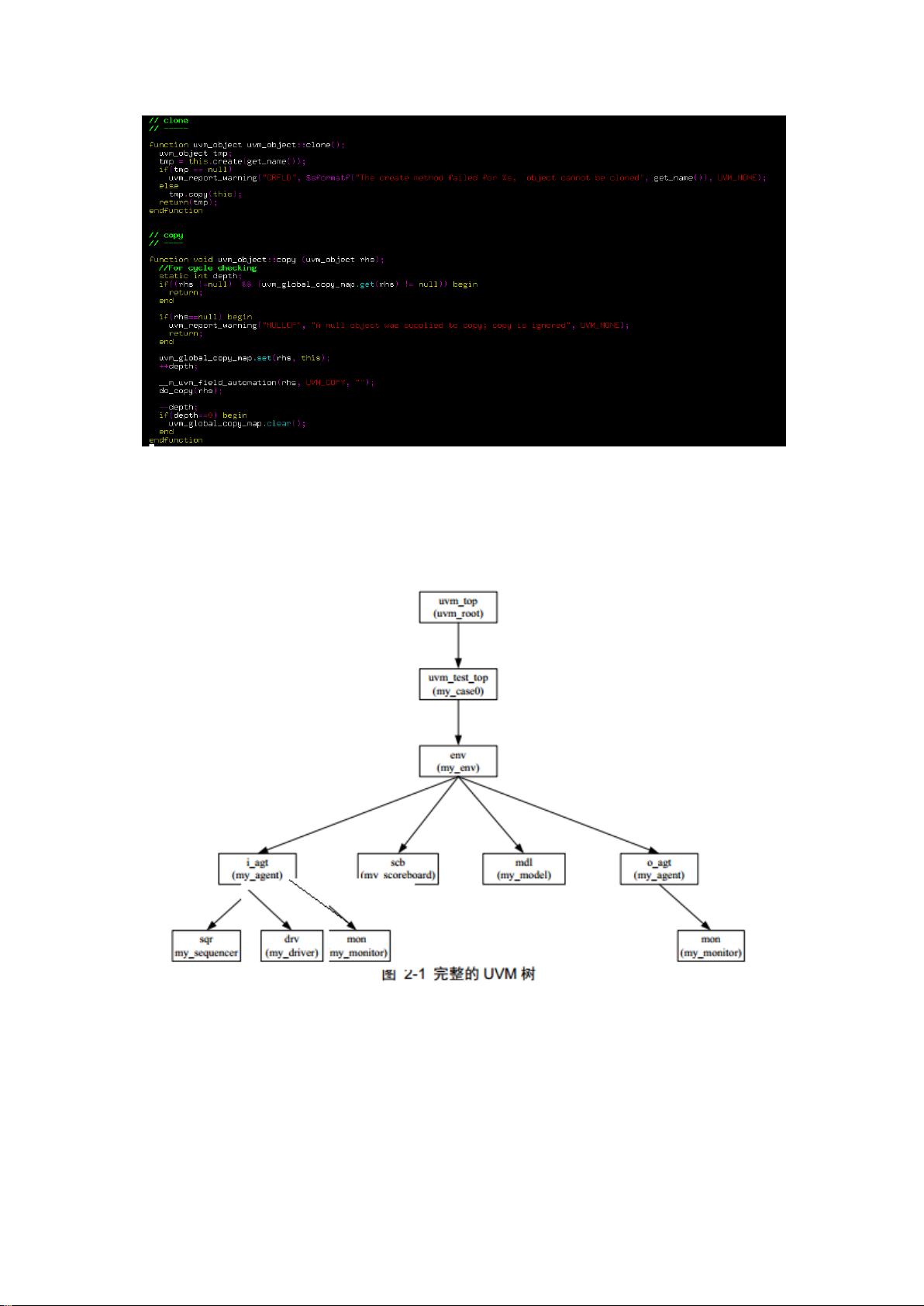

UVM(Universal Verification Methodology,通用验证方法论)是一种广泛用于系统级验证的框架,它提供了一套标准的组件、接口和编程模式,使得验证工程师能够构建可复用、模块化的验证环境。以下是对UVM中重要知识点的详细说明:

1. **Factory机制**:UVM的Factory是基于配置数据库(config_db)实现的动态对象创建机制。它允许在运行时通过配置设置来动态地选择要实例化的类,使得设计具有更高的灵活性和可扩展性。Override config_db允许用户覆盖默认的类创建行为,实现自定义组件实例化。

2. **Transaction Level Modeling (TLM)**:TLM是UVM的核心组成部分,它定义了数据在验证环境中如何传输的标准接口。TLM分为简单传输(TLM-1)和高级传输(TLM-2),提供了请求-响应模型,支持阻塞和非阻塞传输,以及多种传输类型,如单向、双向等,使得数据交换更加高效和灵活。

3. **Phase机制**:UVM的Phase机制管理验证组件的生命周期,确保它们在正确的时间执行必要的操作,如初始化、构建、连接、启动和结束等。通过phase,UVM组件可以协调动作,比如在特定阶段启动sequence,或者在另一阶段收集数据。

4. **Sequence-Sequencer**:Sequences是UVM中生成和控制transaction的类,它们描述了数据流的行为。Sequencers是sequence的调度器,负责管理sequence的执行顺序,将sequence产生的transaction分配给driver。Virtual Sequences和Sequencer Extensions(SQR)进一步增强了sequence的功能,允许更复杂的并发和同步控制。

5. **Components和Object的关系**:`uvm_component`是UVM的基础组件,用于构建验证环境的结构。`uvm_object`则是所有数据对象的基类,包括transaction和sequence。例如,`uvm_sequence_item`是driver从sequencer获取的transaction对象,而`uvm_sequence`是控制sequence_item生成和发送的类。`uvm_driver`是与DUT交互的组件,它处理从sequencer接收到的transaction,并将其转化为信号级的操作。`uvm_monitor`用于捕获DUT的行为,`uvm_scoreboard`则用于比较预期结果和实际观测到的数据。

这些知识点构成了UVM验证方法论的核心,理解和熟练掌握它们对于有效地使用UVM进行系统级验证至关重要。在实际应用中,结合UVM提供的源代码、示例和相关指南,可以更深入地了解和运用这些概念。

339 浏览量

423 浏览量

1000 浏览量

423 浏览量

1000 浏览量

513 浏览量

207 浏览量

185 浏览量

UTUMAN

- 粉丝: 50

最新资源

- ABAP基础操作与系统字段详解

- Linux Kernel中文版详解:硬件与软件基础、存储管理和进程管理

- 精通Linux:从新手到高手的实战教程

- 3S技术集成与应用探索

- LPC2000系列MCU使用SPI接口访问MMC卡教程

- ArcGIS Engine白皮书:基于ESRI技术的自定义GIS应用开发指南

- Oracle数据库入门:从基础到SQL操作

- DOS命令详解:ping与ipconfig的使用技巧

- Visual C++ MFC入门教程:面向对象的Windows应用开发

- Struts2 框架深度解析

- AS/400 RPG语言编程指南

- SAP BAPI 用户指南:高级教程

- 深入学习Svn客户端:服务器功能、TortoiseSVN安装与工作流程

- Compass: Java搜索引擎框架, Hibernate替代方案(最新1.1M1版)

- Linux内核0.11详解与编译指南

- STL常见修改算法详解