5

4

3

2

1

D D

C C

B B

A

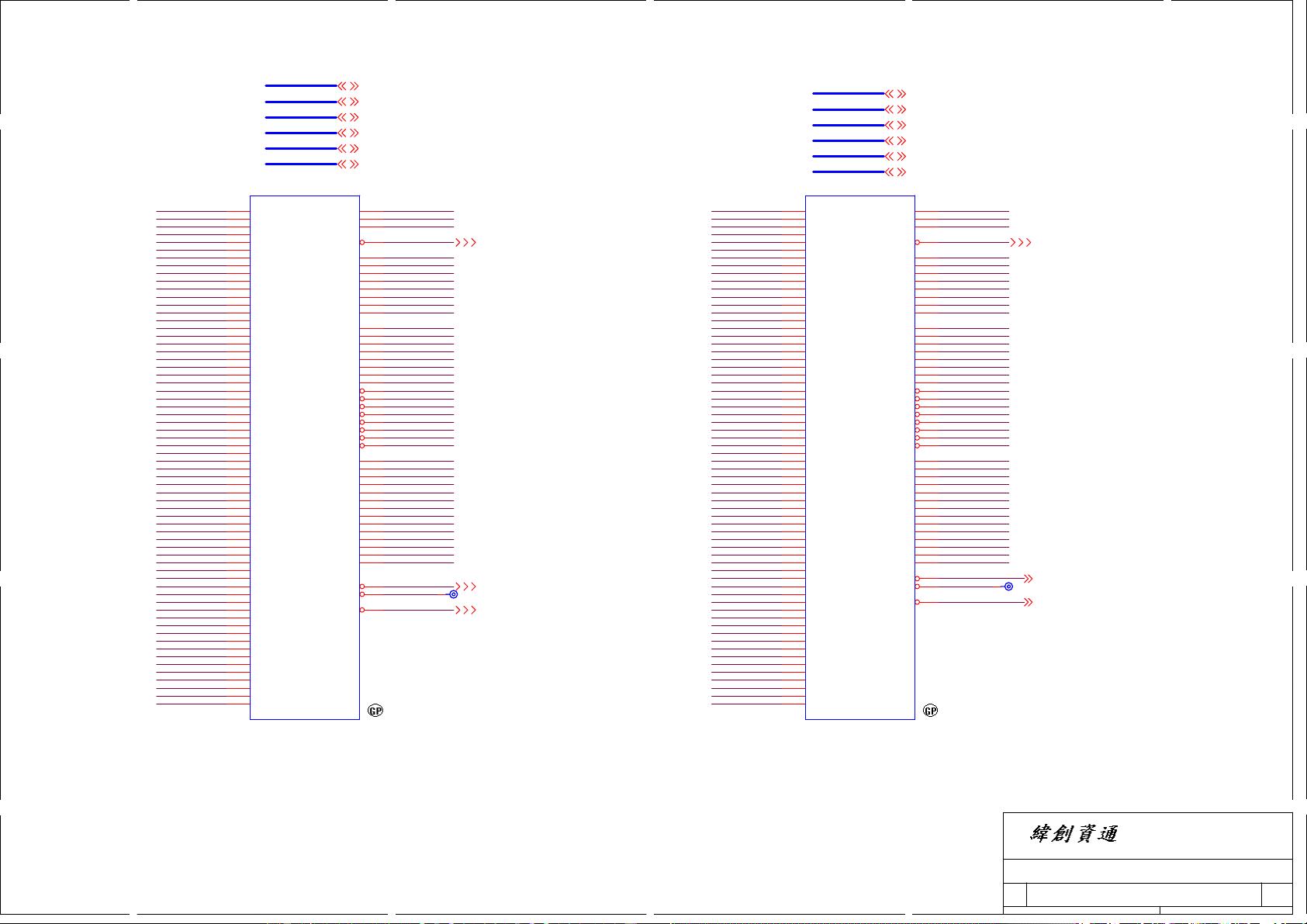

M_COMP

M_LUMA

M_CRMA

M_RED

M_GREEN

LVDS_IBG

CRT_VSYNC

CRTIREF

PEGCOMP

M_BLUE

CRT_HSYNC

1D05V_S0

3D3V_S0

3D3V_S0

LBKLT_CTL16

BLON_IN31

LDDC_CLK16

LDDC_DATA16

LCDVDD_EN16

VGA_TXACLK-16

VGA_TXACLK+16

VGA_TXAOUT0-16

VGA_TXAOUT1-16

VGA_TXAOUT2-16

VGA_TXAOUT0+16

VGA_TXAOUT1+16

VGA_TXAOUT2+16

GMCH_DDCCLK15

GMCH_DDCDATA15

VGA_TXBCLK+16

VGA_TXBCLK-16

VGA_TXBOUT0+16

VGA_TXBOUT2-16

VGA_TXBOUT1-16

VGA_TXBOUT0-16

VGA_TXBOUT2+16

VGA_TXBOUT1+16

GMCH_VSYNC15,17

GMCH_HSYNC15,17

M_COMP15

M_LUMA15

M_CRMA15

M_BLUE15

M_GREEN15

M_RED15

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs

SC

CRESTLINE(3/6)-VGA/LVDS/TV

A3

941

Monday, December 18, 2006

<Core Design>

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs

SC

CRESTLINE(3/6)-VGA/LVDS/TV

A3

941

Monday, December 18, 2006

<Core Design>

Title

Size Document Number Rev

Date: Sheet

of

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Pamirs

SC

CRESTLINE(3/6)-VGA/LVDS/TV

A3

941

Monday, December 18, 2006

<Core Design>

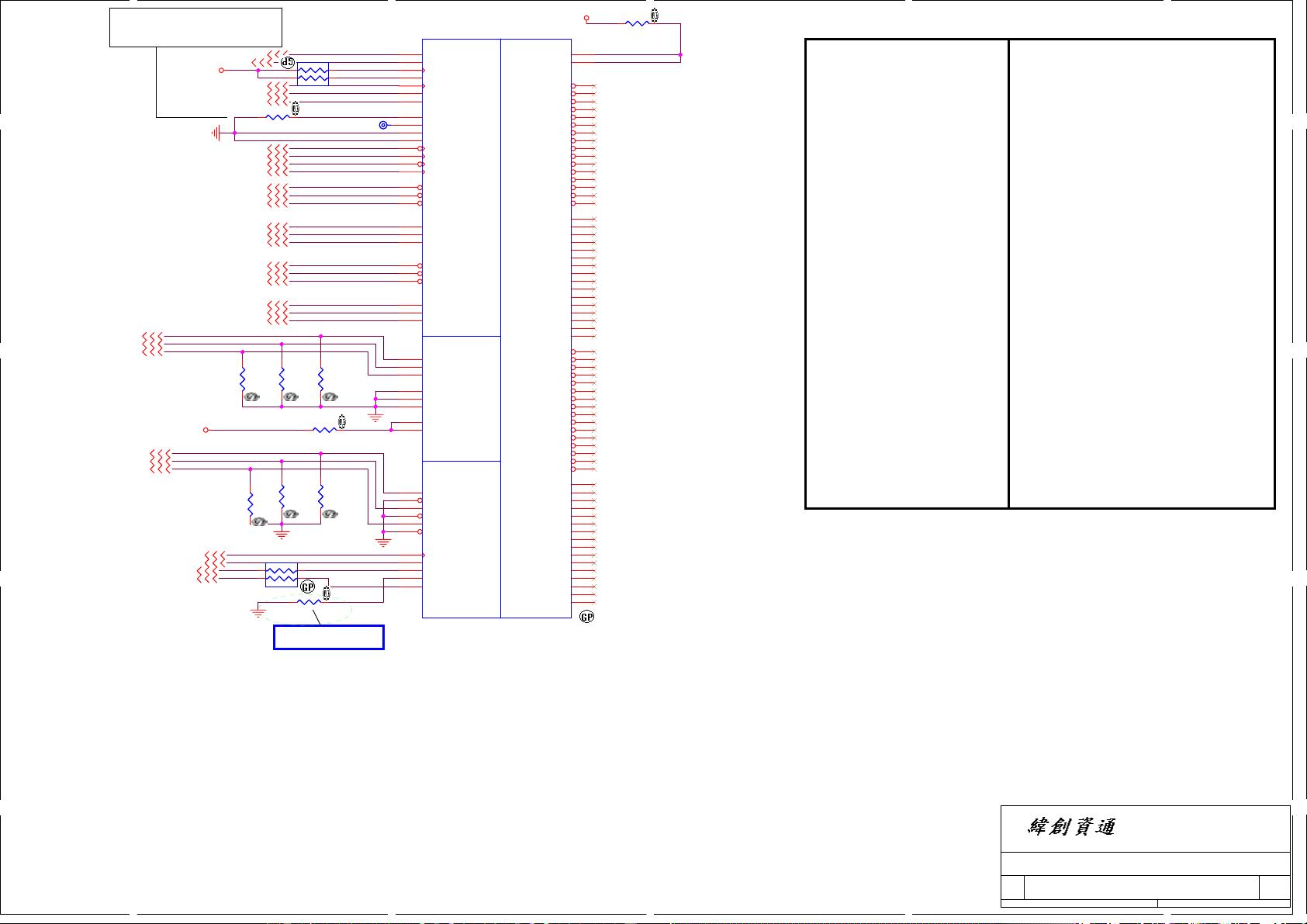

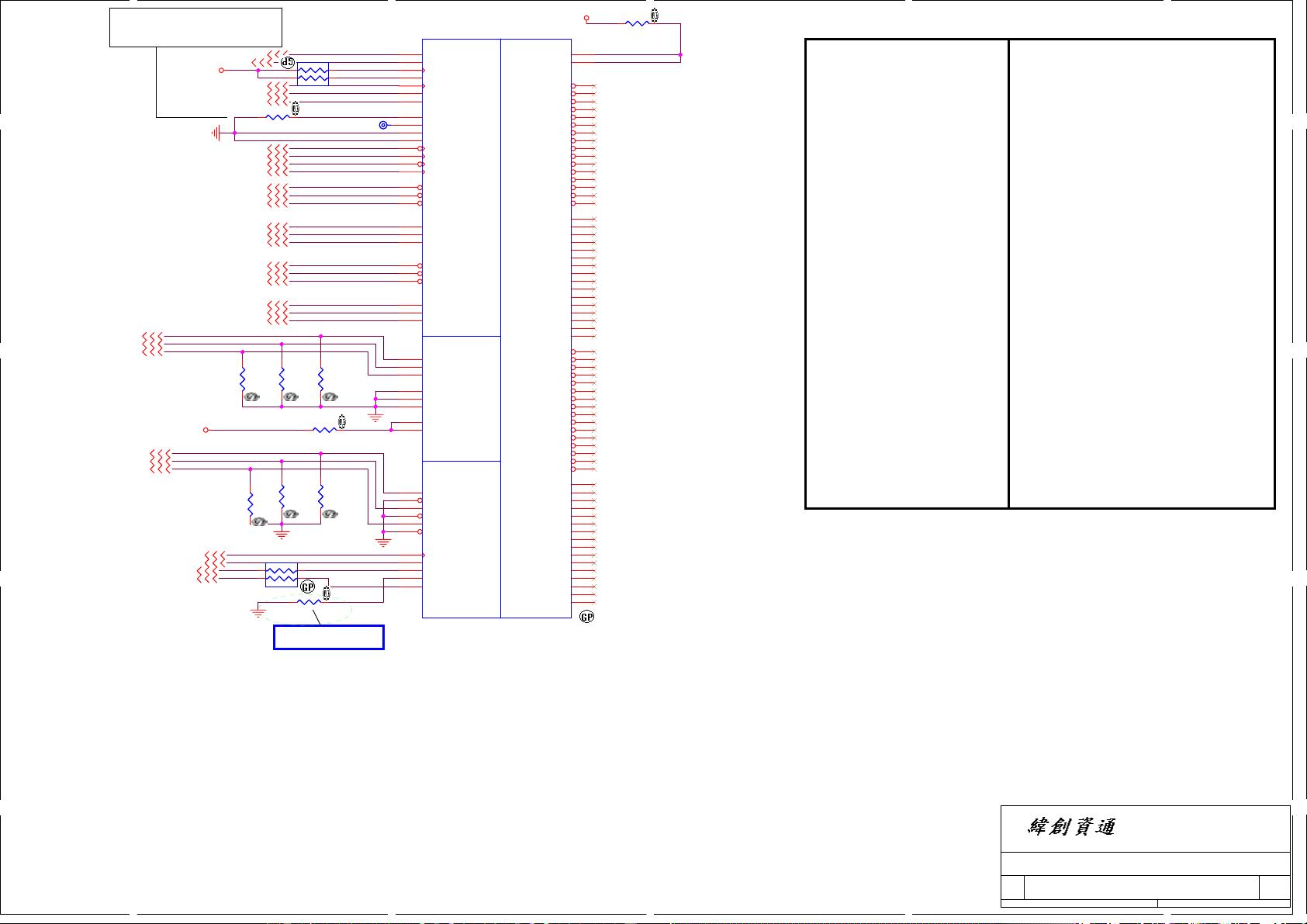

1 = Enable *

CFG[18:17] Reversed

SDVO_CTRLDATA 0 = No SDVO Device Present *

1 = SDVO Device Present

CFG19(DMI Lane Reversal)

0 = Normal Operation *

(Lane number in Order)

1 = Reverse lane

CFG20(PCIE/SDVO consurrent)

0 = Only PCIE or SDVO is operational *

1 = PCIE/SDVO are operating simu.

Strap Pin Table

PEGCOMP trace

width and spacing

is 20/25 mils.

CFG[2:0] FSB Freq select

FOR Calero: 255 ohm

Crestline: 1.3k ohm

010 = FSB 800MHz

011 = FSB 667MHz

Others = Reserved

0 = DMI x 2

1 = DMI x 4 *

CFG5 (DMI select)

CFG6 Reserved

CFG7 (CPU Strap)

0 = Reserved

1 = Mobile CPU *

CFG8 (Low power PCIE)

0 = Normal mode

1 = Low Power mode *

CFG9

(PCIE Graphics Lane Reversal)

0 = Reverse Lane

1 = Normal Operation *

CFG[11:10] Reserved

CFG[13:12] (XOR/ALLZ)

00 = Reserved

01 = XOR Mode Enabled

For Crestline : 2.4 Kohm

For Calero : 1.5Kohm

10 = All Z Mode Enabled

11 = Normal Operation (Default)*

CFG[15:14] Reserved

CFG16 (FSB Dynamic ODT)

0 = Disable

SB

1

23

4

RN54

SRN10KJ-5-GP

DY

RN54

SRN10KJ-5-GP

DY

12

R106

150R2F-1-GP

R106

150R2F-1-GP

1 2

R325 24D9R2F-L-GPR325 24D9R2F-L-GP

1 2

R101 2K2R2J-2-GP

DY

R101 2K2R2J-2-GP

DY

1

2 3

4

RN60

SRN33J-5-GP-U

RN60

SRN33J-5-GP-U

12

R108

150R2F-1-GP

R108

150R2F-1-GP

1 2

R97 1K3R2D-GPR97 1K3R2D-GP

TP30TP30

12

R103

150R2F-1-GP

R103

150R2F-1-GP

1 2

R321 2K4R2F-GPR321 2K4R2F-GP

12

R105

150R2F-1-GP

R105

150R2F-1-GP

L_BKLT_CTRL

J40

L_BKLT_EN

H39

L_CTRL_CLK

E39

L_CTRL_DATA

E40

L_DDC_CLK

C37

L_DDC_DATA

D35

L_VDD_EN

K40

LVDS_IBG

L41

LVDS_VBG

L43

LVDS_VREFL

N40

LVDS_VREFH

N41

LVDSA_CLK

C45

LVDSB_CLK#

D44

LVDSA_CLK#

D46

LVDSB_CLK

E42

LVDSB_DATA2

A45

LVDSB_DATA1

A47

LVDSB_DATA#2

B45

LVDSB_DATA#1

B47

LVDSB_DATA0

E44

LVDSA_DATA1

E50

LVDSA_DATA#1

E51

LVDSA_DATA2

F48

LVDSA_DATA#2

F49

LVDSB_DATA#0

G44

LVDSA_DATA0

G50

LVDSA_DATA#0

G51

TVA_DAC

E27

TVA_RTN

F27

TVB_DAC

G27

TVB_RTN

J27

TVC_DAC

K27

TVC_RTN

L27

TV_DCONSEL0

M35

TV_DCONSEL1

P33

CRT_RED#

E29

CRT_VSYNC

E33

CRT_TVO_IREF

C32

CRT_RED

F29

CRT_HSYNC

F33

CRT_BLUE#

G32

CRT_DDC_DATA

G35

CRT_BLUE

H32

CRT_GREEN#

J29

CRT_GREEN

K29

CRT_DDC_CLK

K33

PEG_COMPI

N43

PEG_COMPO

M43

PEG_RX#2

N47

PEG_RX1

L50

PEG_RX#1

L51

PEG_RX2

M47

PEG_RX5

T41

PEG_RX#3

T45

PEG_RX4

T49

PEG_RX#4

T50

PEG_RX#5

U40

PEG_RX3

U44

PEG_RX#7

Y40

PEG_RX#6

Y44

PEG_RX9

Y48

PEG_RX8

AB50

PEG_RX#8

AB51

PEG_RX7

W41

PEG_RX6

W45

PEG_RX#9

W49

PEG_RX11

AC41

PEG_RX10

AC45

PEG_RX#11

AD40

PEG_RX#10

AD44

PEG_RX#15

AG41

PEG_RX15

AG42

PEG_RX#14

AG45

PEG_RX#12

AG46

PEG_RX13

AG49

PEG_RX0

J50

PEG_RX#0

J51

PEG_RX14

AH45

PEG_RX12

AH47

PEG_RX#13

AH49

PEG_TX#6

Y43

PEG_TX#8

W38

PEG_TX#7

W46

PEG_TX#12

AC42

PEG_TX#10

AC46

PEG_TX#11

AC49

PEG_TX#9

AD39

PEG_TX#14

AE49

PEG_TX#13

AH39

PEG_TX#15

AH44

PEG_TX#0

N45

PEG_TX#3

N51

PEG_TX#4

R50

PEG_TX#5

T42

PEG_TX#1

U39

PEG_TX#2

U47

PEG_TX8

Y39

PEG_TX7

Y47

PEG_TX6

W42

PEG_TX9

AC38

PEG_TX11

AC50

PEG_TX12

AD43

PEG_TX10

AD47

PEG_TX14

AE50

PEG_TX13

AG39

PEG_TX15

AH43

PEG_TX3

N50

PEG_TX0

M45

PEG_TX4

R51

PEG_TX1

T38

PEG_TX2

T46

PEG_TX5

U43

3 OF 10

LVDS

TV VGA

PCI_EXPRESS GRAPHICS

U16C

3 OF 10

LVDS

TV VGA

PCI_EXPRESS GRAPHICS

U16C

12

R109

150R2F-1-GP

R109

150R2F-1-GP

12

R110

150R2F-1-GP

R110

150R2F-1-GP