JEDEC Standard No. 209-4B

Page 13

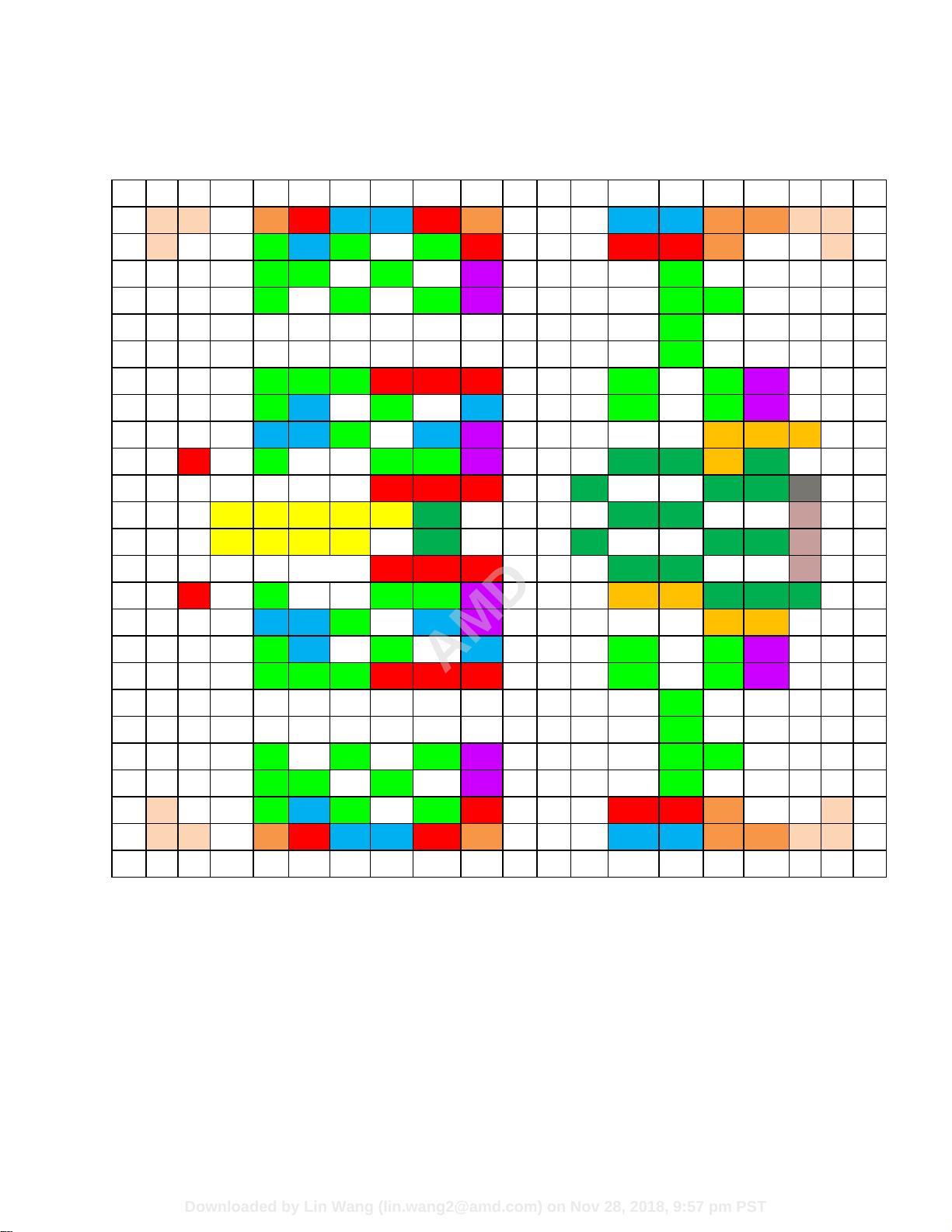

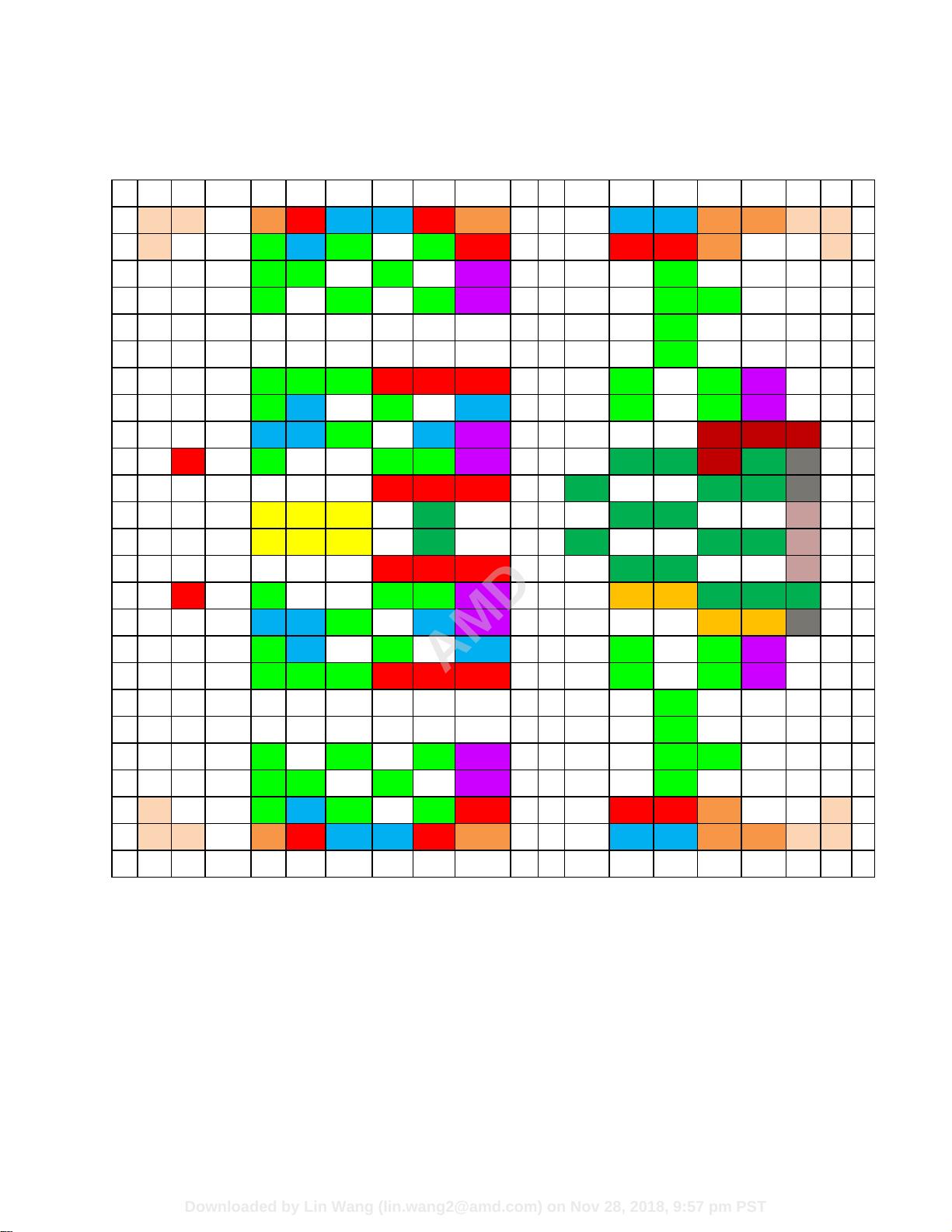

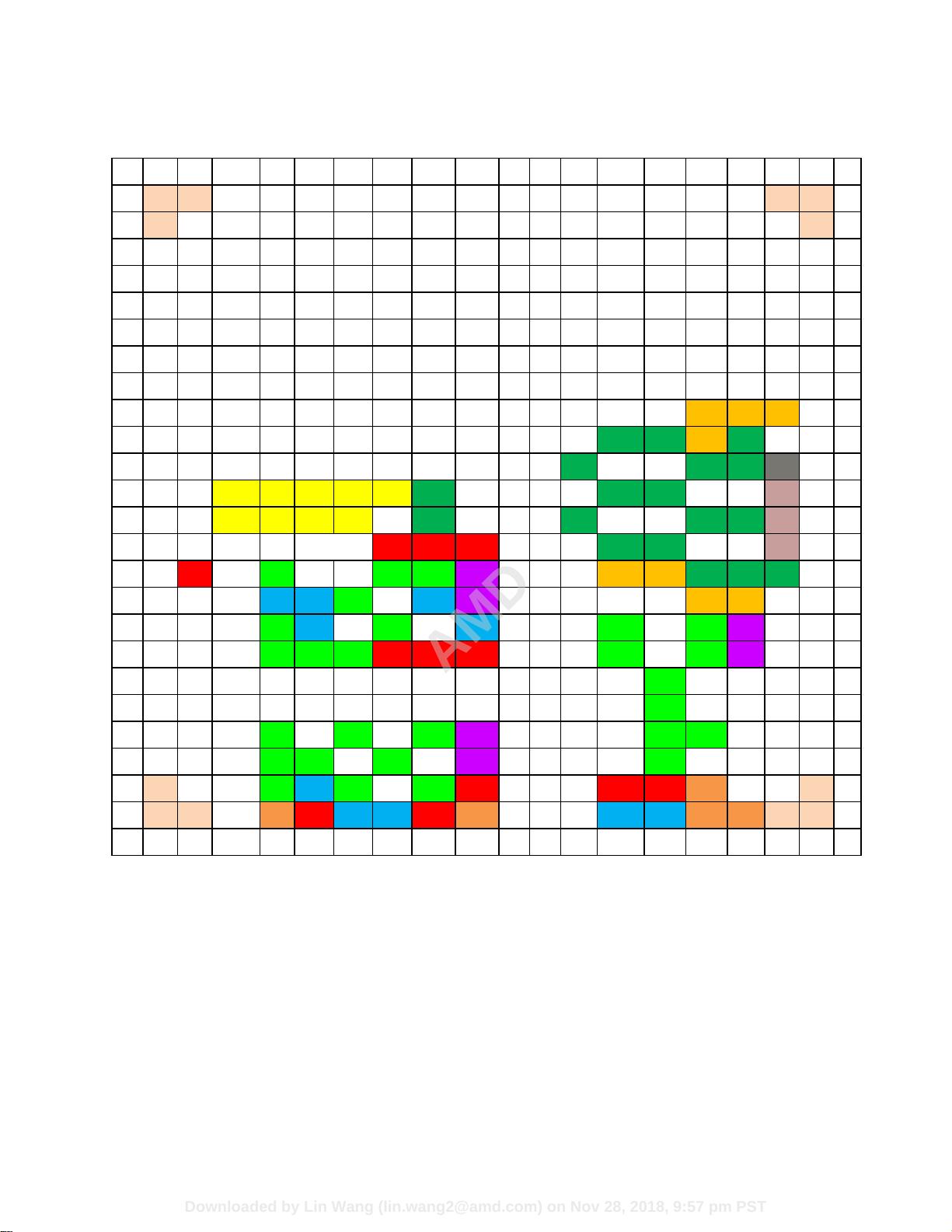

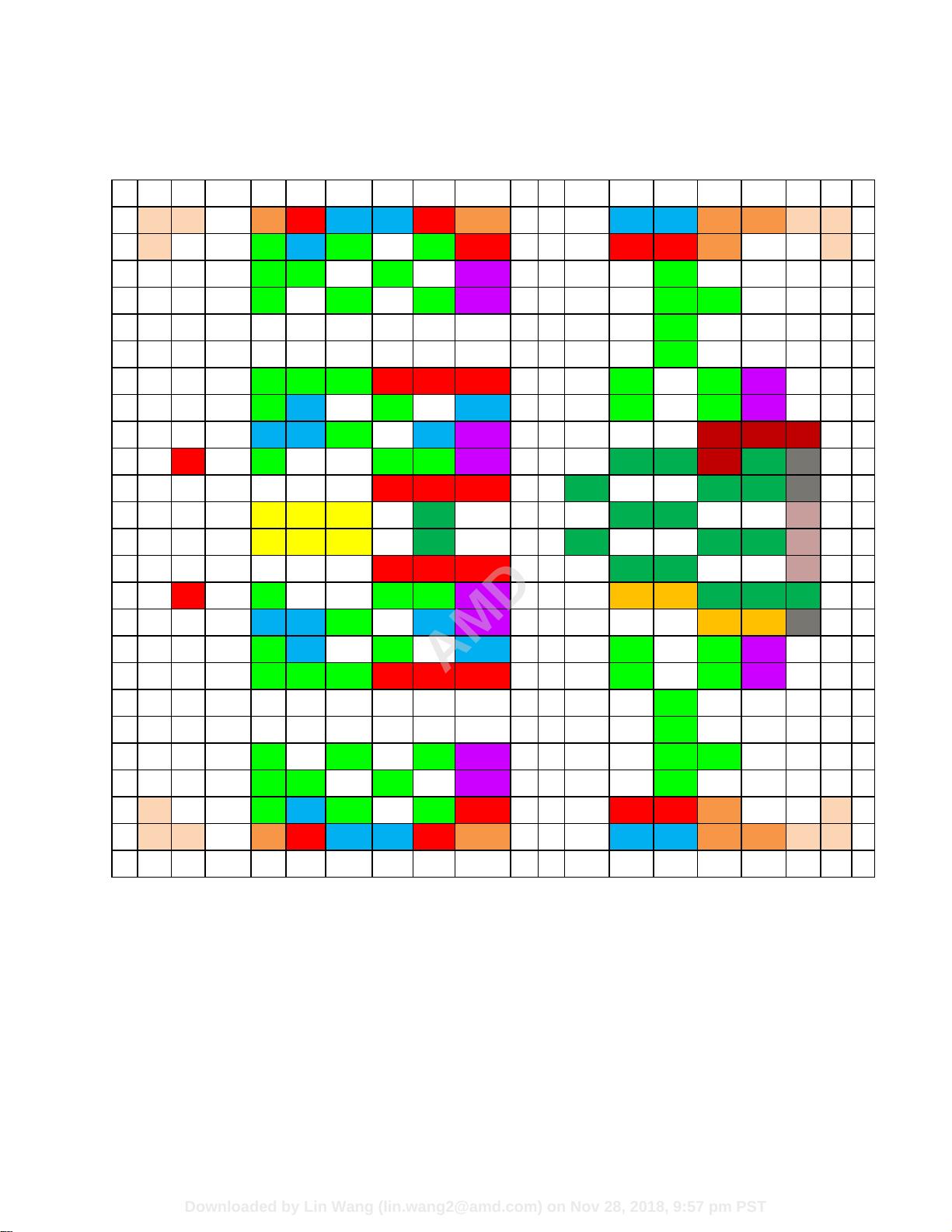

2.2.10 254 ball UFS MCP Two-Channel FBGA (top view) using MO-276

NOTE 1 0.5 mm pitch, 24 rows.

NOTE 2 Top View, A1 in top left corner.

NOTE 3 ODT(ca)_[x] balls are wired to ODT(ca)_[x] pads of Rank 0 DRAM die. ODT(ca)_[x] pads for other ranks (if

present) are disabled in the package.

NOTE 4 ZQ2, CKE2_A, CKE2_B, CS2_A, and CS2_B balls are reserved for 3 rank package, and for 1 rank and 2

rank package those balls are NC.

NOTE 5 DRAM die pad VSS and VSSQ signals are combined to VSS package balls.

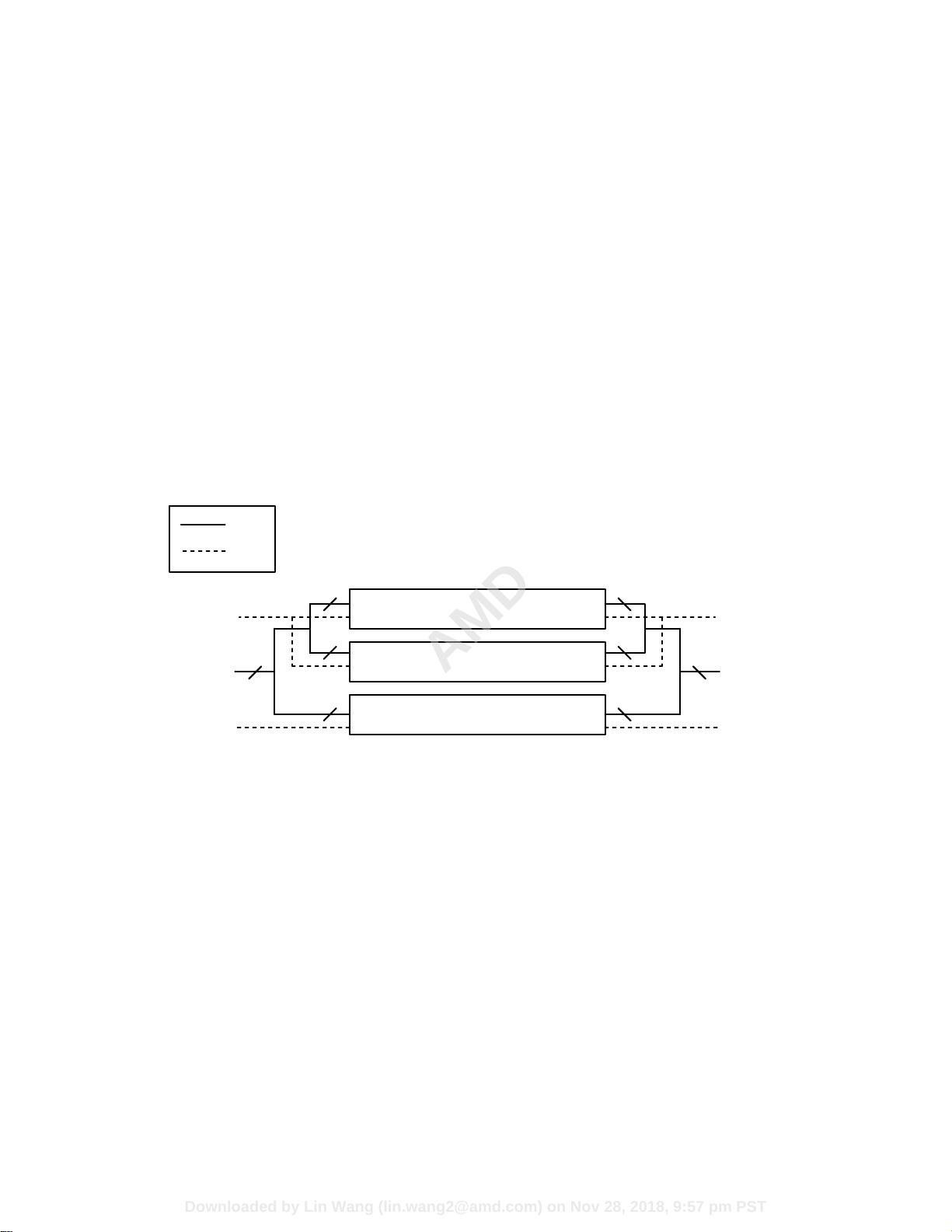

NOTE 6 Package requires dual channel die or functional equivalent of single channel die-stack.

NOTE 7 Vendor specific function (VSF) - this terminal should not have any external electrical connections, but it may

have an internal connection. The terminal may be routed to provide accessibility and may be used for general purpose

vendor specific operations.

12 3 45 6 7 8 9101112131415161718

A

DNU DNU DQ0_A VDD1 VDD2 VDDQ VDDQ VDD2 VDD1 VDDQ VDDQ VDD1 VDD1 DNU DNU

A

B DNU DQ1_A VSS VDDQ VSS DQ4_A VSS VDD2 VDD2 VDD2 VDD1 ZQ0 DNU

B

CDQ2_AVSS VSS DQ5_A VSS DQ7_A DQS0_t_A CA2_A VSS CA5_A ZQ1

C

DDQ3_AVSS DMI0_A VSS DQ6_A VSS DQS0_c_A CA3_A VSS VSS ZQ2

D

E CA4_A VSS CS0_A CKE0_A

E

F CA1_A VSS CS1_A CKE1_A

F

GDQ13_AVSS VSS VSS VDD2 VDD2 VDD2 VSS CA0_A VSS CLK_c_A

G

H DMI1_A VSS VDDQ DQ14_A VSS DQ15_A VDDQ VSS CS2_A VSS CLK_t_A

H

JDQ11_AVDDQ VDDQ VSS DQ12_A VDDQ DQS1_c_A

ODT(ca)_

A

CKE2_A VCCQ2 VCCQ2 VCCQ2

J

K VDD2 DQ10_A VSS DQ8_A DQ9_A VSS VSS DQS1_t_A VSSm VSSm VCCQ2 VSSm

VDDIQ

2

K

L VDD2 VDD2 VDD2 VSSm DIN1_c DIN1_t VSSm VSSm VDDI

L

MNCVSF1 VSF3 VSF5 RFU VSSm RFU RST_n VSSm VSSm DIN0_c DIN0_t VCC

M

NNCVSF2 VSF4 VSF6 RFU VSSm RFU VSSm DOUT1_c DOUT1_t VSSm VSSm VCC

N

P VDD2 VDD2 VDD2 REF_CLK VSSm VSSm DOUT0_c DOUT0_t VCC

P

R VDD2 DQ10_B VSS DQ8_B DQ9_B VSS VSS DQS1_t_B VCCQ VCCQ VSSm VSSm VSSm

R

TDQ11_BVDDQ VDDQ VSS DQ12_B VDDQ DQS1_c_B

ODT(ca)_

B

CKE2_B VCCQ VCCQ VDDIQ

T

U DMI1_B VSS VDDQ DQ14_B VSS DQ15_B VDDQ VSS CS2_B VSS CLK_t_B

U

VDQ13_BVSS VSS VSS VDD2 VDD2 VDD2 VSS CA0_B VSS CLK_c_B

V

W CA1_B VSS CS1_B CKE1_B

W

Y CA4_B VSS CS0_B CKE0_B

Y

AA DQ3_B VSS DMI0_B VSS DQ6_B VSS DQS0_c_B CA3_B VSS VSS RESET_n

AA

AB DQ2_B

VSS VSS DQ5_B VSS DQ7_B DQS0_t_B CA2_B VSS CA5_B NC

AB

AC

DNU DQ1_B VSS VDDQ VSS DQ4_B VSS VDD2 VDD2 VDD2 VDD1 NC DNU

AC

AD

DNU DNU DQ0_B VDD1 VDD2 VDDQ VDDQ VDD2 VDD1 VDDQ VDDQ VDD1 VDD1 DNU DNU

AD

12 3 45 6 7 8 9101112131415161718

Downloaded by Lin Wang (lin.wang2@amd.com) on Nov 28, 2018, 9:57 pm PST

AMD