CPLD实现的数据选择模块——计算机硬件课程设计

需积分: 9 160 浏览量

更新于2024-07-12

收藏 3.31MB PPT 举报

这篇资源主要介绍了如何在计算机硬件课程设计中使用CPLD(复杂可编程逻辑器件)实现数据选择模块。该设计涉及到多个输入和输出引脚,通过控制OE1和OE2信号来选择不同的数据输入(I0-I3),并将选定的数据输出到OD。在CPLD中,设计通常使用ABEL语言编写,并通过ispEXPERT软件进行调试和生成JEDEC文件,以便于下载到CPLD中。

设计步骤包括:

1. 使用ABEL语言或原理图按照题目要求完成设计。

2. 在ispEXPERT中调试设计并生成JEDEC文件。

3. 检查下载电缆连接,确保正确无误。

4. 在TDN-CM++电路板上根据电路图组装硬件。

5. 检验设计结果,验证是否满足设计目标。

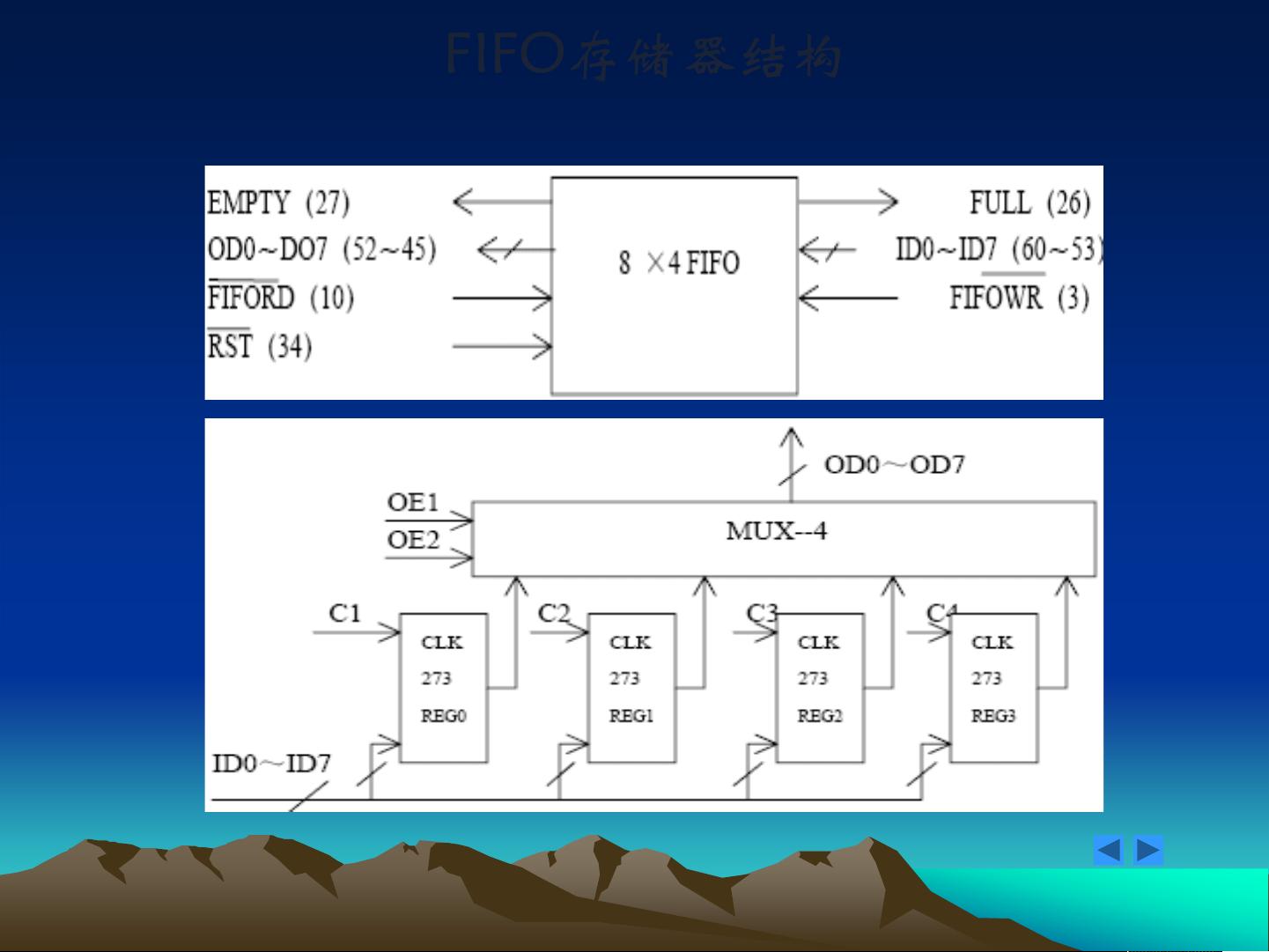

设计题目包括运算器ALU、FIFO存储器以及几种模型机的设计,如RISC、流水线、重叠和超标量模型机。其中,ALU设计需要实现至少8种运算功能,可以参考74LS181的功能表,用ABEL语言描述并进行下载验证。FIFO存储器设计要求实现8x8大小,具备满、空标志,以及读写控制信号。

相关知识包括ABEL语言简介、ispEXPERT软件的使用方法,以及CPLD1032和1048的基础知识。在实验过程中,学生需要注意遵守实验室规定,保持良好的考勤记录,设计报告应包含设计目的、内容、原理、结果分析和自我评价。

在注意事项方面,每个学生需要有自己的设备,项目文件应存放在D盘。同时,课程成绩由上机调试、设计报告和考勤三部分组成。对于FIFO存储器,其内部结构包括控制信号模块、寄存器模块和数据选择器模块,每个模块都需要用ABEL语言设计,并确保正确实现数据的读写以及状态标志的控制。

这篇资源详细阐述了使用CPLD进行数据选择模块设计的过程,涉及了硬件设计的基本流程、工具使用、设计规范以及相关硬件组件的理解和应用,对于学习计算机硬件和CPLD设计的学生来说具有很高的参考价值。

2013-04-26 上传

2010-06-10 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-07-07 上传

2023-11-12 上传

清风杏田家居

- 粉丝: 21

- 资源: 2万+

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案