基于CORDIC的数字下变频器ASIC坐标变换模块设计

14 浏览量

更新于2024-08-31

收藏 301KB PDF 举报

在数字信号处理(DSP)领域中,数字下变频器(Digital Down Converter, DDC)是实现无线通信系统中频信号处理的关键组件。在超外差式接收机的设计中,下变频是一种重要的信号处理技术,通过它,可以将高频率的射频信号降至较低的中频,便于后续的信号处理和数字化。下变频过程可以分为模拟下变频和数字下变频两阶段,最终目标是将信号转换成便于解调的基带信号。

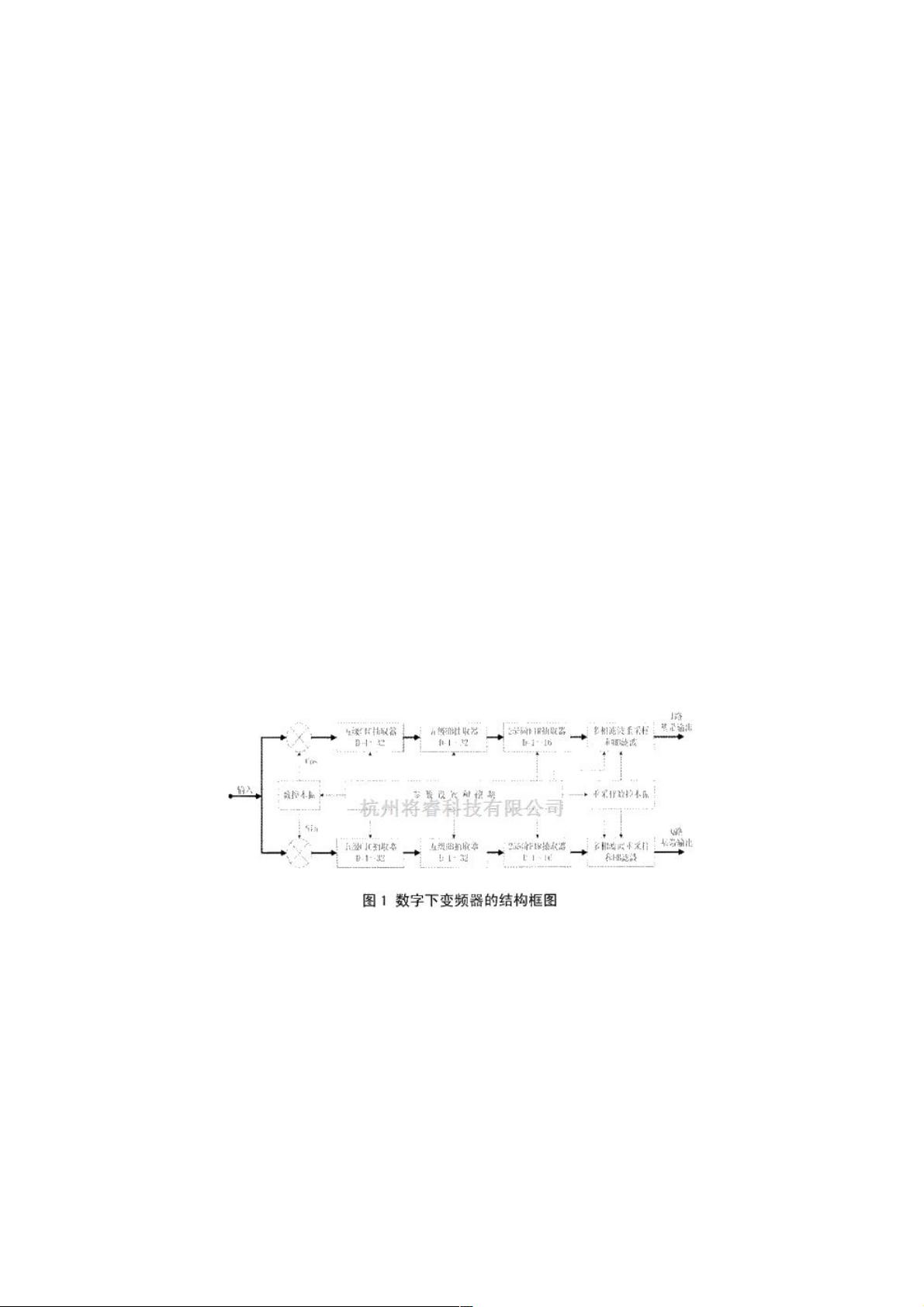

数字下变频器的核心结构通常包括两个主要模块:NCO(Numerical Control Oscillator,数字控制振荡器)混频模块和抽取滤波模块。NCO模块的作用是生成正余弦波,通过与输入数据进行复数乘法,实现了混频过程,这是模拟信号与数字信号之间的桥梁。抽取滤波模块则负责进一步细化信号,如采用CIC(积分梳状抽取滤波器)或HBF(半带滤波器)级联,以减少噪声和失真。对于宽信号带宽且抽取倍数适中的情况,FIR滤波器也可以作为选择;而在高速数据处理场景,多相滤波的下变频方案能降低对处理器性能的要求。

在ASIC(Application-Specific Integrated Circuit,专用集成电路)的应用中,数字下变频器的坐标变换模块尤其引人关注。由于ASIC是针对特定应用设计的集成电路,它能够优化芯片的性能,如减小体积、降低功耗、提高可靠性、增强保密性和降低成本。本文着重探讨的是基于CORDIC算法的数字下变频器中的坐标变换模块,这一部分实现了从直角坐标系到极坐标系的转换,这对于信号处理精度至关重要,尤其是在极化天线和多径衰落环境下,高效的坐标变换能有效改善信号质量。

因此,数字下变频器的ASIC实现不仅涉及硬件设计的效率和灵活性,还涉及到算法选择和优化,如CORDIC算法的应用,以适应各种不同的应用场景和性能需求。这些设计决策直接影响到整个接收系统的性能指标,包括信号捕获能力、抗干扰能力以及系统功耗等,是现代无线通信系统设计中的关键技术挑战。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-02-22 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2024-12-28 上传

2024-12-28 上传

weixin_38743372

- 粉丝: 5

- 资源: 920

最新资源

- ConcurrentStudy:Java并发编程和netty中学习加强相关代码

- 与一只巨大的鸡战斗至死:一场史诗般的最终幻想风格的战斗,对抗具有动态界面的 AI 控制的鸡:P-matlab开发

- Parstagram

- dsc字符串实验室在线ds-pt-090919

- UMLS-explorer

- txline,微带线计算工具

- OPPOR9S OPPOR9Splus原厂维修图纸电路图PCB位件图资料.zip

- stocks-chaser-frontend:库存跟踪应用

- 通过非线性导数进行边缘检测:这个简短的演示展示了一种有效的边缘检测算法。-matlab开发

- mariebeigelman.github.io

- AnoClient

- 开发基于JSP Servlet JavaBean的网上交易系统(JSP Servlet JavaBean Web Service

- Weather Forecast-crx插件

- go-jsonrpc-websocket.rar

- AM调制和解调研究:这个演示有助于研究和分析AM MOD和DEMOD。-matlab开发

- gocloud-secrets-awssecretsmanager