VHDL实现专用串行通信芯片设计——同步收发器

136 浏览量

更新于2024-08-28

收藏 434KB PDF 举报

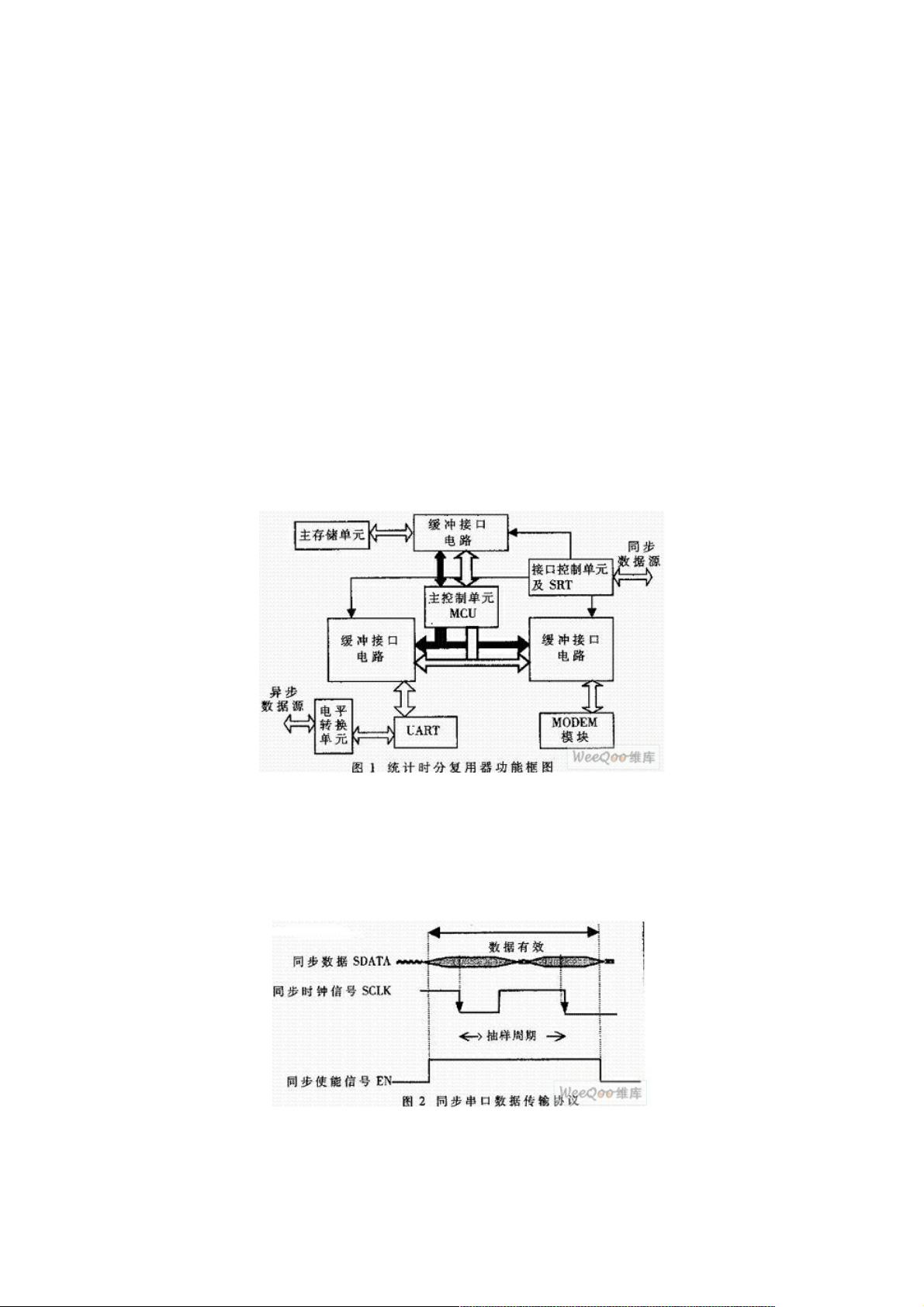

"本文介绍了如何使用VHDL设计专用串行通信芯片,特别是在同步传输协议需求下,如何利用现代可编程ASIC技术,如FPGA和CPLD,来替代传统逻辑元器件,提高设计效率和系统稳定性。文章通过实例展示了在统计时分复用器系统中设计专用SRT(同步收发器)的过程,并详细分析了SRT的模块组成和功能。"

在通信领域,通信芯片扮演着至关重要的角色,它们负责OSI模型物理层的数据发送与接收,并能依据不同的传输方式和协议执行数据校验和组帧。通常,市场上的串行通信芯片分为同步和异步两种类型,异步芯片多与INTEL的8250兼容,而同步芯片则需支持特定的协议,如BSC、HDLC、SDLC等。以往,设计专用的同步收发器往往依赖于传统的逻辑元件,这种方法可能导致设计周期长、系统稳定性差。

随着FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)的发展,现在可以通过电子设计自动化(EDA)工具,根据具体需求定制通信芯片。以统计时分复用器为例,这种设备能够复接7路异步数据和1路同步数据。为了降低成本和功耗,设计者可以选择将专用SRT和接口控制单元整合到单片CPLD中。

在CPLD内部,SRT的主要功能模块包括接口控制单元和SRT本身。SRT设计借鉴了与INTEL 8250兼容的UART,以简化主控单元的编程。这样做可以统一访问外部通信芯片的操作流程,使系统更易维护。SRT的结构通常包括数据缓冲区、波特率发生器、帧同步电路、数据校验模块以及控制逻辑等组成部分。

数据缓冲区用于暂存待发送或接收的数据,波特率发生器则根据设定的速率产生时钟信号,控制数据的传输速度。帧同步电路确保数据帧的正确发送和接收,而数据校验模块则执行如CRC(循环冗余校验)等算法,检测数据传输过程中可能出现的错误。控制逻辑协调这些模块的工作,响应来自主控单元的命令,处理各种通信状态。

设计这样一个专用SRT,工程师需要深入理解VHDL语言,用其描述各个模块的功能和相互间的交互。VHDL是一种硬件描述语言,它允许开发者以接近于自然语言的方式定义硬件结构和行为。通过综合工具,VHDL代码可以转换成门级网表,进而编程到FPGA或CPLD中,实现硬件功能。

使用VHDL设计专用串行通信芯片能够显著提升设计灵活性和系统性能,缩短开发周期,并确保设计满足特定的通信协议需求。这种技术的应用对于现代通信系统,尤其是那些需要定制化解决方案的场合,具有极大的价值。

107 浏览量

131 浏览量

107 浏览量

点击了解资源详情

131 浏览量

2021-07-26 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38723192

- 粉丝: 8

- 资源: 870