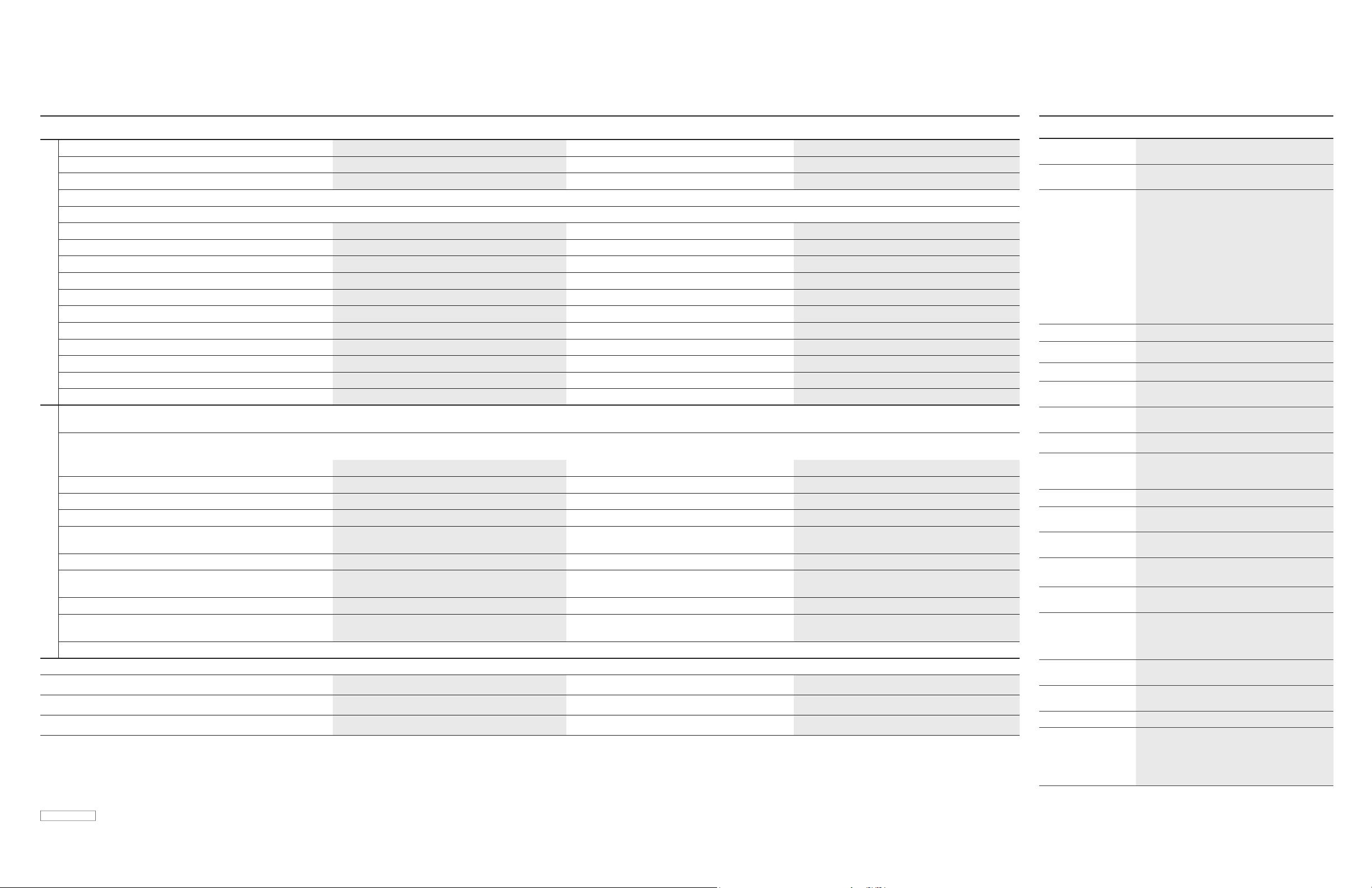

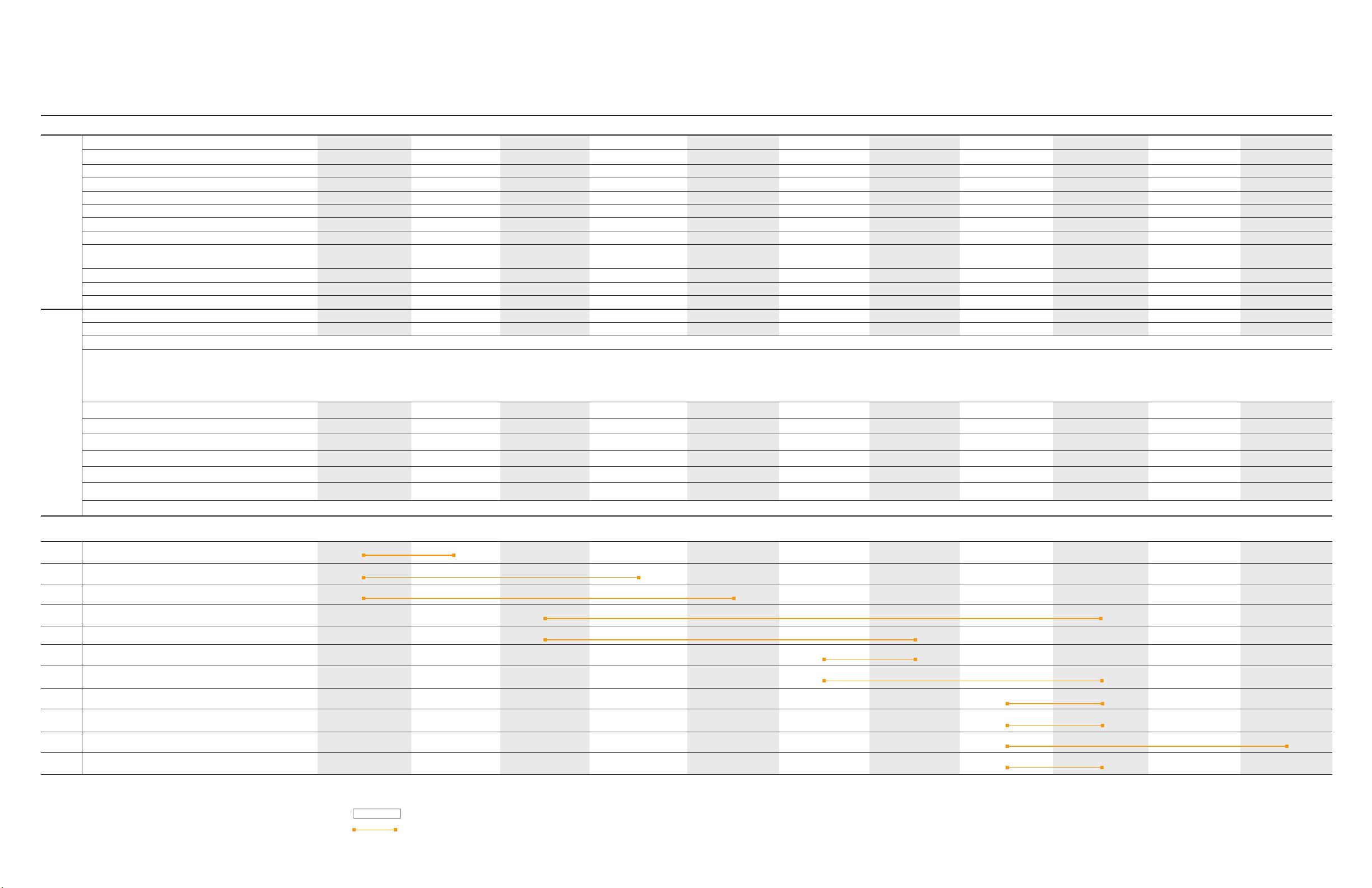

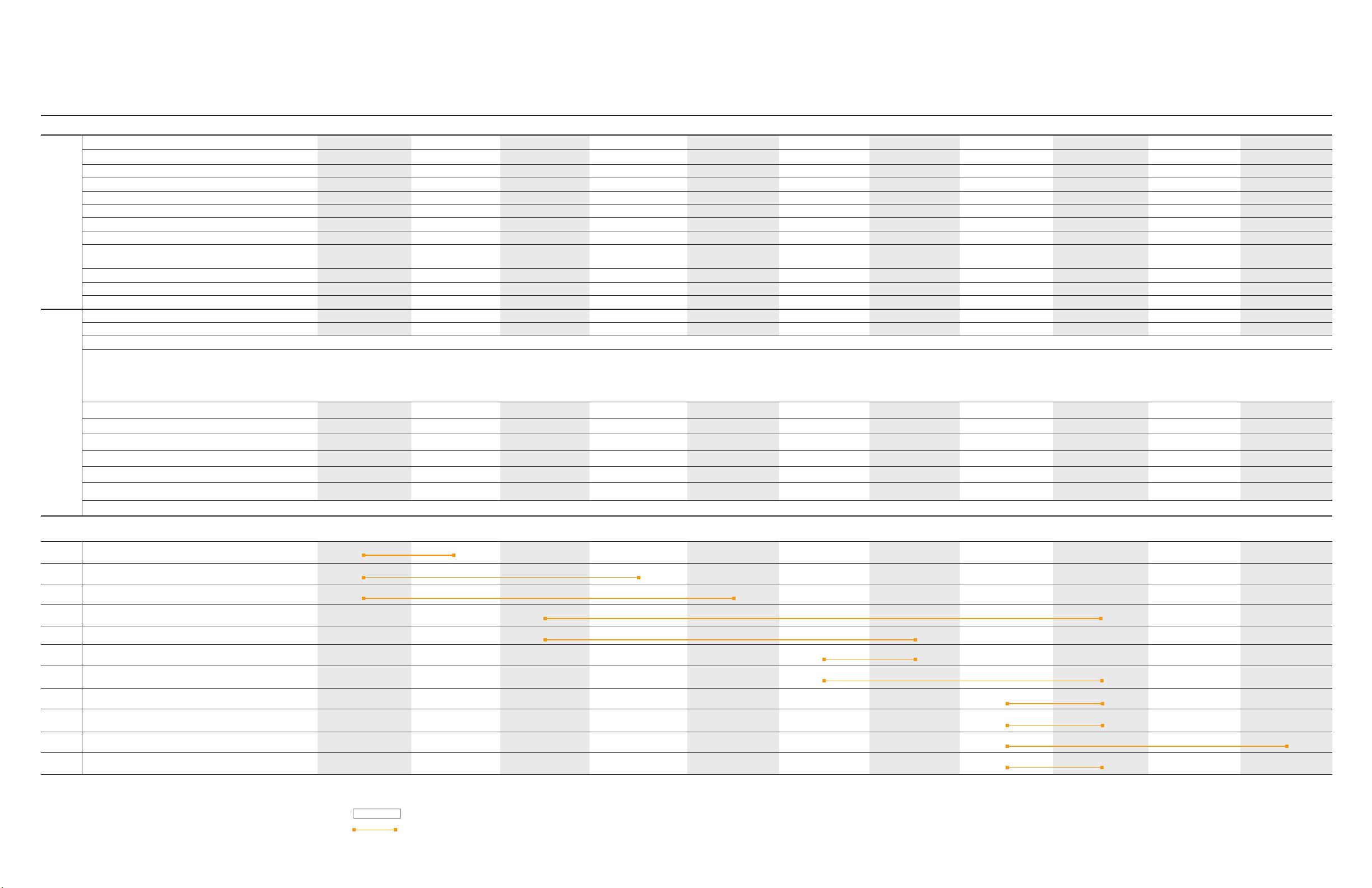

INTEL ArrIA 10 FPGA FEATurEs

•

PRODUCT LINE GX 160 GX 220 GX 270 GX 320 GX 480 GX 570 GX 660 GX 900 GX 1150 GT 900 GT 1150

Resources

Part number reference 10AX016 10AX022 10AX027 10AX032 10AX048 10AX057 10AX066 10AX090 10AX115 10AT090 10AT115

LEs (K) 160 220 270 320 480 570 660 900 1,150 900 1,150

System logic elements (K) 210 288 354 419 629 747 865 1,180 1,506 1,180 1,506

Adaptive logic modules (ALMs) 61,510 83,730 101,620 118,730 181,790 217,080 250,540 339,620 427,200 339,620 427,200

Registers 246,040 334,920 406,480 474,920 727,160 868,320 1,002,160 1,358,480 1,708,800 1,358,480 1,708,800

M20K memory blocks 440 588 750 891 1,438 1,800 2,133 2,423 2,713 2,423 2,713

M20K memory (Mb) 9 11 15 17 28 35 42 47 53 47 53

MLAB memory (Mb) 1.0 1.8 2.4 2.8 4.3 5.0 5.7 9.2 12.7 9.2 12.7

Hardened single-precision oating-point multiplers/

adders

156/156 191/191 830/830 985/985 1,368/1,368 1,523/1,523 1,688/1,688 1,518/1,518 1,518/1,518 1,518/1,518 1,518/1,518

18 x 19 multipliers 312 382 1,660 1,970 2,736 3,046 3,376 3,036 3,036 3,036 3,036

Peak xed-point performance (GMACS)

1

343 420 1,826 2,167 3,010 3,351 3,714 3,340 3,340 3,340 3,340

Peak oating-point performance (GFLOPS) 140 172 747 887 1,231 1,371 1,519 1,366 1,366 1,366 1,366

Clocks, Maximum I/O Pins, and

Architectural Features

Global clock networks 32 32 32 32 32 32 32 32 32 32 32

Regional clocks 8 8 8 8 8 8 16 16 16 16 16

I/O voltage levels supported (V) 1.2, 1.25, 1.35, 1.8, 2.5, 3.0

I/O standards supported

3 V I/O pins only: 3 V LVTTL, 2.5 V CMOS

Maximum LVDS channels (1.6 G) 120 120 168 168 222 324 270 384 384 312 312

Maximum user I/O pins 288 288 384 384 492 696 696 768 768 624 624

Transceiver count (17.4 Gbps) 12 12 24 24 36 48 48 96 96 72 72

Transceiver count (25.78 Gbps) – – – – – – – – – 6 6

PCI Express hardened IP blocks (Gen3 x8) 1 1 2 2 2 2 2 4 4 4 4

Maximum 3 V I/O pins 48 48 48 48 48 48 48 – – – –

Memory devices supported DDR4, DDR3, DDR2, QDR IV, QDR II+, QDR II+ Xtreme, LPDDR3, LPDDR2, RLDRAM 3, RLDRAM II, LLDRAM II, HMC

Package Options

2

and I/O Pins

3

: General-Purpose I/O (GPIO) Count, High-Voltage I/O Count, LVDS Pairs

4

, and Transceiver Count

U19 U484 pin (19 mm)

192, 48, 72, 6 192, 48, 72,6 – – – – – – – – –

F27 F672 pin (27 mm)

240, 48, 96, 12 240, 48, 96, 12 240, 48, 96, 12 240, 48, 96, 12 – – – – – – –

F29 F780 pin (29 mm)

288, 48, 120, 12 288, 48, 120, 12 360, 48, 156, 12 360, 48, 156, 12 360, 48, 156, 12 – – – – – –

F34 F1152 pin (35 mm)

– – 384, 48, 168, 24 384, 48, 168, 24 492, 48, 222, 24 492, 48, 222, 24 492, 48, 222, 24 504, 0, 252, 24 504, 0, 252, 24 – –

F35 F1152 pin (35 mm)

– – 384, 48, 168, 24 384, 48, 168, 24 396, 48, 174, 36 396, 48, 174, 36 396, 48, 174, 36 – – – –

KF40 F1517 pin (40 mm)

– – – – – 696, 96, 324, 36 696, 96, 324, 36

– – – –

NF40 F1517 pin (40 mm)

– – – – – 588, 48, 270, 48 588, 48, 270, 48 600, 0, 300, 48 600, 0, 300, 48 – –

RF40 F1517 pin (40 mm)

– – – – – – – 342, 0, 154, 66 342, 0, 154, 66 – –

NF45 F1932 pin (45 mm)

– – – – – – – 768, 0, 384, 48 768, 0, 384, 48 – –

SF45 F1932 pin (45 mm)

– – – – – – – 624, 0, 312, 72 624, 0, 312, 72 624, 0, 312, 72 624, 0, 312, 72

UF45 F1932 pin (45 mm)

– – – – – – – 480, 0, 240, 96 480, 0, 240, 96 – –

192, 48, 72, 6

All I/Os: 1.8 V CMOS, 1.5 V CMOS, 1.2 V CMOS, SSTL-135, SSTL-125,

Dierential SSTL-18 (I and II), Dierential SSTL-15 (I and II),

Numbers indicate GPIO count, high-voltage I/O count, LVDS pairs, and

transceiver count.

Indicates pin migration.

POD12, POD10, Dierential POD12, Dierential POD10, LVDS, RSDS, mini-LVDS, LVPECL

DDR and LVDS I/O pins:

SSTL-18 (1 and II), SSTL-15 (I and II), SSTL-12, HSTL-18 (I and II), HSTL-15 (I and II), HSTL-12 (I and II), HSUL-12, Dierential SSTL-135, Dierential SSTL-125,

Dierential SSTL-12, Dierential HSTL-18 (I and II), Dierential HSTL-15 (I and II), Dierential HSTL-12 (I and II), Dierential HSUL-12

6. All data is correct at the time of printing, and may be subject to change without prior notice.

For the latest information, please visit www.intel.com/fpga.

Notes:

1. Fixed-point performance assumes the use of pre-adders.

2. All packages are ball grid arrays with 1.0 mm pitch, except for U19 (U484), which is 0.8 mm pitch.

3. A subset of pins for each package are used for 3.3 V and 2.5 V interfaces.

4. Each LVDS pair can be congured as either a dierential input or a dierential output.

5. Certain packages might not bond out all PCI Express hard IP blocks.

View device ordering codes on page 52.

Intel FPGA Product Catalog

Devices: Generation 10 Device Portfolio

2221

Devices: Generation 10 Device Portfolio

Intel FPGA Product Catalog