FPGA实现的移位寄存器流水线FFT处理器

60 浏览量

更新于2024-09-05

收藏 1.02MB PDF 举报

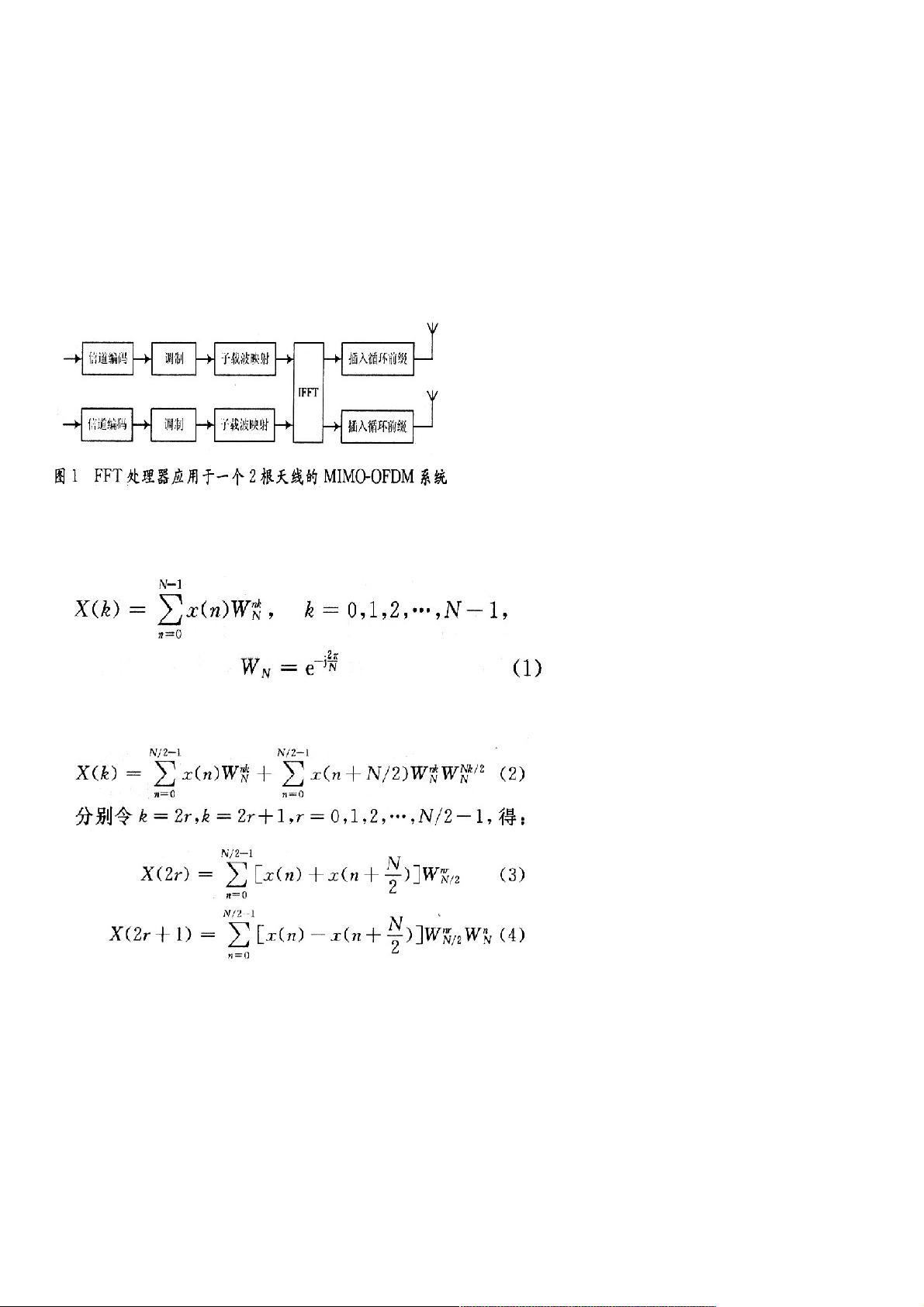

"基于FPGA的移位寄存器流水线结构FFT处理器的实现,用于高效执行快速傅里叶变换,适用于雷达、通信和电子对抗等领域的应用。该设计利用FPGA的并行处理能力,采用基-2的频域抽取DIF算法,通过移位寄存器流水线结构实现高频率、高效率的运算。"

本文探讨了基于FPGA的FFT处理器设计,特别是在现代雷达、通信和电子对抗系统中,快速傅里叶变换(FFT)的重要性不言而喻。随着FPGA技术的迅速进步,它在处理速度和并行性方面相比于数字信号处理器(DSP)具有显著优势,特别适合于实时信号处理任务。

在FFT处理中,DIT(时域抽取)和DIF(频域抽取)是两种主要算法。本文选择了DIF算法,这是一种基-2的方法,它通过将输入序列按奇偶分组,逐步分解为更小的DFT,减少了计算复杂性。DIF算法的输入顺序是正序,而输出是倒序的,这简化了地址控制,并且为使用移位寄存器作为存储结构提供了可能。

移位寄存器流水线结构是本文的核心创新点。在传统结构中,所有数据需先加载到寄存器中才能开始运算。但在DIF算法基础上,仅需前半部分数据就可以开始计算。通过移位寄存器,数据在运算过程中不断移动,使得新的数据能够及时补充进来,保持了数据流的连续性。这种方法的最大工作频率可达500MHz,远超传统的RAM方式。

为了解决移位寄存器中可能出现的空白位,设计中采用了类似“乒乓操作”的机制,两路数据交替补充到移位寄存器,保证了运算的连续性和效率。值得注意的是,与传统的“乒乓操作”不同,这里的实现不需要两块RAM,减少了硬件资源的占用。

图2展示了256点FFT处理器的第一级结构,图3则进一步解释了8点结构的工作原理,数据通过输入选择控制进入各级,逐级进行处理,各级所需的移位寄存器数量递减,优化了资源利用率。

这个基于FPGA的移位寄存器流水线结构FFT处理器实现了高效的FFT运算,优化了硬件资源,提高了运算速度,尤其适合对实时性和处理能力有严格要求的领域。这样的设计不仅提升了系统性能,还降低了成本,展示了FPGA在信号处理领域的强大潜力。

2020-08-07 上传

2023-10-22 上传

2023-08-25 上传

2024-01-04 上传

2024-10-24 上传

2023-08-06 上传

2023-05-12 上传

weixin_38622849

- 粉丝: 3

- 资源: 958

最新资源

- MCP C#试用试题

- nutch初学入门 非常好的入门教程

- c#面试题 网络转载 不错 经典

- C#设计模式大全 好书

- Struts+Spring+Hibernate整合教程.pdf

- BP神经网络原理及仿真实例

- 使用简介POWERPLAY

- Oracle 9i10g编程艺术

- scm手把手开发文档

- Cognos Impromptu

- LoadRunner安装手册.pdf

- cognos 部署 文档

- 用C语言进行单片机程序设计与应用

- Direct3D.ShaderX.-.Vertex.and.Pixel.Shader.Tips.and.Tricks.pdf

- 《uVision2入门教程》.pdf

- spring1.2申明式事务.txt