电子科技大学通信学院数字后端设计流程详解

需积分: 32 52 浏览量

更新于2024-07-20

4

收藏 964KB PPT 举报

"数字后端流程与工具 - 电子科技大学通信学院111教研室"

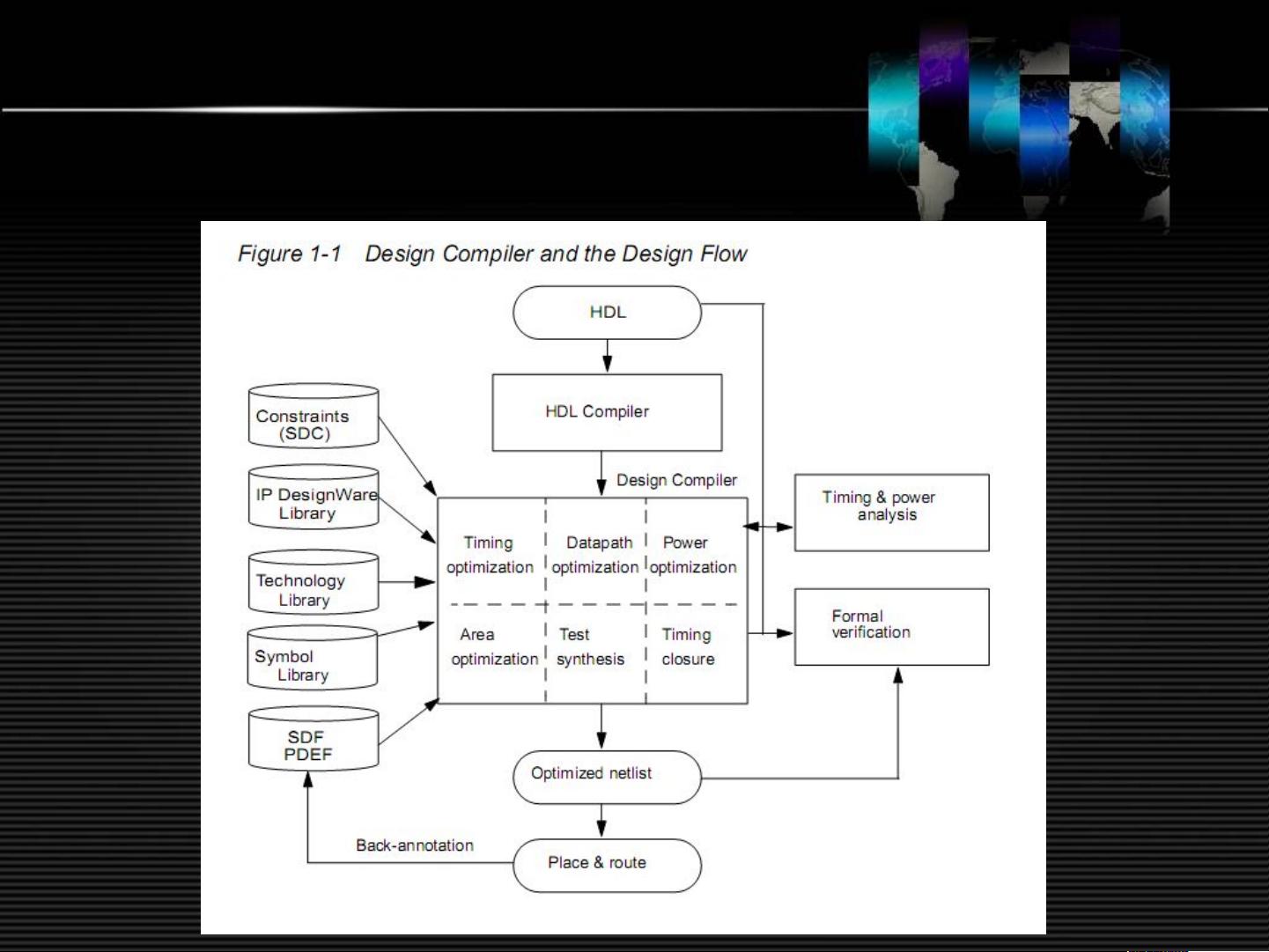

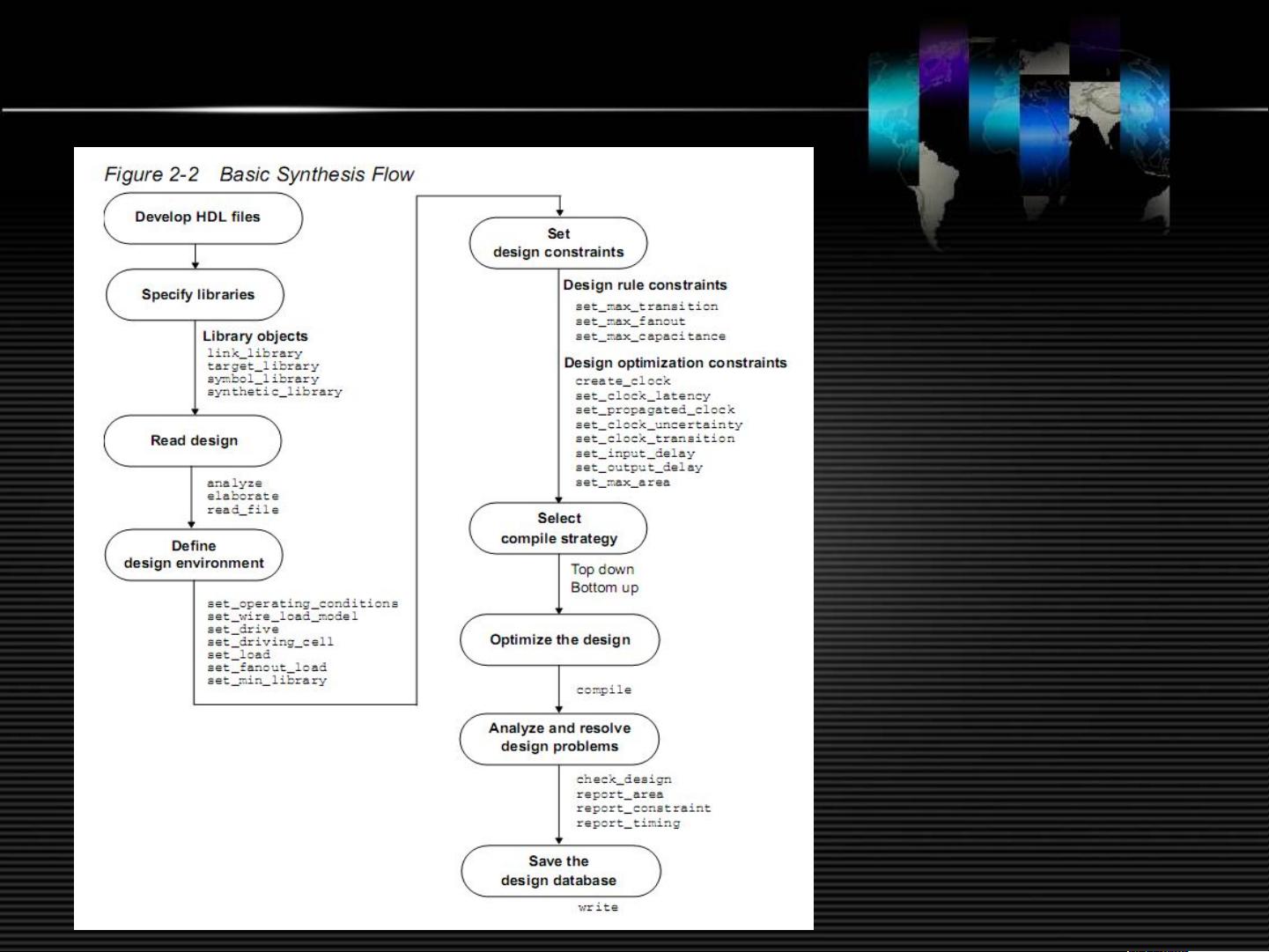

本文将详细介绍数字后端流程与工具在集成电路设计中的应用,特别关注基于标准单元的ASIC(Application-Specific Integrated Circuit)设计流程。该流程分为数字前端设计和数字后端设计两个主要阶段,旨在生成可用于制造的GDS2文件。

**数字前端设计(front-end)**

前端设计始于高层次的算法模型,通常用C、MATLAB或类似语言编写。接着,设计者会用硬件描述语言(HDL),如VHDL或Verilog,将算法转换为RTL(Register Transfer Level)代码。这个阶段的目标是创建一个能描述系统行为的逻辑模型。然后,综合工具会根据基本单元库(standard cell library)的功能和时序模型,将RTL代码翻译成门级网表(NETLIST)。在这个过程中,设计师需要进行形式验证,确保RTL代码的逻辑正确性。

**静态时序分析(Static Timing Analysis, STA)**

在前端设计中,静态时序分析是至关重要的一步,用于评估设计的时序性能。如果设计不能满足速度要求,可能需要返回到RTL代码并进行优化。此外,前端设计还包括功耗和面积的预估,这些都是设计迭代的重要考量因素。

**数字后端设计(back-end)**

数字后端设计阶段开始于前端生成的网表,其目标是布局布线,生成可送至芯片代工厂(foundry)进行流片的GDS2文件。布局布线工具根据基本单元库的时序和几何模型,将电路单元在硅片上进行合理分布和连接,同时优化性能、功耗和面积。这个过程涉及多轮迭代,以满足时序、电气规则、物理尺寸等约束。

**布局与布线(Placement & Routing, P&R)**

布局阶段决定每个电路模块的位置,而布线阶段则负责连接这些模块,确保信号传输的正确性和时序要求。在这一过程中,可能会进行时序驱动的布线优化,以提高整体设计性能。

**后处理与签核(Post-processing & Sign-off)**

在布局布线完成后,需要进行后处理,包括寄生参数提取、时序签核、功耗计算和热分析。这些步骤确保设计满足所有制造要求,如工艺、电压和温度(PVT)条件下的工作。如果在签核阶段发现问题,可能需要返回布局布线阶段进行调整。

**tape-out**

tape-out是设计流程的最后一步,意味着设计团队提交最终的GDS2文件给芯片代工厂进行制造。在tape-out之前,设计需经过严格的技术签核,确保无误。

数字后端流程与工具在集成电路设计中扮演着核心角色,它将前端的抽象设计转化为物理实现,涉及到多个复杂的步骤和工具,需要设计师深入理解并不断迭代优化,以达到最佳的设计效果。

点击了解资源详情

点击了解资源详情

117 浏览量

2584 浏览量

199 浏览量

357 浏览量

357 浏览量

2021-10-04 上传

码男-波杰克

- 粉丝: 31

- 资源: 2

最新资源

- 计算机操作系统课后答案(西安电子科技大学版)

- 通用变频器应用技术.pdf

- 《开源》旗舰电子杂志2008年第4期

- C# 语言的微软官方说明书(权威)

- usb2.0协议 中文版

- 《开源》旗舰电子杂志2008年第3期

- 思科2950CR官方配置命令手册.pdf

- ABB ACS510_01 用户手册中文版

- 打造linux完美桌面

- STC单片机内部资源经典应用大全.PDF

- 进行空间,你的网站及域名的备案详细步骤

- Packt.Publishing.Learn.OpenOffice.org.Spreadsheet.Macro.Programming.Dec.2006.pdf

- 虚拟硬盘系统的实现及应用

- JasperReport3

- C/C++面试大全--算法和知识点详析

- DIV+CSS布局大全