没有合适的资源?快使用搜索试试~ 我知道了~

首页μC/OS-II和dspic33

资源详情

资源评论

资源推荐

Micriµm

© Copyright 2008, Micriµm

All Rights reserved

µC/OS-II

and the

Microchip dsPIC33

Application Note

AN-1033

www.Micrium.com

µC/OS-II and the Microchip dsPIC33

2

Table of Contents

1.00 Introduction ............................................................................................................. 3

2.00 The Microchip dsPIC33 programmer’s model ......................................................... 4

3.00 µC/OS-II Port for dsPIC33..................................................................................... 7

3.01 Directories and Files................................................................................................ 7

3.02 OS_CPU.H.............................................................................................................. 8

3.02.01 OS_CPU.H, macros for ‘externals’..................................................................... 8

3.02.02 OS_CPU.H, Data Types..................................................................................... 8

3.02.03 OS_CPU.H, Critical Sections ............................................................................. 9

3.02.04 OS_CPU.H, Stack growth .................................................................................. 9

3.02.05 OS_CPU.H, Task Level Context Switch............................................................. 9

3.02.06 OS_CPU.H, Function Prototypes ..................................................................... 10

3.03 OS_CPU_C.C ....................................................................................................... 10

3.03.01 OS_CPU_C.C, OSInitHookBegin()................................................................... 10

3.03.02 OS_CPU_C.C, OSInitHookEnd() ..................................................................... 11

3.03.03 OS_CPU_C.C, OSTaskCreateHook() .............................................................. 11

3.03.04 OS_CPU_C.C, OSTaskStkInit() ....................................................................... 12

3.03.05 OS_CPU_C.C, OSTaskSwHook().................................................................... 15

3.03.06 OS_CPU_C.C, OSTimeTickHook().................................................................. 15

3.04 OS_CPU_A.S........................................................................................................ 16

3.04.01 OS_CPU_A.S, OSStartHighRdy().................................................................... 16

3.04.02 OS_CPU_A.S, OSCtxSw()............................................................................... 17

3.04.03 OS_CPU_A.S, OSIntCtxSw()........................................................................... 18

3.04.04 OS_CPU_A.S, T2Interrupt()............................................................................. 18

3.04.05 OS_CPU_A.S, T4Interrupt()............................................................................. 19

3.05 OS_CPU_UTIL_A.S.............................................................................................. 20

3.06 OS_DBG.C............................................................................................................ 21

4.00 Interrupt Handling.................................................................................................. 22

5.00 Application Code ................................................................................................... 26

5.01 APP.C, APP.H and APP_CFG.H........................................................................... 27

5.02 INCLUDES.H......................................................................................................... 29

5.03 OS_CFG.H............................................................................................................ 29

6.00 BSP (Board Support Package).............................................................................. 30

7.00 Conclusion............................................................................................................. 31

Licensing ...................................................................................................................... 32

References.................................................................................................................... 32

Contacts ...................................................................................................................... 32

µC/OS-II and the Microchip dsPIC33

3

1.00 Introduction

This application note describes how µC/OS-II has been ported to the Microchip dsPIC33 family of

processors. This application note does not assume any specific dsPIC33 derivative.

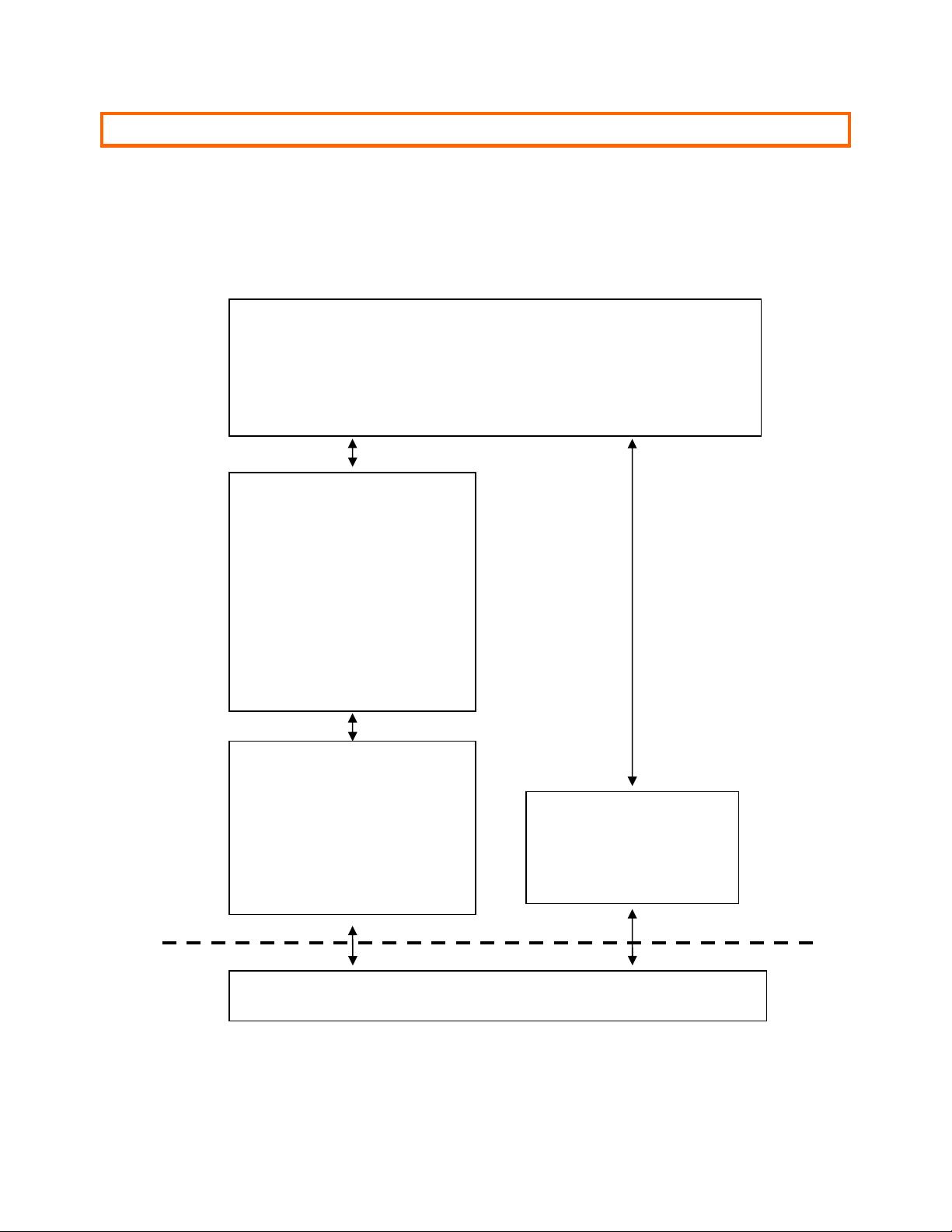

Figure 1-1 shows a block diagram showing the relationship between your application, µC/OS-II, the port

code and the BSP (Board Support Package). Relevant sections of this application note are referenced

on the figure.

µC/OS-II

OS_CORE.C

OS_FLAG.C

OS_MBOX.C

OS_MEM.C

OS_MUTEX.C

OS_Q.C

OS_SEM.C

OS_TASK.C

OS_TIME.C

OS_TMR.C

uCOS II.H

µC/OS-II

dsPIC33 Port

OS_CPU_C.C

OS_CPU_A.S

OS_CPU_UTIL_A.S

OS_CPU.H

OS DBG.C

Section 5

Your Application

APP.C

APP.H

APP_CFG.H

INCLUDES.H

O

S CFG.H

Explorer 16 / Target Board

BSP

BSP.C

BSP.H

Section 2

µC/OS-II

Book

Section 6

Section 3

Figure 1-1, Relationship between modules.

µC/OS-II and the Microchip dsPIC33

4

2.00 The Microchip dsPIC33 programmer’s model

This section provides a brief description of the dsPIC33 programmer’s model. We present enough

information in this section to provide a brief introduction. A complete description can be found in the

Microchip documentation.

The dsPIC33 family of CPU cores features proprietary Microchip architecture and is designed for

controller applications using a 16-bit (data), DSP capable architecture. Below are some of the features of

the dsPIC33 family of CPU cores:

• 16 General-purpose ‘Working’ registers

• Dual 40 bit Accumulators, 17x17 Multiplier

• 24 bit variable length instruction word, 23 bit program counter.

• 40 bit barrel shifter capable of 16 bit shift left of shift right in 1 cycle.

• Dedicated 1KB of DMA Ram

• Hardware divider support

• Dual Address generators for accessing memory blocks X and Y.

• High speed deterministic interrupt processing

The dsPIC33 is a Little Endian architecture and thus the least significant byte of a value is placed at a

lower memory location than its most significant byte.

Figure 2-1 shows the register model of the dsPIC33 and consist of 16 Working registers, two 40 bit

accumulators, the Data Table Page register, the Program Space Visibility Page Address register, a

Repeat Loop Counter, three dedicated DO Loop registers, the Core Configuration register, and a CPU

Status register.

W0-W15 (Working Registers)

• Registers W0-W3 are general purpose scratch pad registers

• Registers W4-W7 are the DSP Operand registers

• Registers W8-W11 are the DSP address registers

• Register W12 doubles as the DSP Offset register

• Register W13 doubles as the DSP Write Back register

• Register W14 doubles as the Frame Pointer register

• Register W15 doubles as the CPU Stack Pointer register

The stack pointer always points to the last pushed element. In other words, when an element is

pushed onto the stack, the stack pointer is first decremented and the value placed at the current

location where the stack is pointing to. The stack is popped by first reading the contents of the

stack and then incrementing the stack pointer.

SPLIM (Stack Pointer Limit Register)

• Causes a TRAP error when W15 is greater than SPLIM

ACCA / ACCB (DSP Accumulators)

• Dual 40 bit accumulators for DSP operations

TBLPAGE (Table Page Register)

• The 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program

space. This is concatenated with a 16-bit effective address in order to arrive at a full 24-bit

program space address.

µC/OS-II and the Microchip dsPIC33

5

PSVPAG (Program Space Visibility Page Address Register)

• For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to

define a 16K word page in the program space. When the Most Significant bit of the EA is ‘1’,

PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space

address. Unlike table operations, this limits remapping operations strictly to the user memory

area.

RCOUNT (Repeat Loop Counter)

• The RCOUNT register tracks the iteration count of an instruction that must be executed

repetitively until its operation has been completed. Divide instructions are iterative instructions

that make extensive use of the RCOUNT register.

DCOUNT (Do Loop Counter)

• Counts the iteration number of a DO loop

DOSTART (Do Loop Start Address)

• Holds the start address of a particular DO loop

DOEND (Do Loop End Address)s

• Holds the end address of a particular DO loop

CORECON (Core Configuration Register)

• Contains configuration bits pertaining to how the processor handles certain types of operations.

STATUS (CPU Status Register)

• Contains status CPU status flags indicating the state of the CPU after a given instruction.

剩余31页未读,继续阅读

wjm_0603

- 粉丝: 5

- 资源: 33

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0