没有合适的资源?快使用搜索试试~ 我知道了~

首页MT6223 GSM/GPRS Baseband Processor Data Sheet Revision 2.01

1. System Overview MT6223 is an entry level chipset solution with class 12 GPRS/GSM modem. It integrates only only analog baseband but also power management blocks into one chip and can greatly reduce the component count and make smaller PCB size. Besides, MT6223 is capable of SAIC (Single Antenna Interference Cancellation) and AMR speech. Based on 32 bit ARM7EJ-STM RISC processor, MT6223 provides an unprecedented platform for high quality modem performance. Typical application diagram is shown in Figure 1.

资源详情

资源评论

资源推荐

MT6223 GSM/GPRS

Baseband Processor

Data Sheet

Revision 2.01

Oct 05, 2007

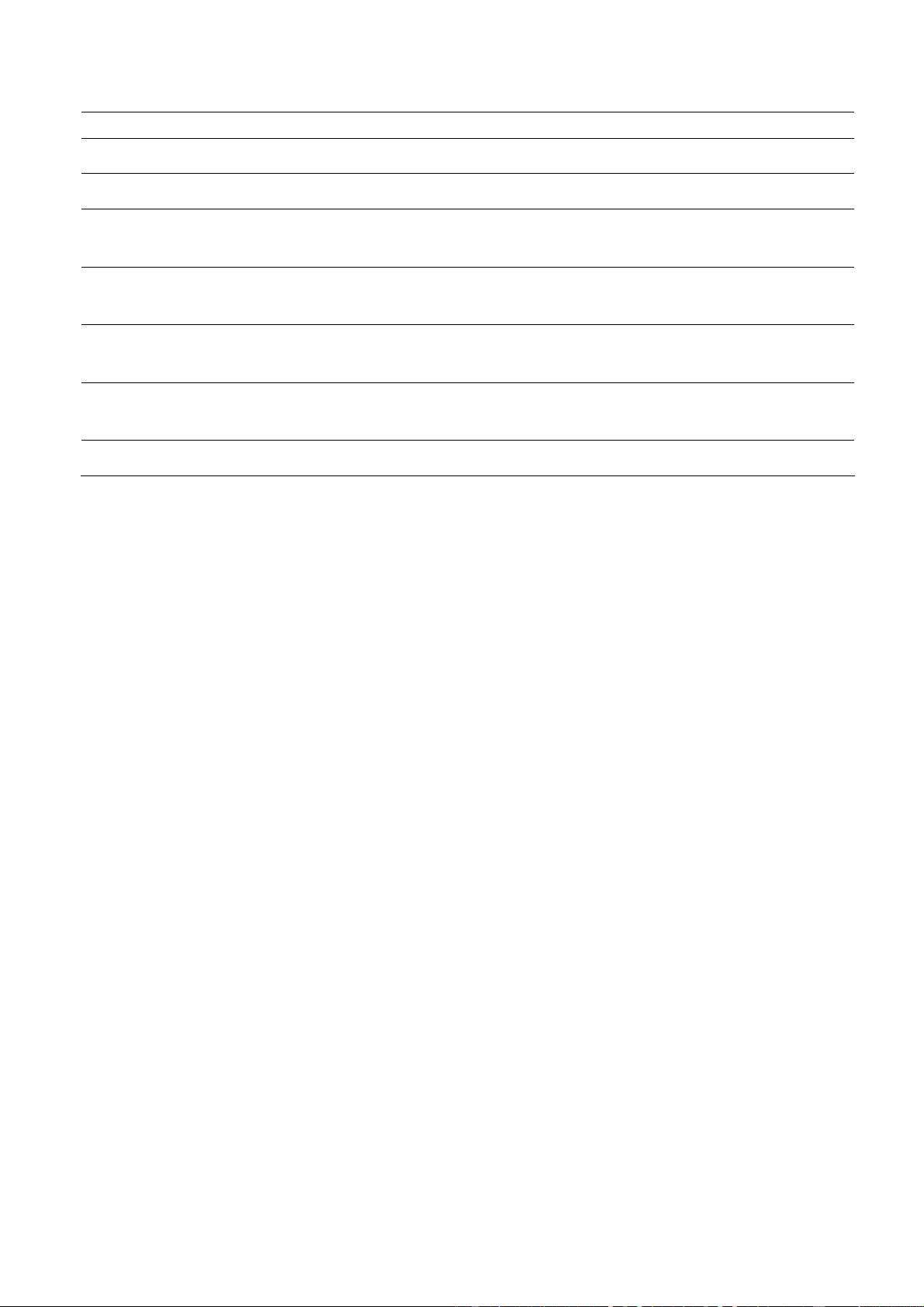

Revision History

Revision Date Comments

1.00 Oct 26, 2006 First Release

1.01 Nov 6, 2006 Modify Pin-out, LCD interface, GPIO and analog control

1.02 Nov 17, 2006 1. Modify LCD interface

2. Modify EMI descriptions

3. Modify GPIO

4. Modify Analog front end and audio front end

1.03 Dec 1, 2006 1. Modify micro-controller subsystem descriptions.

2. Add PMU descriptions into analog front end part.

1.06 Mar 19, 2007 1. Update Baseband Front End descriptions

2. Update General Purpose IO descriptions

3. Add Efuse Controller segment

4. Update analog front end and PMU part descriptions

5. Update Auxiliary ADC segment

6. Update Automatic Frequency Control segment

7. Update Timing Generator descriptions

8. Update Software power down control

1.07 Apr 3, 2007 1. Remove NAND and memory card interface descriptions

2. Remove NiMH battry charger support in product summary section

1.08 Apr 13, 2007 1. Modify naming of external memory interface pin out

1.09 May 29,2007 1. Modify system overview descriptions

1.10 Jun 6

th

, 2007 1. Update information for MT6223P, including feature and part number

2. Hardware change for MT6223P’s new feature, including LCD interface change and GPIO

setting

1.11 Jun 13

th

, 2007 1. Correct the typo in row number of TFBGA dimension

2. BPI_BUS2 should be placed in ball number R3, and number U2 have no ball out

1.12 Jun 14

th

, 2007 1. Modified TFBGA diagram figure

1.13 Jun 21

th

, 2007 Limit the card type

1.14 Jun 26

th

, 2007 Reverse Aux Func. 0 and Aux Func. 1

1.15 Jun 27

th

, 2007 Remove serial LCD interface and EINT7 in 2.3 Pin description, MFIQ should reside at GPIO

mode 1 of GPIO52

1.16 Jul 5

th

, 2007 Add driving strength to BPI_BUS3 and slow-down control for wavetable, corresponding to E5

1.17 Jul 21

th

, 2007 Modify the BGA diagram

1.18 Aug 02

th

,

2007

Remove incorrect description about USB and other project name. Change the VRTC LDO

spec.

1.19 Aug 22

th

,

2007

Remove GPIO52 mode 0 from ECS3_B. Add digital pin electrical characteristics section

1.20 Aug 24

th

,

2007

Replace MIRQ at EINT2 (GPIO42)

2.00 Aug 30

th

,

2007

Revised CC mode spec.

2.01 Oct 4

th

, 2007 Correct GPIO50 definition and new electrical characteristics

TABLE OF CONTENTS

Revision History......................................................................................................................................................................2

1. System Overview..............................................................................................................................................................6

1.1 Platform Features .....................................................................................................................................................10

1.2 MODEM Features .................................................................................................................................................... 11

1.3 Multi-Media Features ...............................................................................................................................................12

1.4 General Description.................................................................................................................................................. 13

2 Product Descriptions.....................................................................................................................................................15

2.1 Pin Outs....................................................................................................................................................................15

2.2 Top Marking Definition............................................................................................................................................ 17

2.3 Pin Description......................................................................................................................................................... 20

2.4 Digital Pin Electrical Characteristics........................................................................................................................31

3 Micro-Controller Unit Subsystem................................................................................................................................31

3.1 Processor Core..........................................................................................................................................................36

3.2 Memory Management ..............................................................................................................................................36

3.3 Bus System...............................................................................................................................................................39

3.4 Direct Memory Access .............................................................................................................................................43

3.5 Interrupt Controller...................................................................................................................................................62

3.6 External Memory Interface.......................................................................................................................................79

3.7 Internal Memory Interface........................................................................................................................................ 91

3.8 Alerter.......................................................................................................................................................................91

3.9 SIM Interface............................................................................................................................................................ 94

3.10 Keypad Scanner...................................................................................................................................................... 104

3.11 LCD Interface......................................................................................................................................................... 107

3.12 UART .....................................................................................................................................................................120

3.13 Auxiliary ADC Unit ............................................................................................................................................... 138

3.14 General Purpose Inputs/Outputs............................................................................................................................. 141

3.15 General Purpose Timer ........................................................................................................................................... 159

3.16 GPRS Cipher Unit.................................................................................................................................................. 163

3.17 Security Engine ......................................................................................................................................................168

3.18 Real Time Clock..................................................................................................................................................... 171

3.19 Divider.................................................................................................................................................................... 179

3.20 CSD Accelerator.....................................................................................................................................................184

3.21 FCS Codec..............................................................................................................................................................198

3.22 EFUSE Controller (efusec).....................................................................................................................................202

4 Radio Interface Control..............................................................................................................................................203

4.1 Baseband Serial Interface ....................................................................................................................................... 203

4.2 Baseband Parallel Interface ....................................................................................................................................212

4.3 Automatic Power Control (APC) Unit ................................................................................................................... 217

4.4 Automatic Frequency Control (AFC) Unit.............................................................................................................224

5 Baseband Front End....................................................................................................................................................228

5.1 Baseband Serial Ports............................................................................................................................................. 229

5.2 Downlink Path (RX Path)....................................................................................................................................... 232

5.3 Uplink Path (TX Path)............................................................................................................................................242

6 Audio Front-End..........................................................................................................................................................247

6.1 General Description................................................................................................................................................ 247

6.2 Register Definitions................................................................................................................................................ 250

6.3 DSP Register Definitions........................................................................................................................................256

6.4 Programming Guide ...............................................................................................................................................260

7 Timing Generator........................................................................................................................................................261

7.1 TDMA timer...........................................................................................................................................................261

7.2 Slow Clocking Unit ................................................................................................................................................ 272

8 Power and Clocks ........................................................................................................................................................276

8.1 Software Power Down Control...............................................................................................................................276

9 Analog Front-end & Analog Blocks ...........................................................................................................................282

9.1 General Description................................................................................................................................................ 282

9.2 MCU Register Definitions......................................................................................................................................294

9.3 Programming Guide ...............................................................................................................................................333

剩余343页未读,继续阅读

sunriseye

- 粉丝: 1

- 资源: 35

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1