Architecture

20 of 141 DDR PHY Interface, Version 3.1

Copyright 1995-2014 March 21, 2014

Cadence Design Systems, Inc.

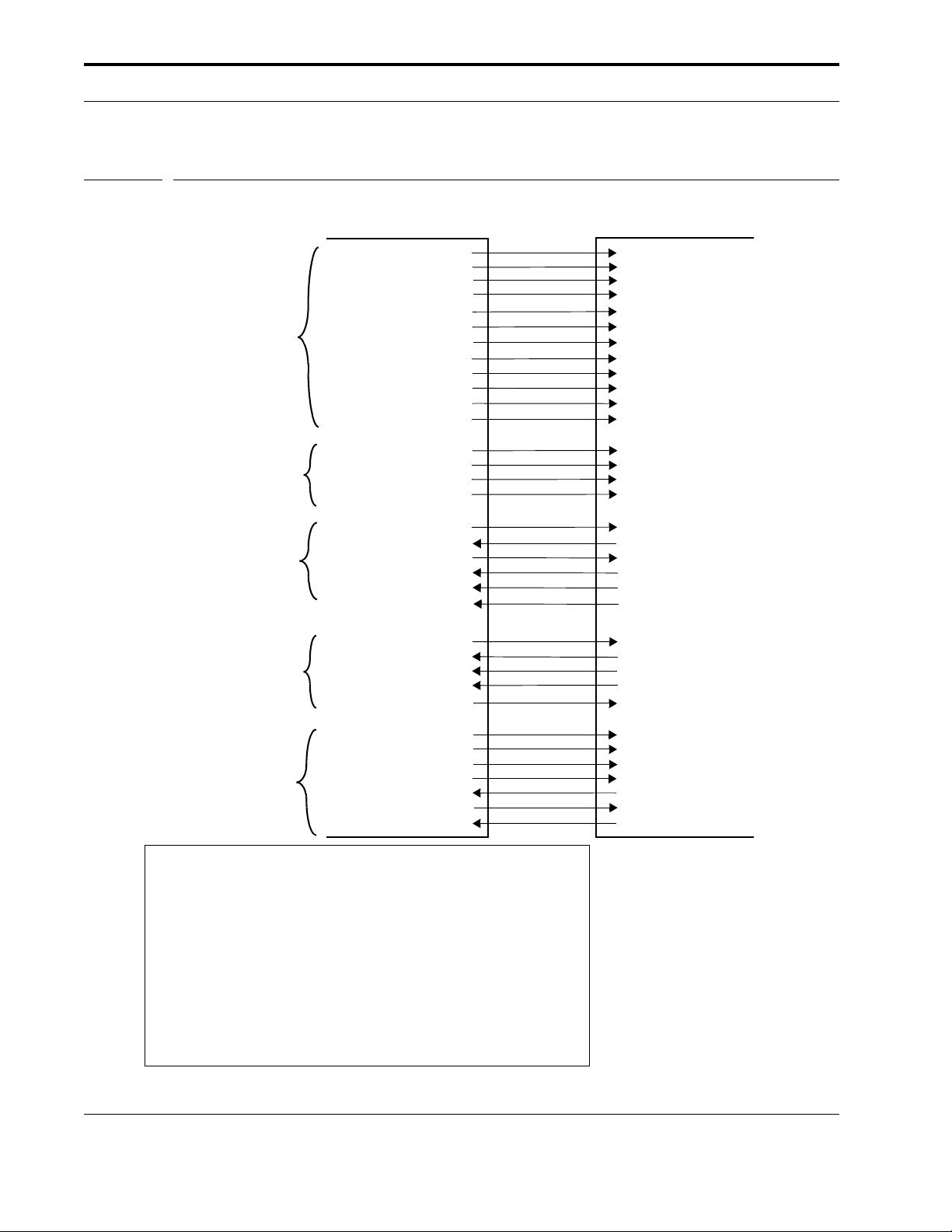

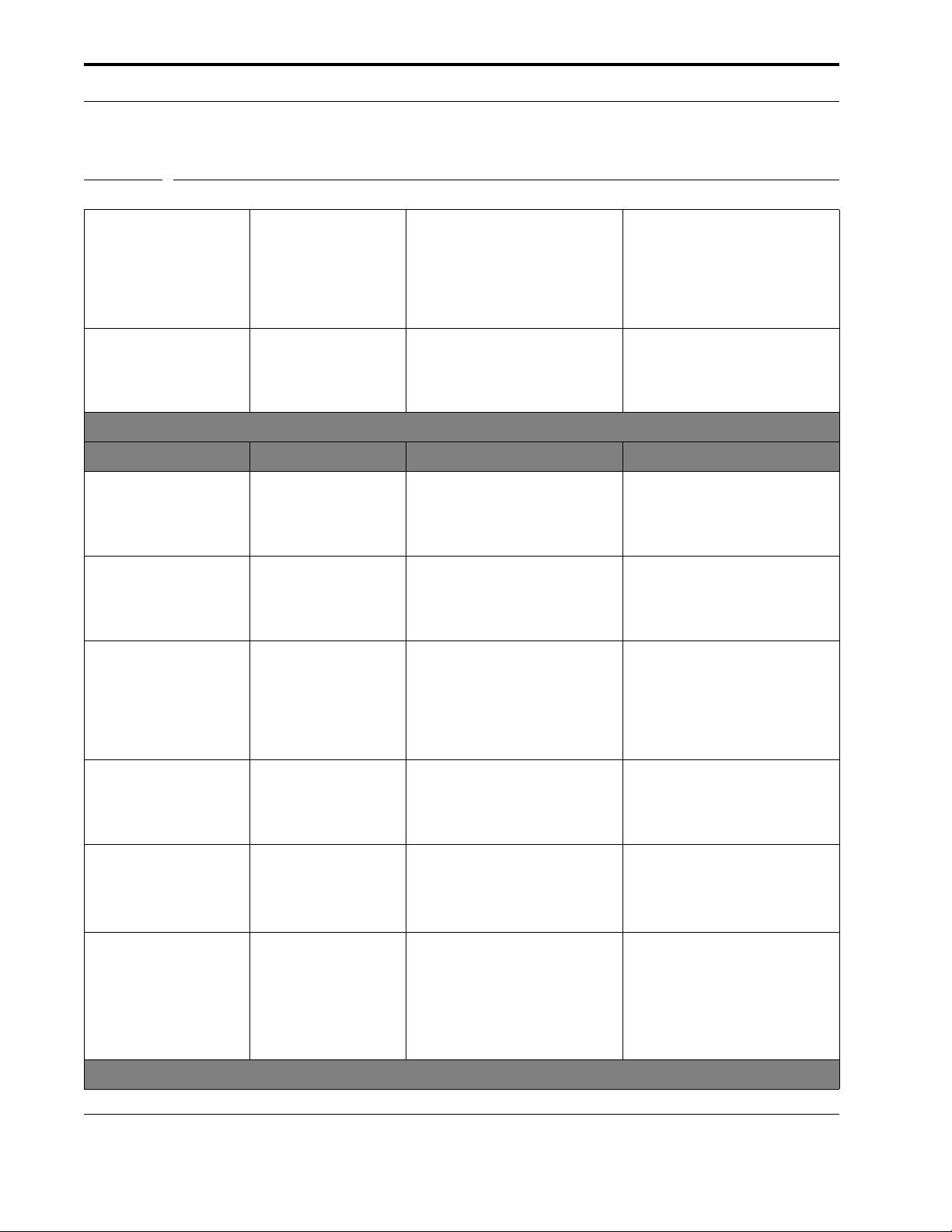

dfi_wrdata_cs_n_pN t

phy_wrcsgap

t

phy_wrcslat

Required for all DRAMs if any of

the training features are supported,

otherwise, optional.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

Optional.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

dfi_wrdata_mask_pN phy

crc_mode

t

phy_wrdata

t

phy_wrlat

Required for all DRAMs.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

Required for all DRAMs.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

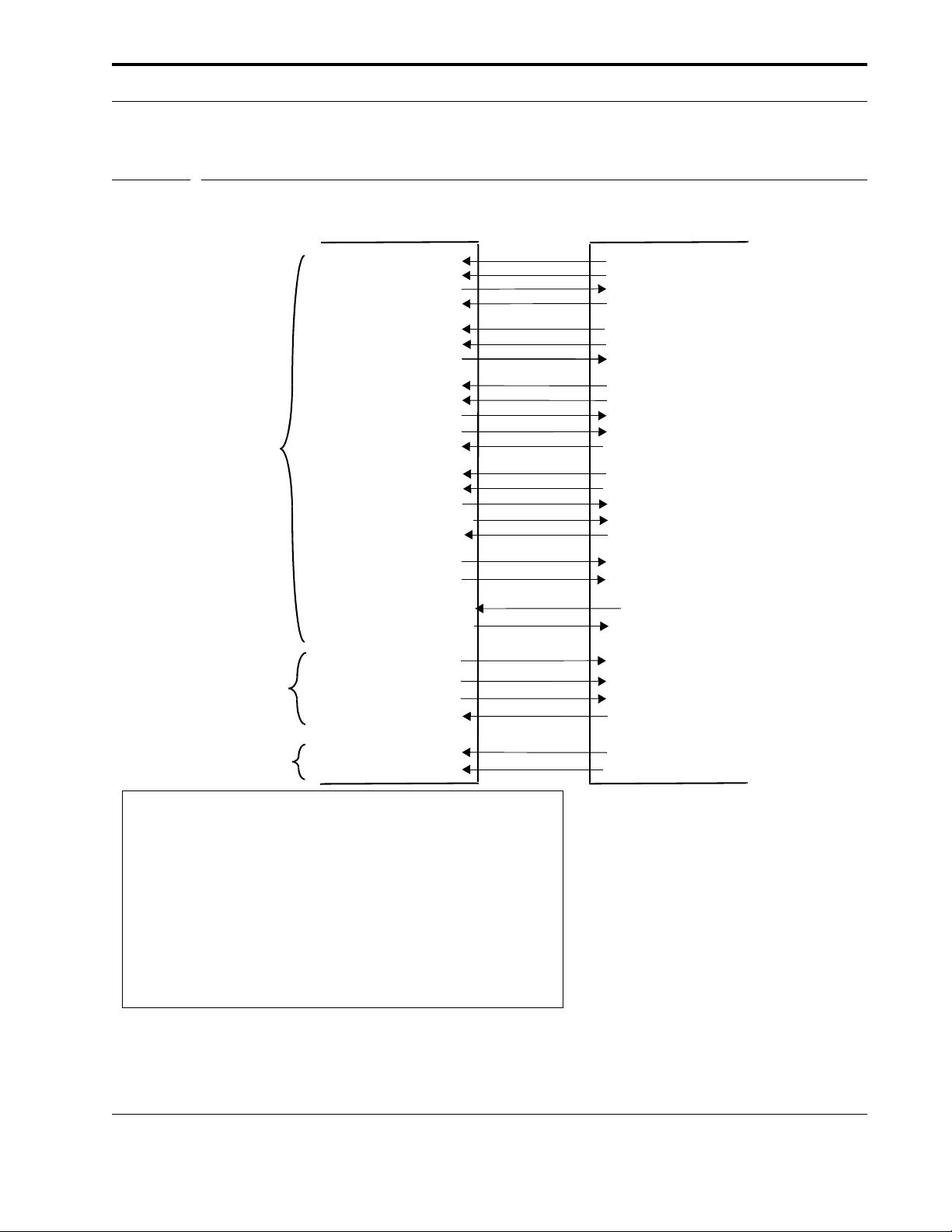

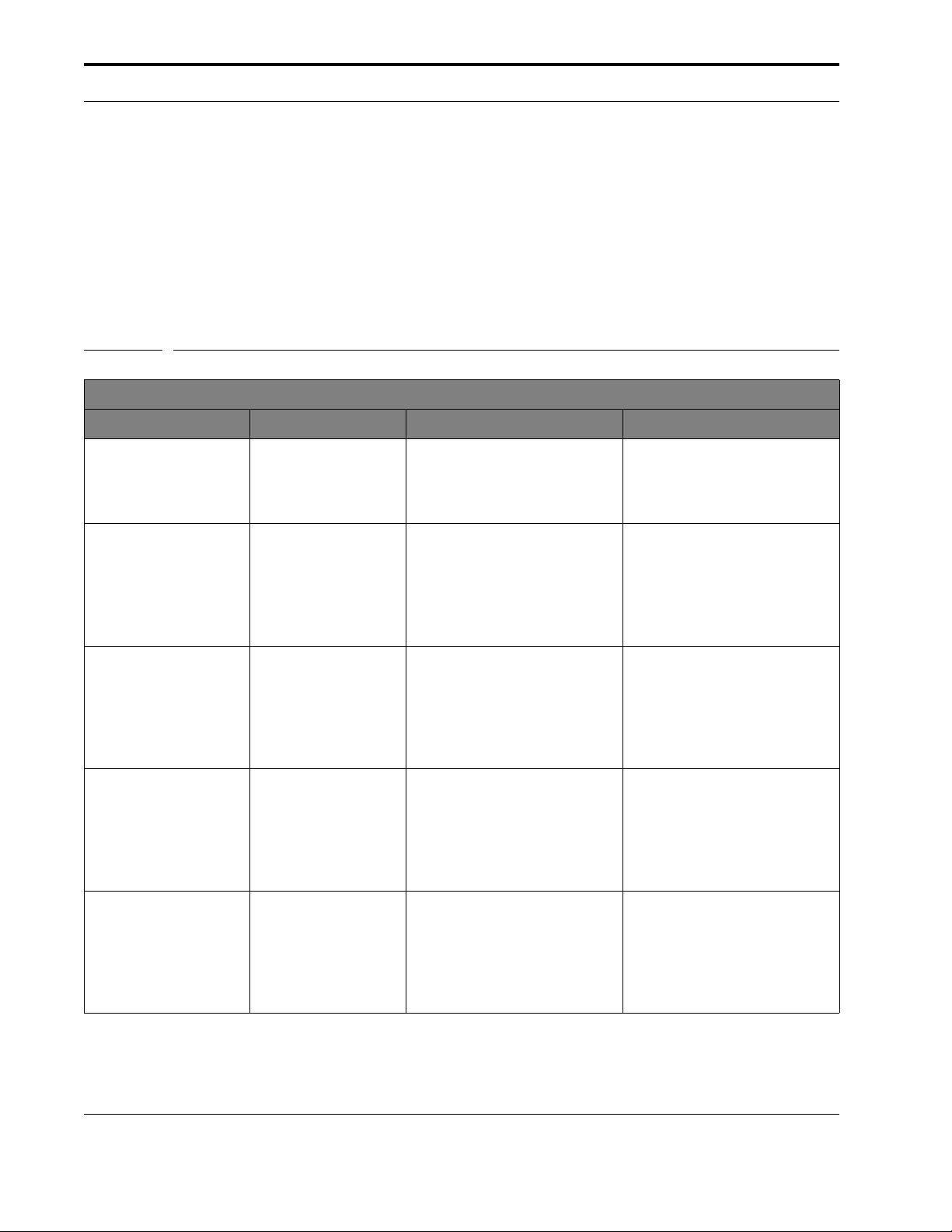

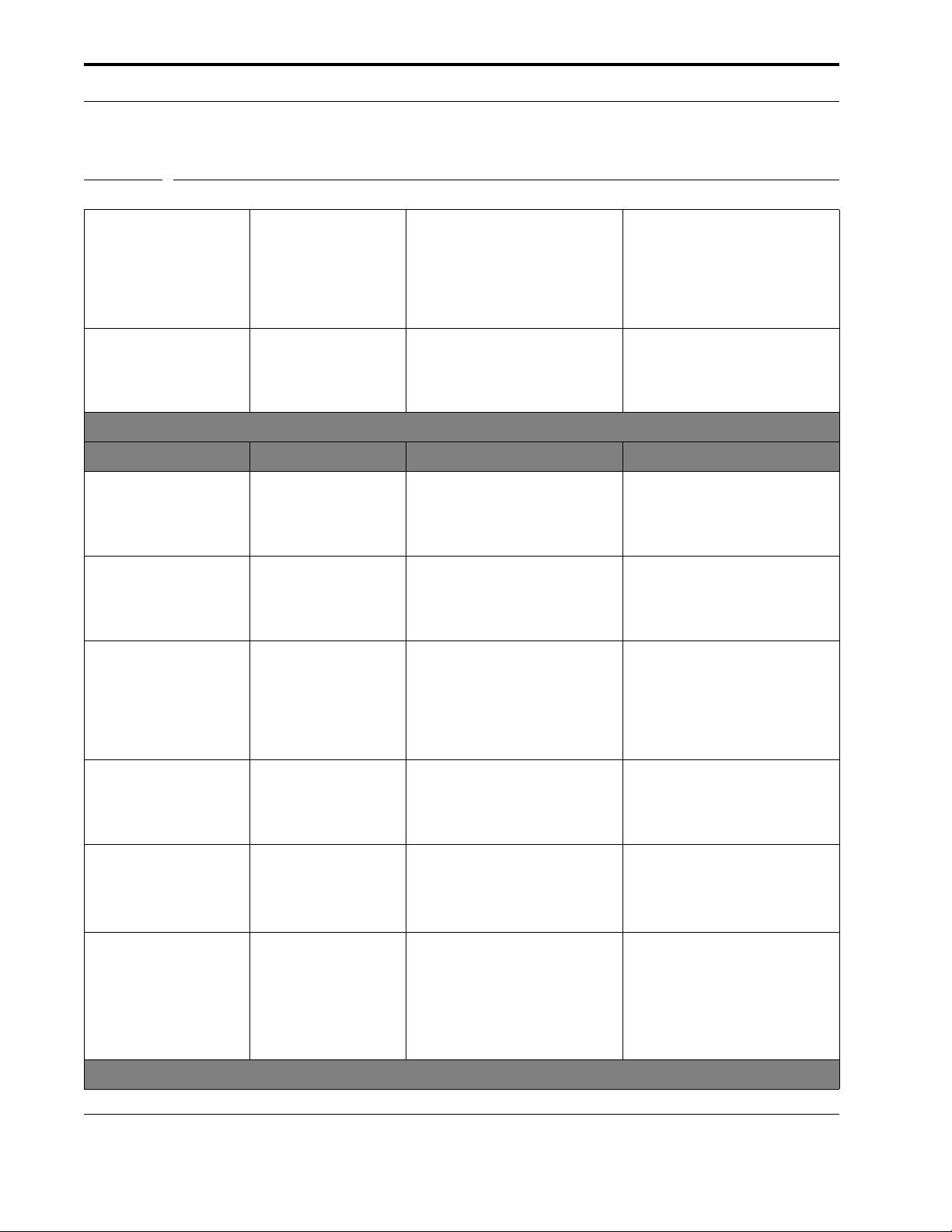

Read Interface Group

Signal Associated Parameters MC PHY

dfi_rddata_en_pN t

phy_rdlat

t

rddata_en

dfi

rw_length

Required for all DRAMs.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

Required for all DRAMs.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

dfi_rddata_wN

t

phy_rdlat

t

rddata_en

Required for all DRAMs.

Suffix (_wN) required for

frequency ratio systems to replicate

information across the phases.

a

Required for all DRAMs.

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

dfi_rddata_cs_n_pN t

phy_rdcsgap

t

phy_rdcslat

Required for all DRAMs if read

training is supported, otherwise,

optional.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

Optional.

Suffix (_pN) required for

frequency ratio systems to replicate

information across the phases.

a

dfi_rddata_valid_wN t

phy_rdlat

t

rddata_en

Required for all DRAMs.

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

Required for all DRAMs.

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

dfi_rddata_dnv_wN t

phy_rdlat

t

rddata_en

Required for LPDDR2 DRAM.

b

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

Required for LPDDR2 DRAM.

b

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

dfi_rddata_dbi_n_wN phy

dbi_mode

t

phy_rdlat

t

rddata_en

Applicable for DDR4 only.

Required when MC DBI support is

enabled and phy

dbi_mode

=0.

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

Applicable for DDR4 only.

Required when MC DBI support is

enabled and phy

dbi_mode

=0.

Suffix (_wN) required for

frequency ratio systems to replicate

information across the word.

a

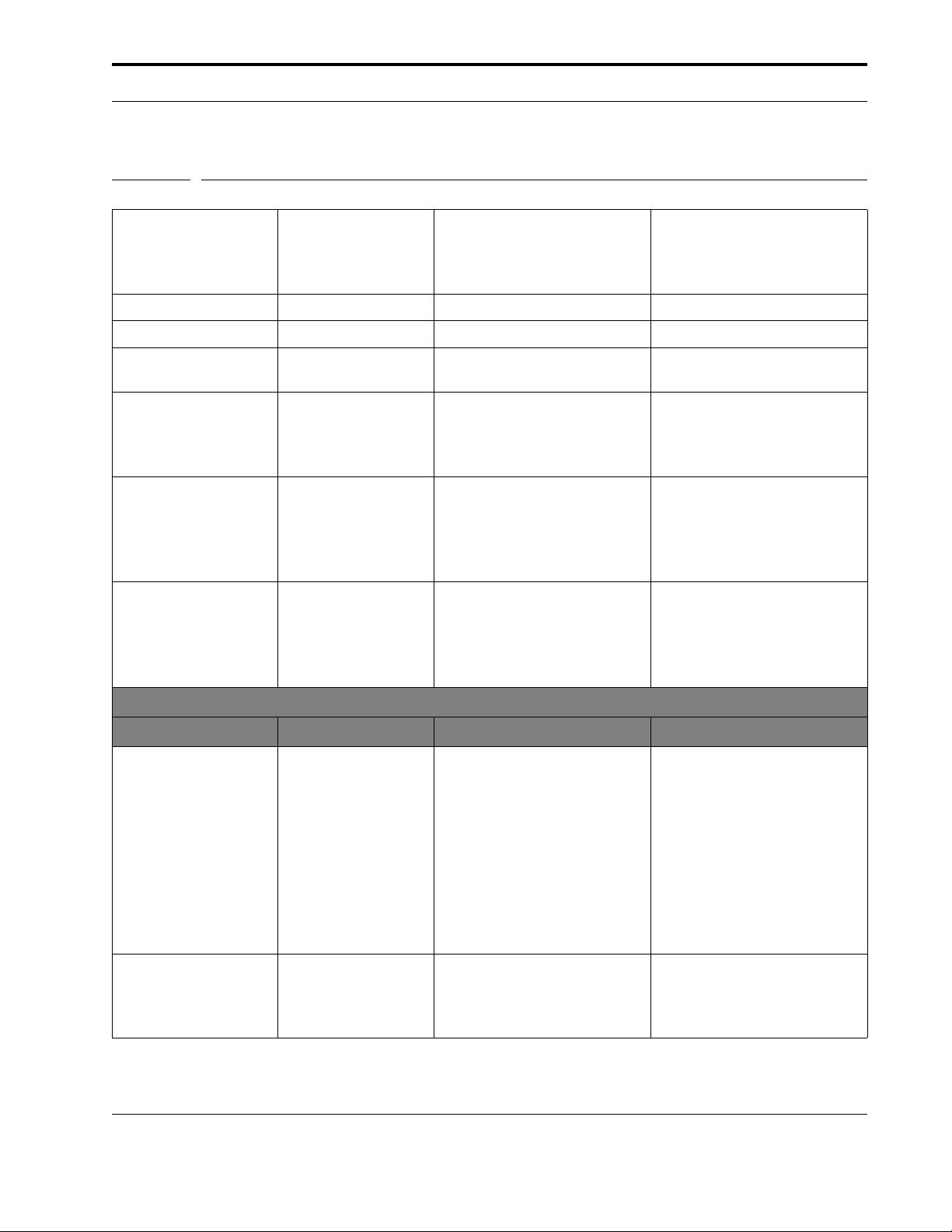

Update Interface Group

TABLE 2. DFI Signal Requirements (Continued)