使用ModelSim设计74LS160十进制计数器

需积分: 49 70 浏览量

更新于2023-03-16

2

收藏 69KB DOC 举报

"本次实验是关于使用FPGA设计一个十进制计数器,主要工具是MModelSim,这是一款强大的语言仿真器,支持VHDL和Verilog混合仿真,适用于FPGA和ASIC设计的仿真。实验目标包括理解74LS160计数器的工作原理,熟悉MModelSim的使用,并掌握仿真流程。74LS160是一款同步十进制加法计数器,具备异步清零和同步预置数功能。实验中将利用74LS160来构建一个可实现任意进制计数的计数器。"

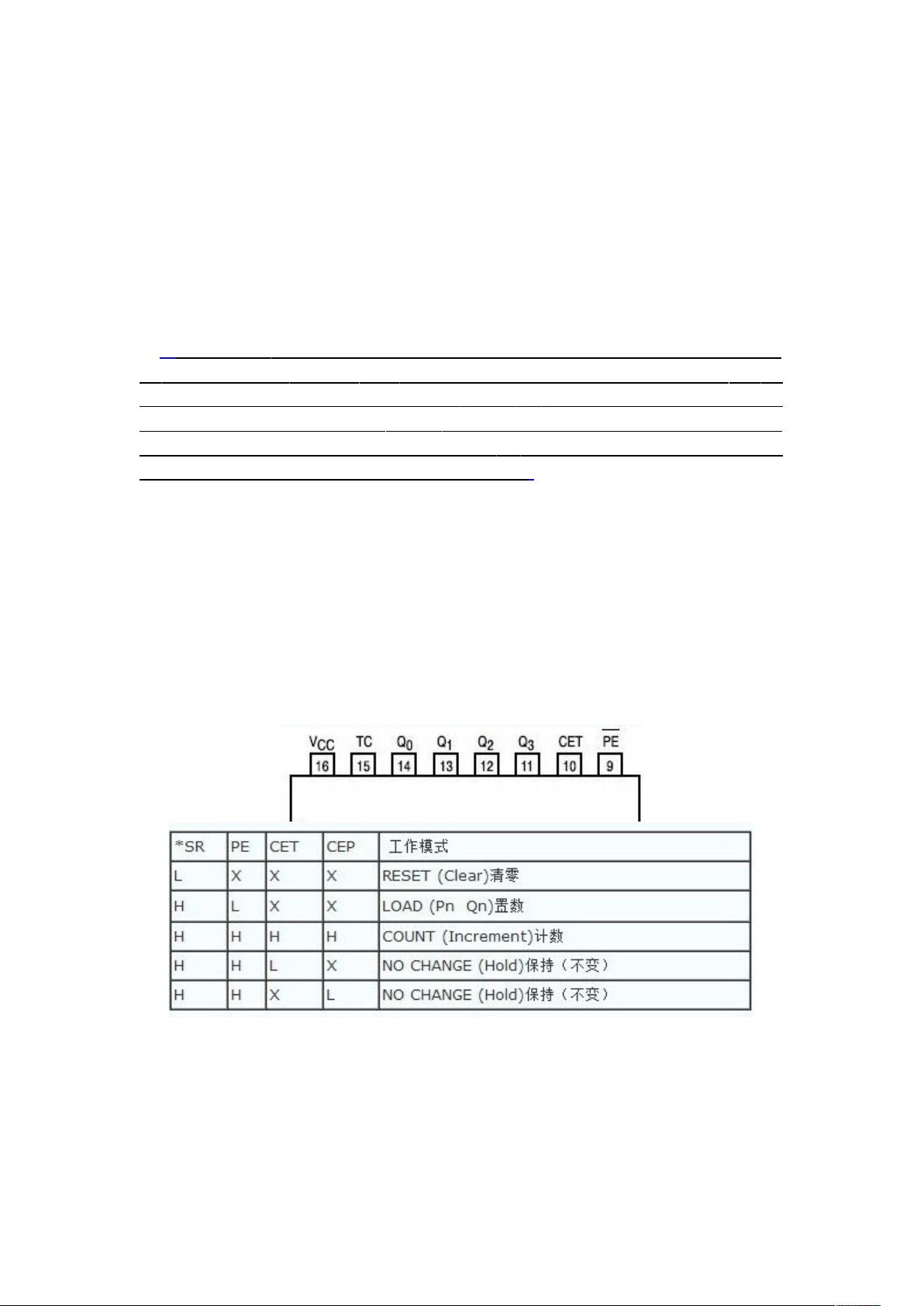

在实验设计中,74LS160计数器是一个关键组件,它有四个输出端Q0到Q3,能够进行二进制计数。当DR引脚为低电平时,计数器会被异步清零,所有输出变为0。同步预置功能则是在LD为低电平且时钟脉冲上升沿时,数据D0到D3被加载到计数器,形成特定的初始值。计数器的正常计数功能只有在使能端EP和ET均为高电平时才会启动。此外,还给出了74LS160的引脚图和选择开关方式的真值表,以供参考。

在编程实现方面,实验提供了使用Verilog HDL语言编写的源程序。模块`decade_counter`定义了一个4位的计数器,参数`SIZE`可以根据需要调整。输入包括时钟信号、装载禁用(load_n)、清除禁用(clear_n)以及装载数据。输出是计数器的当前值`q`。代码中,`always`块根据不同的条件更新`q`的值,如装载数据、清除计数器或者正常计数。当计数达到9(十进制计数器的上限)时,计数值会重置为0。

测试程序部分未给出完整内容,但通常会包含对`decade_counter`模块的实例化以及时钟和其他输入信号的激励生成,以验证计数器的功能是否正确。这部分通常会使用`initial`块来设定初始条件,然后使用`#`延迟语法来驱动时钟和其他控制信号,以便观察计数器的输出波形。

整个实验旨在提高学生对FPGA设计的理解,特别是使用硬件描述语言(HDL)以及仿真工具MModelSim进行逻辑设计的能力。通过这个实验,学生不仅能够掌握74LS160的实际应用,还能深入理解数字逻辑和FPGA设计的基础知识。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-10-07 上传

2021-09-25 上传

2023-10-19 上传

2022-04-08 上传

2022-10-19 上传

2022-06-14 上传

yangqingqianling

- 粉丝: 0

- 资源: 2

最新资源

- MANITOR-Raspberry:Manitor Para La树莓

- react-text-transition:动画文字更改

- 季节

- embafu:这是embafu short let上市网站的应用程序

- bg-helper-cubalibre:自由古巴的人工智能伴侣

- 基于微信小程序的疫苗预约接种系统.zip

- flax:Flax是JAX的神经网络生态系统,旨在提高灵活性

- 谷歌视觉API

- 天池短租新人赛-数据集

- 温特线性matlab代码-Dual-Inverted-Pendulum-MATLAB:为双倒立摆设计控制器和估计器。UCSDWinter15'

- 在Android上将实时摄像头与AI危害检测配合使用

- go-netstat:用Go编写的netstat实现

- meanBackend:我正在一个完整JavaScript环境中工作!

- square-kappa

- Android应用源码多种特效,实现多种动画,抽屉效果、多种自定义的view-IT计算机-毕业设计.zip

- 基于java的大数据分析.zip