没有合适的资源?快使用搜索试试~ 我知道了~

首页SSD2828 datasheet

The SSD2828 IC is an MIPI master bridge chip that connects an application processor with traditional parallel LCD interface and an LCD driver with MIPI slave interface. The 2828 supports up to 1Gbps per lane speed with maximum 4 lanes using both parallel RGB interface and serial SPI interface

资源详情

资源评论

资源推荐

SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

This document contains information on a new product. Specifications and information herein are subject to change

without notice.

http://www.solomon-systech.com

SSD2828QN4

Rev 1.2 P 1/167 Dec 2012

Copyright © 2012 Solomon Systech Limited

SSD2828QN4

Advance Information

MIPI Master Bridge

SSD2828QN4 Rev 1.2 P 2/167 Dec 2012 Solomon Systech

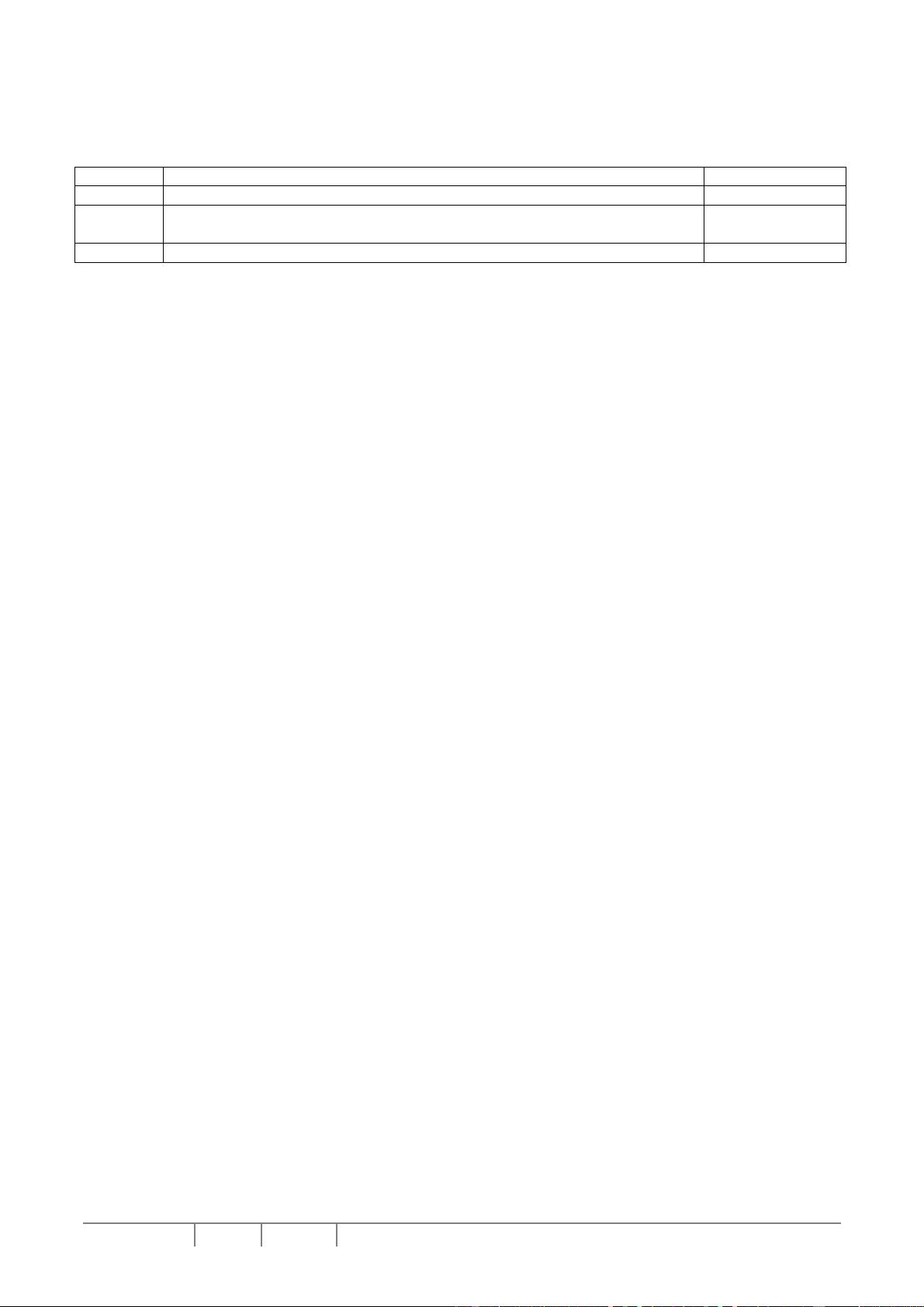

Appendix 1: IC Revision history of SSD2828 Specification

Version Change Items Effective Date

1.0 Initial release of Advance Information 16-Oct-12

1.1 - Modify the description of END and CO (Section 8.1.38)

- Modify the timing for data latch in RGB timing (Section 14.4)

13-Dec-12

1.2 - Specify the prefix T in RGB timing (Section14.4) 09-Jan-13

SSD2828QN4 Rev 1.2 P 3/167 Dec 2012 Solomon Systech

CONTENTS

1 GENERAL DESCRIPTION ....................................................................................................... 9

2 FEATURES................................................................................................................................. 10

2.1 REFERENCES........................................................................................................................................................10

2.2 DEFINITIONS ........................................................................................................................................................10

3 ORDERING INFORMATION................................................................................................. 11

4 BLOCK DIAGRAM .................................................................................................................. 11

5 FUNCTIONAL DESCRIPTION .............................................................................................. 14

5.1 FUNCTIONAL BLOCKS..........................................................................................................................................14

5.2 CLOCK AND RESET MODULE ...............................................................................................................................14

5.3 EXTERNAL INTERFACE.........................................................................................................................................15

5.4 PROTOCOL CONTROL UNIT (PCU).......................................................................................................................15

5.5 PACKET PROCESSING UNIT (PPU) .......................................................................................................................15

5.6 ERROR CORRECTION CODE/ CYCLIC REDUNDANCY CHECK (ECC/CRC)............................................................16

5.7 LONG AND COMMAND BUFFERS ..........................................................................................................................16

5.8 INTERRUPT SIGNAL ..............................................................................................................................................16

5.9 D-PHY CONTROLLER..........................................................................................................................................16

5.10 ANALOG TRANSCEIVER .......................................................................................................................................16

5.11 INTERNAL PLL ....................................................................................................................................................17

6 SSD2828QN4 PIN ASSIGNMENT........................................................................................... 18

7 PIN DESCRIPTION .................................................................................................................. 20

8 COMMAND TABLE................................................................................................................. 23

8.1 REGISTER DESCRIPTION.......................................................................................................................................25

8.1.1 Device Identification Register.....................................................................................................................25

8.1.2 RGB Interface Control Register 1...............................................................................................................26

8.1.3 RGB Interface Control Register 2...............................................................................................................27

8.1.4 RGB Interface Control Register 3...............................................................................................................28

8.1.5 RGB Interface Control Register 4...............................................................................................................29

8.1.6 RGB Interface Control Register 5...............................................................................................................30

8.1.7 RGB Interface Control Register 6...............................................................................................................31

8.1.8 Configuration Register................................................................................................................................33

8.1.9 VC Control Register....................................................................................................................................35

8.1.10 PLL Control Register..................................................................................................................................36

8.1.11 PLL Configuration Register........................................................................................................................37

8.1.12 Clock Control Register................................................................................................................................38

8.1.13 Packet Size Control Register 1....................................................................................................................39

8.1.14 Packet Size Control Register 2....................................................................................................................40

8.1.15 Packet Size Control Register 3....................................................................................................................41

8.1.16 Generic Packet Drop Register ....................................................................................................................42

8.1.17 Operation Control Register ........................................................................................................................43

8.1.18 Maximum Return Size Register...................................................................................................................44

8.1.19 Return Data Count Register........................................................................................................................45

8.1.20 ACK Response Status Register....................................................................................................................46

8.1.21 Line Control Register..................................................................................................................................47

8.1.22 Interrupt Control Register ..........................................................................................................................49

8.1.23 Interrupt Status Register.............................................................................................................................50

8.1.24 Error Status Register ..................................................................................................................................52

8.1.25 Delay Adjustment Register 1.......................................................................................................................54

8.1.26 Delay Adjustment Register 2.......................................................................................................................55

SSD2828QN4 Rev 1.2 P 4/167 Dec 2012 Solomon Systech

8.1.27 Delay Adjustment Register 3.......................................................................................................................56

8.1.28 Delay Adjustment Register 4.......................................................................................................................57

8.1.29 Delay Adjustment Register 5.......................................................................................................................58

8.1.30 Delay Adjustment Register 6.......................................................................................................................59

8.1.31 HS TX Timer Register 1..............................................................................................................................60

8.1.32 HS TX Timer Register 2..............................................................................................................................61

8.1.33 LP RX Timer Register 1..............................................................................................................................62

8.1.34 LP RX Timer Register 2..............................................................................................................................63

8.1.35 TE Status Register.......................................................................................................................................64

8.1.36 SPI Read Register.......................................................................................................................................65

8.1.37 PLL Lock Register.......................................................................................................................................66

8.1.38 Test Register ...............................................................................................................................................67

8.1.39 TE Count Register.......................................................................................................................................69

8.1.40 Analog Control Register .............................................................................................................................70

8.1.41 Analog Control Register 2 ..........................................................................................................................71

8.1.42 Analog Control Register 3 ..........................................................................................................................72

8.1.43 Analog Control Register 4 ..........................................................................................................................73

8.1.44 Interrupt Output Control Register ..............................................................................................................74

8.1.45 RGB Interface Control Register 7...............................................................................................................75

8.1.46 Lane Configuration Register.......................................................................................................................76

8.1.47 Delay Adjustment Register 7.......................................................................................................................77

8.1.48 Pull Control Register 1...............................................................................................................................78

8.1.49 Pull Control Register 2...............................................................................................................................80

8.1.50 Pull Control Register 3...............................................................................................................................81

8.1.51 CABC Brightness Control Register 1..........................................................................................................82

8.1.52 CABC Brightness Control Register 2..........................................................................................................83

8.1.53 CABC Brightness Status Register ...............................................................................................................84

8.1.54 Encoder Control Register ...........................................................................................................................85

8.1.55 Video Sync Delay Register..........................................................................................................................86

8.1.56 Trimming Register ......................................................................................................................................87

8.1.57 GPIO1 Register...........................................................................................................................................89

8.1.58 GPIO2 Register...........................................................................................................................................91

8.1.59 DLYA01 Register ........................................................................................................................................93

8.1.60 DLYA23 Register ........................................................................................................................................94

8.1.61 DLYB01 Register ........................................................................................................................................95

8.1.62 DLYB23 Register ........................................................................................................................................96

8.1.63 DLYC01 Register ........................................................................................................................................97

8.1.64 DLYC23 Register ........................................................................................................................................98

8.1.65 Analog Control Register 5 ..........................................................................................................................99

8.1.66 Read Register............................................................................................................................................101

9 CONFIGURATION................................................................................................................. 102

9.1 LANE MANAGEMENT .........................................................................................................................................102

9.2 USE CASES .........................................................................................................................................................103

9.2.1 RGB + SPI Interface.................................................................................................................................103

9.2.2 MIPI DC Characteristics..........................................................................................................................105

9.2.3 High Speed Clock Transmission ...............................................................................................................106

9.2.4 Data Lane State Flow ...............................................................................................................................106

9.2.5 High Speed Data Transmission.................................................................................................................107

9.2.6 Bi-Directional Data Lane Turnaround.....................................................................................................109

9.2.7 Escape Mode.............................................................................................................................................109

9.2.8 Low Power Data Transmission.................................................................................................................111

9.2.9 Reset Trigger.............................................................................................................................................112

9.2.10 Tearing Effect............................................................................................................................................113

9.2.11 Acknowledge.............................................................................................................................................114

9.2.12 Packet Transmission.................................................................................................................................115

9.2.13 HS Transmission Example ........................................................................................................................115

9.2.14 General Packet Structure..........................................................................................................................116

9.2.15 Long Packet Format .................................................................................................................................116

9.2.16 Short Packet Structure..............................................................................................................................117

SSD2828QN4 Rev 1.2 P 5/167 Dec 2012 Solomon Systech

9.2.17 Data Identifier (DI)...................................................................................................................................117

9.2.18 Victual Channel Identifier (VC)................................................................................................................118

9.2.19 Data Type (DT).........................................................................................................................................118

9.3 OPERATING MODES ...........................................................................................................................................122

9.3.2 State machine operation............................................................................................................................135

9.3.3 D-PHY operation......................................................................................................................................136

9.3.4 Analog Transceiver...................................................................................................................................137

9.3.5 PLL ...........................................................................................................................................................137

9.3.6 Clock Source Example..............................................................................................................................138

10 EXTERNAL INTERFACE.................................................................................................. 139

10.1 SPI INTERFACE 8 BIT 4 WIRE .............................................................................................................................139

10.2 SPI INTERFACE 8 BIT 3 WIRE .............................................................................................................................141

10.2.1 3 or 4 wires 8bit SPI read back sequence for 0xFF register which is stored MIPI read back data .........143

10.3 SPI INTERFACE 24 BIT 3 WIRE ...........................................................................................................................145

10.3.1 3 wires 24bit SPI read back sequence for 0xFF register which is stored MIPI read back data...............147

11 MAXIMUM RATINGS........................................................................................................ 149

12 RECOMMENDED OPERATING CONDITIONS ........................................................... 150

13 DC CHARACTERISTICS................................................................................................... 151

14 AC CHARACTERISTICS................................................................................................... 153

14.1 8 BIT 4 WIRE SPI INTERFACE TIMING................................................................................................................154

14.2 8 BIT 3 WIRE SPI INTERFACE TIMING................................................................................................................155

14.3 24 BIT 3 WIRE SPI INTERFACE TIMING..............................................................................................................156

14.4 RGB INTERFACE TIMING ...................................................................................................................................157

14.5 RESET TIMING .................................................................................................................................................158

14.6 TX_CLK TIMING ..............................................................................................................................................158

15 POWER UP SEQUENCE.................................................................................................... 159

16 EXAMPLE FOR SYSTEM SLEEP IN AND OUT ........................................................... 160

17 SERIAL LINK DATA ORDER........................................................................................... 161

18 PACKAGE INFORMATION.............................................................................................. 164

18.1 DIMENSION FOR SSD2828QN4 .........................................................................................................................164

剩余166页未读,继续阅读

我是阿Q

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论5