1、熟悉 MAX+plusII 软件的基本使用方法。

2、熟悉 GW48-ES EDA 实验开发系统的基本使用方法。

3、了解 VHDL 文本输入设计方法。

二、实验内容

设计并调试好一个 1 位二进制全加器,并用 GW48-ES EDA 实验开发系

统(拟采用的实验芯片的型号为 EPF10K20TC144-4 或 EP1K30TC144-3)进

行系统仿真、硬件验证。设计 1 位二进制全加器时要求先设计一个或门和一个

1 位二进制半加器,再由或门和 1 位二进制半加器构成 1 位二进制全加器。

三、实验条件

1、开发条件:MAX+plusII

2、实验设备:GW48-ES EDA 实验开发系统、联想电脑

3、拟用芯片:EPF10K20TC144-4 或 EP1K30TC144-3

四、实验设计

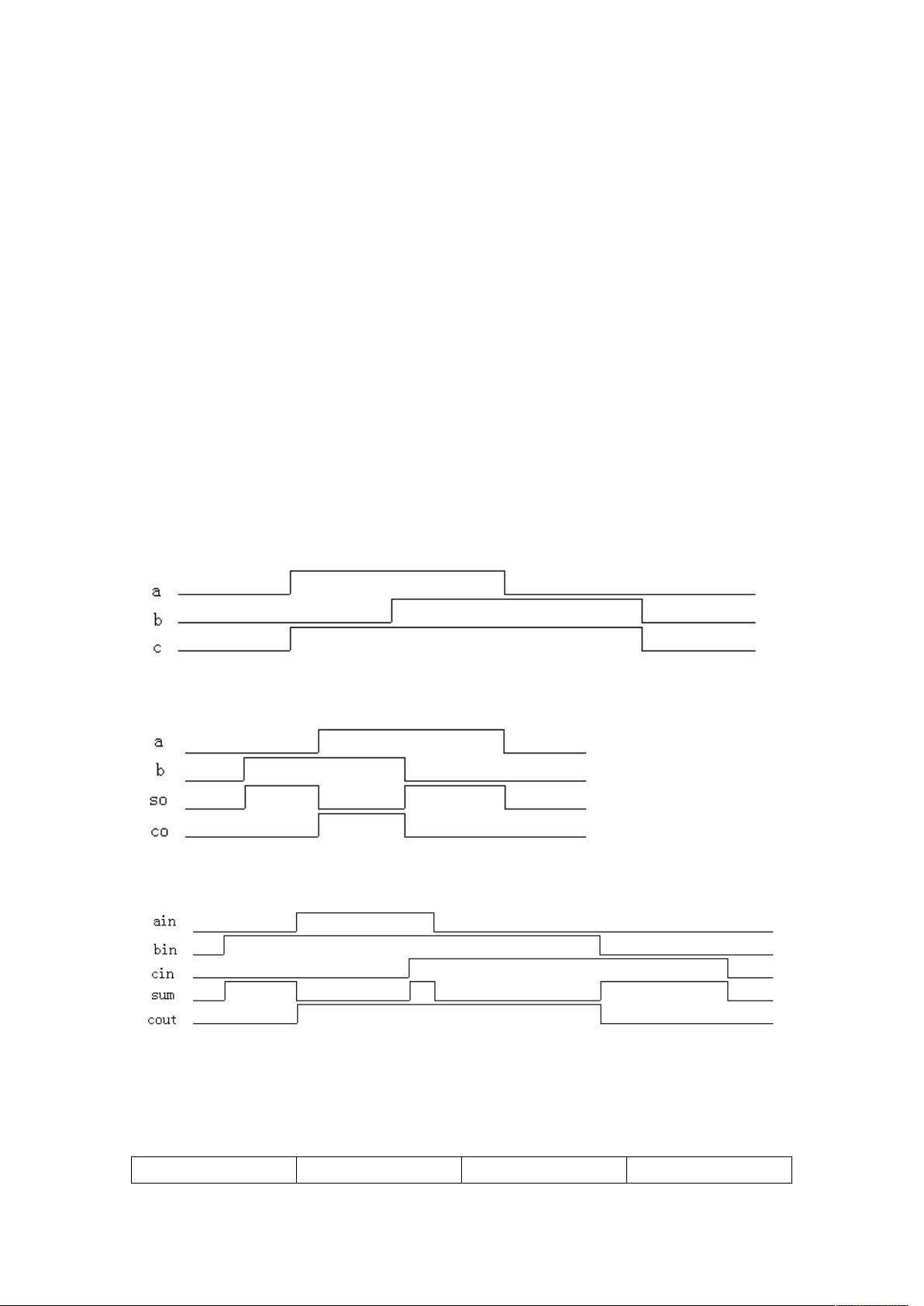

--或门逻辑描述(or2a.vhd)

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE one OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE one;

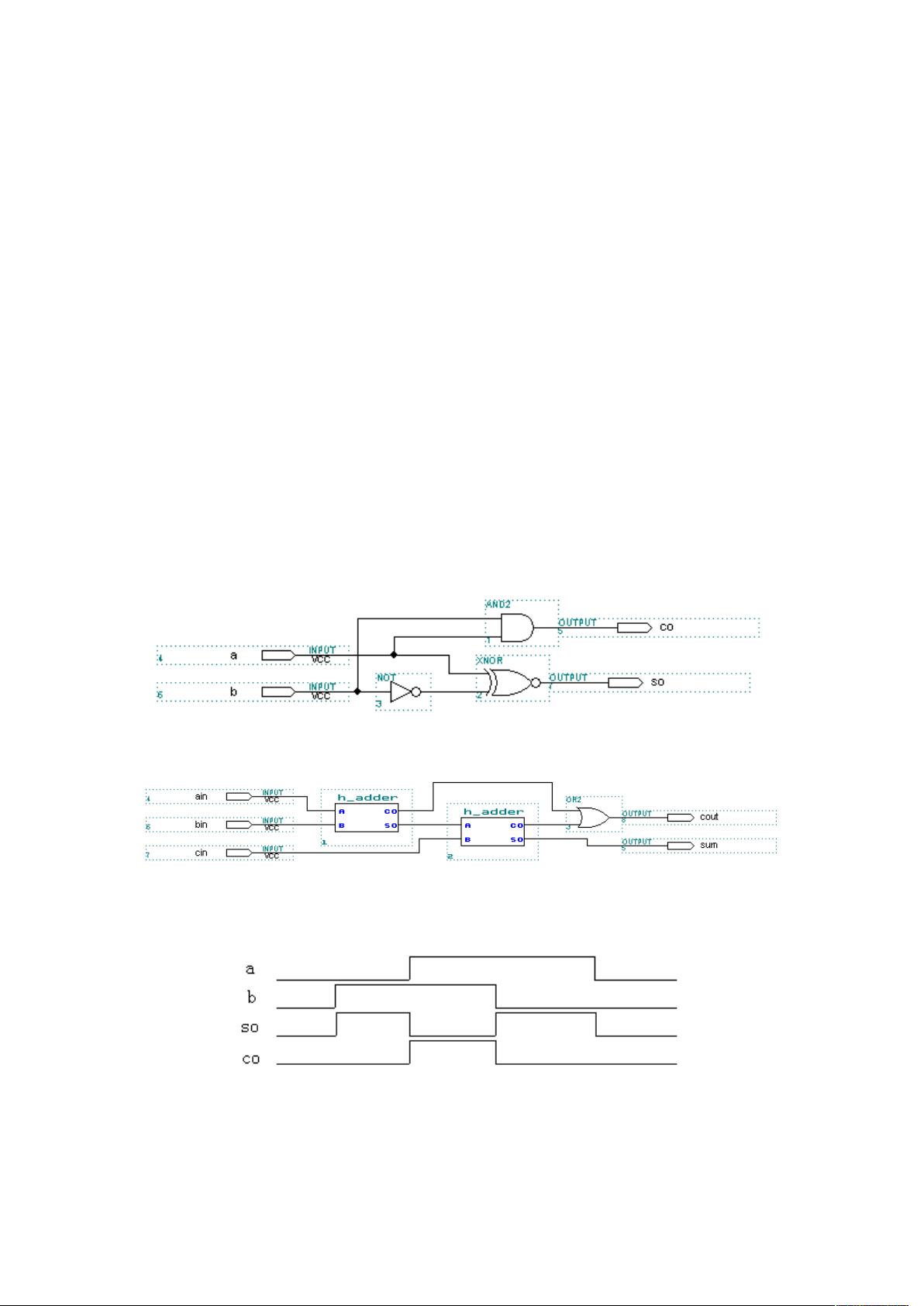

--半加器描述(h_adder.vhd)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY h_adder;

ARCHITECTURE fh1 OF h_adder is

BEGIN

so <= NOT(a XOR (NOT b)) ;

co <= a AND b ;

END ARCHITECTURE fh1;

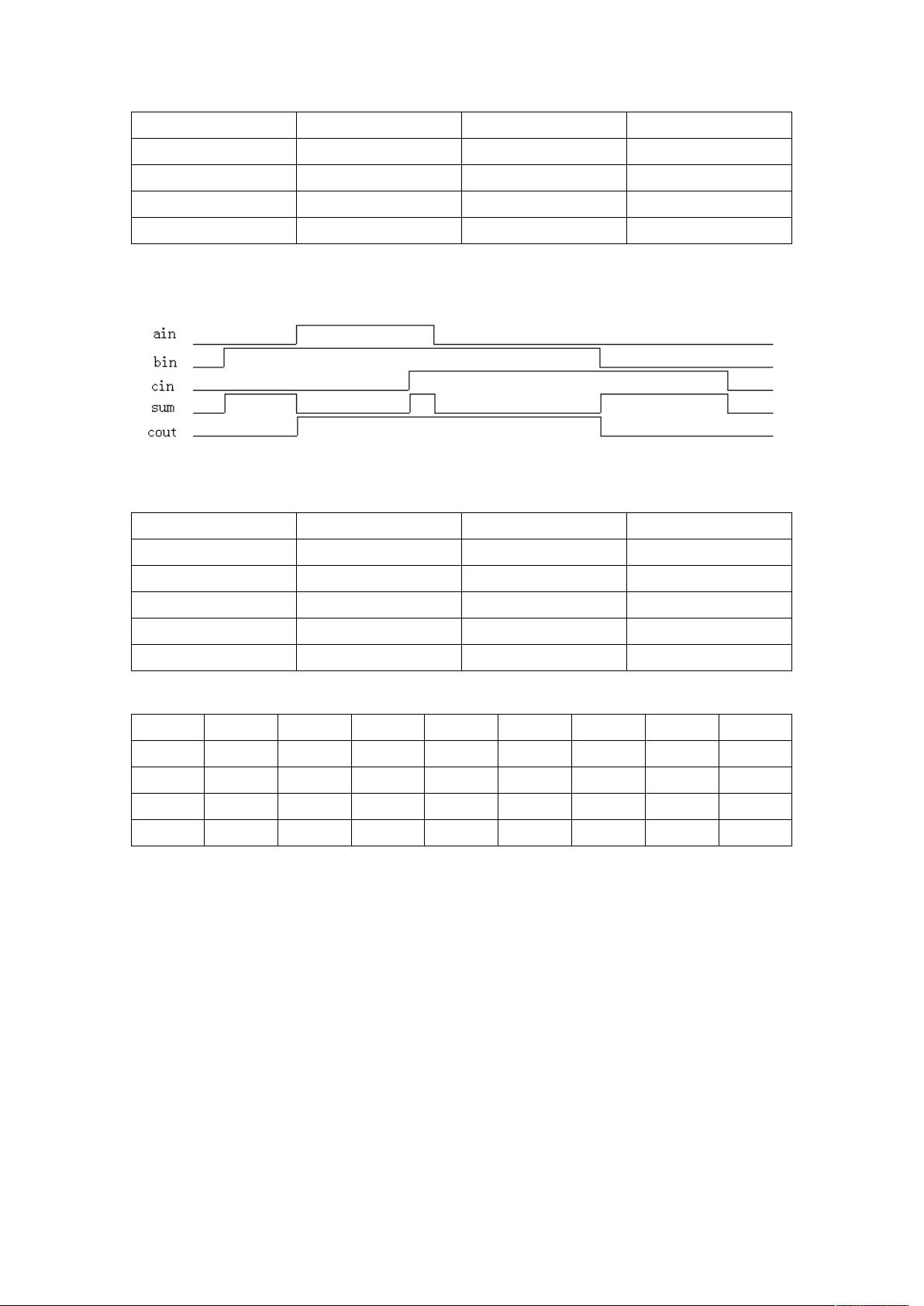

--1 位二进制全加器顶层设计描述(f_adder.vhd)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (ain, bin, cin : IN STD_LOGIC;

评论0