TPS54331:28V输入、3A步降DC-DC转换器,低功耗与高效设计

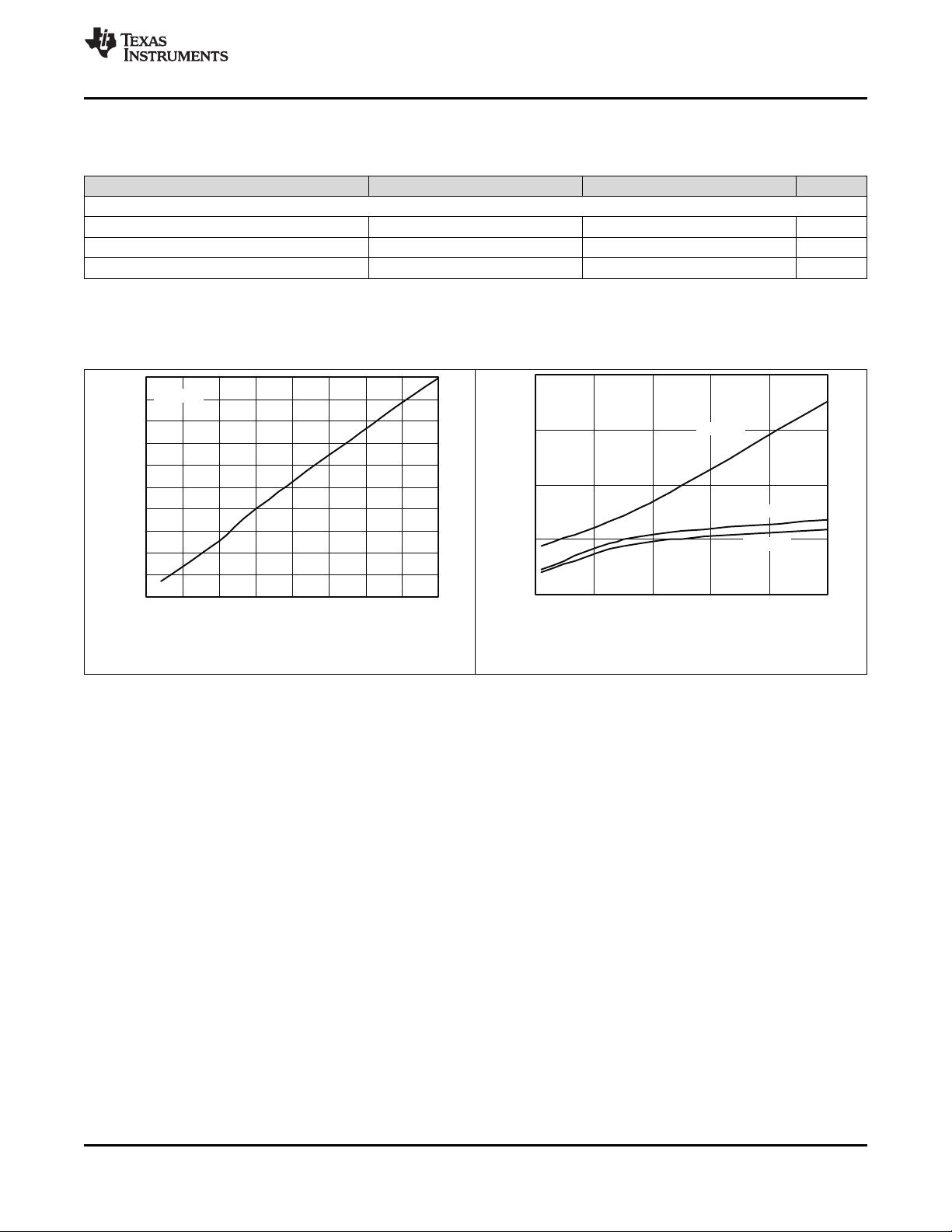

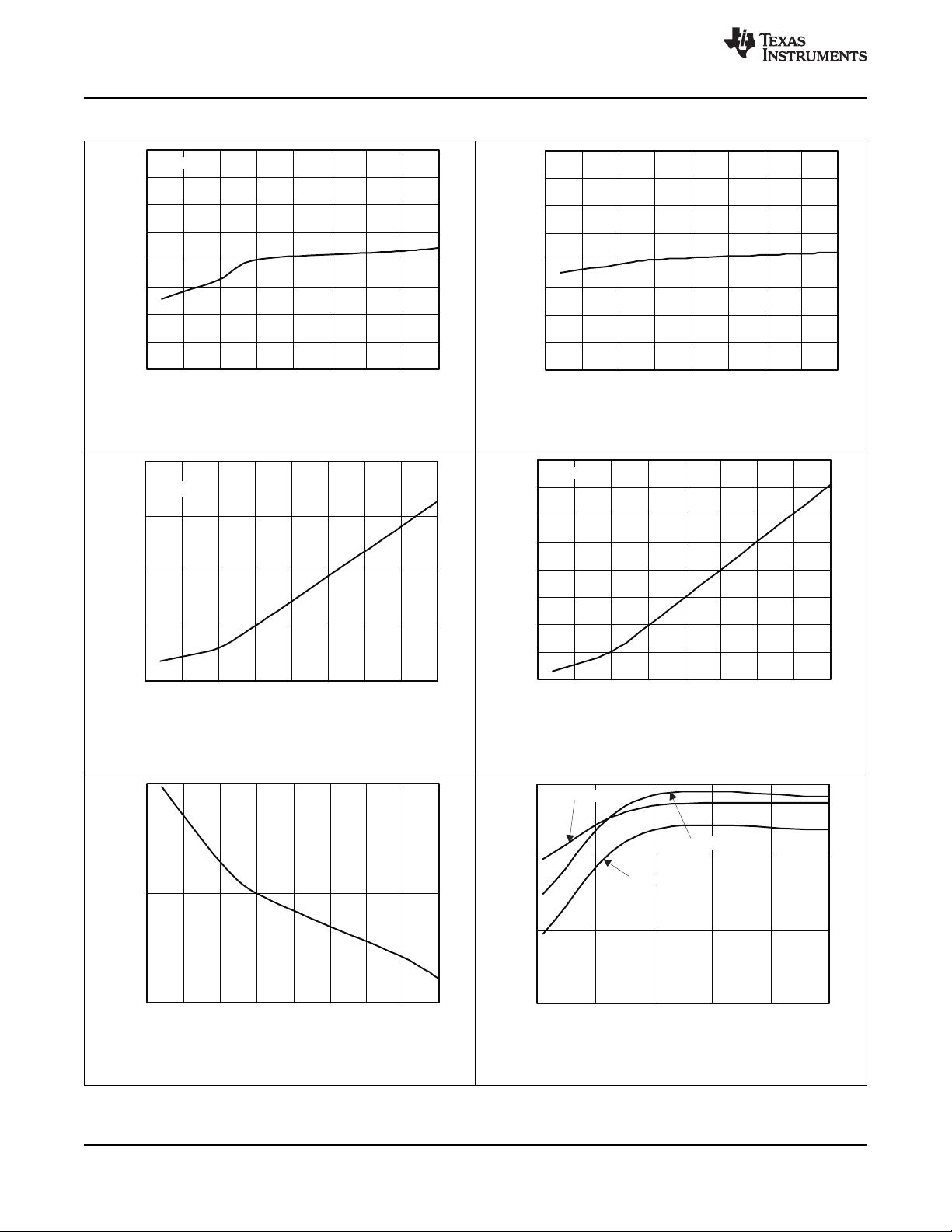

标题:"TPS54331数据手册"详细介绍了TI公司的一款高性能、高效率的28伏输入降压转换器。这款DC-DC转换器的主要特点包括: 1. 宽广的输入电压范围:TPS54331支持3.5至28伏的输入电压,这使得它在各种电源应用中具有很高的灵活性。 2. 低待机电流:典型情况下,该器件的待机模式下静态电流极低,仅为1微安,这在电池供电的应用中尤为重要,可以显著延长设备的电池寿命。 3. 可编程过电压低阈值(UVLO):通过编程,用户可以根据需要设置适当的阈值,以确保电路安全并防止过电压损害。 4. 周期性负载限制与节能模式:采用频率折返的周期性电流限制机制,当负载电流低于预设阈值时,会自动进入“Eco-mode”,在轻载条件下提供更高的能效,并减少不必要的功率损耗。 5. 内置高侧MOSFET:集成的80毫欧姆高侧MOSFET有助于降低开关损耗,提高整体转换效率,特别适合于轻负载或脉冲工作环境。 6. 简单控制:电流模式控制配合内部斜坡补偿,使得设计过程更加简化,易于实现稳定和高效的系统性能。 7. 多种功能集于一体:该产品集成了一个低阻抗高侧MOSFET,以及完整的保护功能,如热过载保护,确保了系统的可靠性和稳定性。 8. 电源引脚:包括VIN、GND、BOOT、VSENSE、COMP、SS、CSS等,满足不同功能的需求。 9. 文档资源:手册提供了丰富的技术文档、工具软件、支持服务和社区资源,便于用户理解和使用该器件。 总体来说,TPS54331是一款高效、灵活且易于使用的DC-DC转换器,适用于对功率效率有较高要求的工业级和消费类电子设备,特别是那些需要在电池供电或轻负载环境下运行的产品。设计者可以通过合理配置其特性来优化其在特定应用场景中的性能。

剩余35页未读,继续阅读

信息提交成功

信息提交成功