没有合适的资源?快使用搜索试试~ 我知道了~

首页IT6801FN 手册

IT6801FN 手册

IT6801FN 数据手册 IT6801FN 数据手册 IT6801FN 数据手册

资源详情

资源评论

资源推荐

www.ite.com.tw T8720F V0.7.1

DEC-2014 Rev:0.96 1/44

IT6801FN

Single-port MHL2.1/HDMI1.4 Receiver with 3D Support

Preliminary Datasheet

ITE TECH. INC.

IT6801FN

www.ite.com.tw T8720F V0.7.1

DEC-2014 Rev:0.96 2/44

General Description

The IT6801FN is a single-port HDMI receiver which can operate in both HDMI1.4 and MHL2.1 dual

mode, it is fully compatible with MHL2.1, HDMI 1.4b, HDMI 1.4b 3D and HDCP 1.4 and also backward

compatible to DVI 1.0 specifications. The IT6801FN with its Deep Color capability (up to 36-bit)

ensures robust reception of high-quality uncompressed video content. The IT6801FN also supports all

the primary 3D formats which are compliant with the HDMI 1.4b 3D specification.

Aside from the various video output formats supported, the IT6801FN also receives and provides up to

4 channels of I

2

S digital audio outputs, with sampling rate up to 192kHz and sample size up to 24 bits,

facilitating direct connection to industry-standard low-cost audio DACs. Also, an S/PDIF output is

provided to support up to compressed audio of 192kHz frame rate.

Each IT6801FN comes preprogrammed with an unique HDCP key, in compliance with the HDCP 1.4

standard so as to provide secure transmission of high-definition content. Users of the IT6801FN need

not purchase any HDCP keys or ROMs.

Features

Single-port MHL2.1/HDMI 1.4b receiver.

Support MHL2.1, HDMI1.4b dual mode input.

MHL/HDMI mode auto detection.

MHL RCP command to HDMI CEC interactive translation.

Compliant with MHL2.1, HDMI 1.4b, HDMI 1.4b 3D, HDCP 1.4 and DVI 1.0 specifications

Supporting link speeds of up to 3.0Gbps (link clock rate of 300MHz) for 4K2K or 1080p@120hz

solution. And up to 1080p@60hz on MHL packed pixel mode.

Supporting all the primary 3D formats which are compliant with the HDMI 1.4b 3D specification.

Supporting 3D video up to 1080P@50/59.95/60/120Hz, 1080P@23.98/24/29.97/30Hz,

1080i@50/59.94/60/Hz, 720P@23.98/24/29.97/30Hz, 720P@50/59.94/60Hz

Supporting formats: Framing Packing, Side-by-Side (half), Top-and-Bottom.

Video output interface supporting digital video standards such as:

24-bit RGB/YCbCr 4:4:4

16-bit YCbCr 4:2:2

8-bit YCbCr 4:2:2 (ITU BT-656)

24-bit double data rate interface (full bus width, pixel clock rate halved, clocked with both rising

and falling edges)

Input channel swap

IT6801FN

www.ite.com.tw T8720F V0.7.1

DEC-2014 Rev:0.96 3/44

Bi-direction Color Space Conversion (CSC) between RGB and YCbCr color spaces with

programmable coefficients.

Up/down sampling between YCbCr 4:4:4 and YCbCr 4:2:2

Dithering for conversion from 12-bit component to 8-bit

Digital audio output interface supporting

up to two I

2

S interface supporting 4-channel audio, with sample rates of 32~192 kHz and

sample sizes of 16~24 bits

S/PDIF interface supporting PCM, Dolby Digital, DTS digital audio at up to 192kHz frame rate

automatic audio error detection for programmable soft mute, preventing annoying harsh output

sound due to audio error or hot-unplug

Auto-calibrated input termination impedance provides process-, voltage- and temperature-invariant

matching to the input transmission lines.

Integrated pre-programmed HDCP keys

Integrated programmable EDID RAM

Intelligent, programmable power management

76-pin QFN (9mm x 9mm) package

RoHS Compliant ( 100% Green available )

Ordering Information

Model

Temperature Range

Package Type

Green/Pb free Option

IT6801FN

-20~70

76-pin QFN

Green

IT6801FN

www.ite.com.tw T8720F V0.7.1

DEC-2014 Rev:0.96 4/44

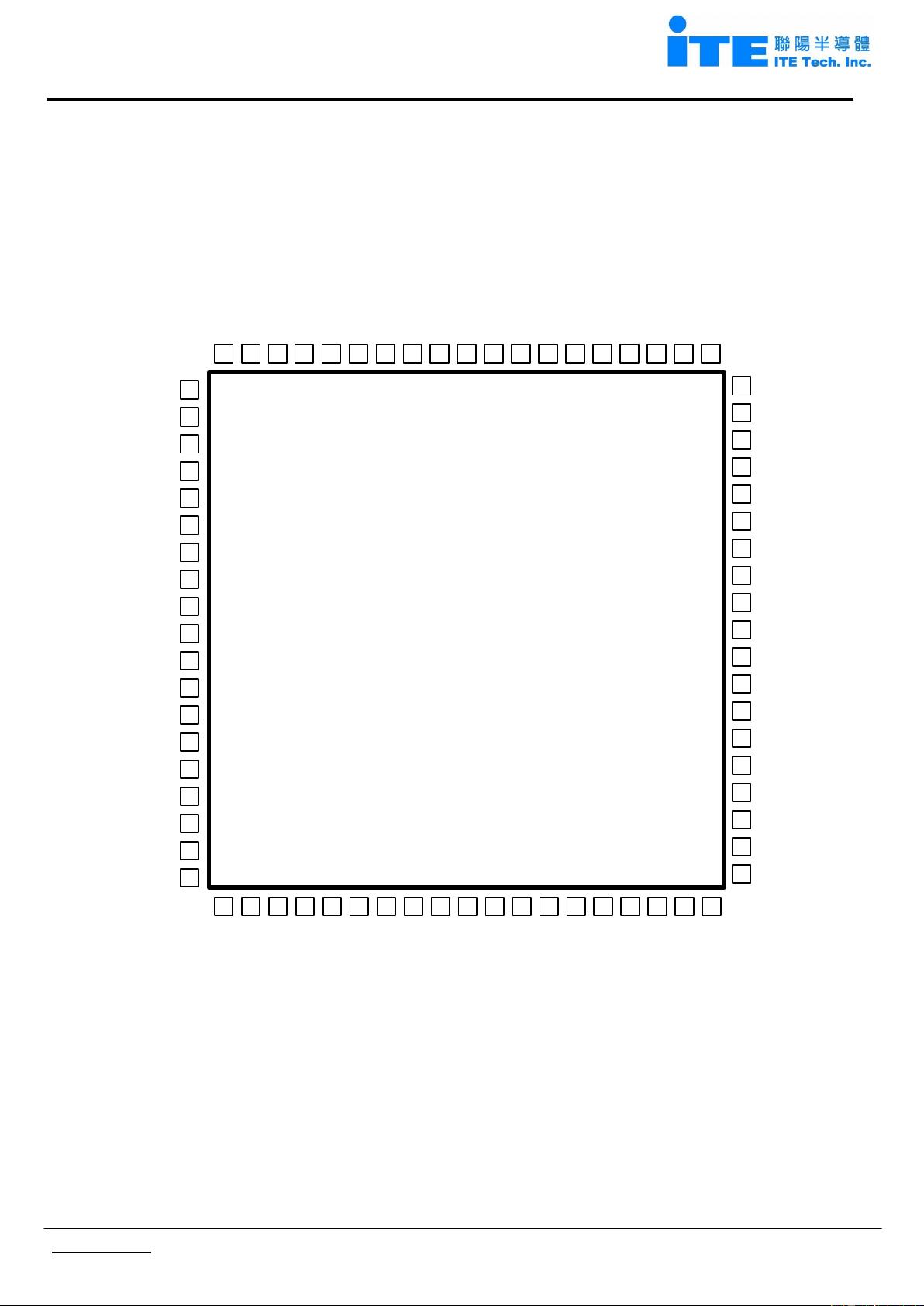

Pin Diagram

1

QE9

2

QE8

3

4

PCLK

5

6

QE7

7

QE6

8

QE5

9

QE4

10

11

12

13

14

OVDD

15

16

17

DE

18

HSYNC

19

VSYNC

IVDD12

OVDD33

INT#_CEC

PCSDA

20

CBUS/HPD

P0_RXCN

P0_RXCP

212223

AVCC33

P0_RX0N

P0_RX0P

242526

P0_RX1N

272829

P0_RX1P

DVDD12

303132

P0_RX2N

P0_RX2P

33343536

APVDD12

XTALOUT

XTALIN

APVCC33

MUTE_MCLK

39

40

I2S0

41

IVDD12

42

I2S1_3DR

43

44

45

WS_SPDIF

46

SCK_MCLK

47

48

49

50

QE10

QE11

IVDD12

OVDD

QE16

QE17

QE18

QE19

IVDD12

QE20

76

QE21

75

QE22

OVDD

74737271

QE23

7069

PCSCL

DDCSDA0

DDCSCL0

R0PWR5V

IVDD12

CDSENSE

3738

PVCC12

51

SYSRSTN

52

IVDD12

53

54

55

56

PCADR

57

OVDD

QE35

QE34

QE33

68676665

QE28

64

QE29

6362

QE30

6160

QE31

59

QE32

58

IT6801

MHL/HDMI RX

QFN-76 9x9

(Top View)

AVCC12

AVCC33

ENVBUS#

OVDD

OVDD

AVCC33

PVCC33

Figure 1. IT6801FN pin diagram

Note:

1. Pins marked with NC should be left unconnected.

IT6801FN

www.ite.com.tw T8720F V0.7.1

DEC-2014 Rev:0.96 5/44

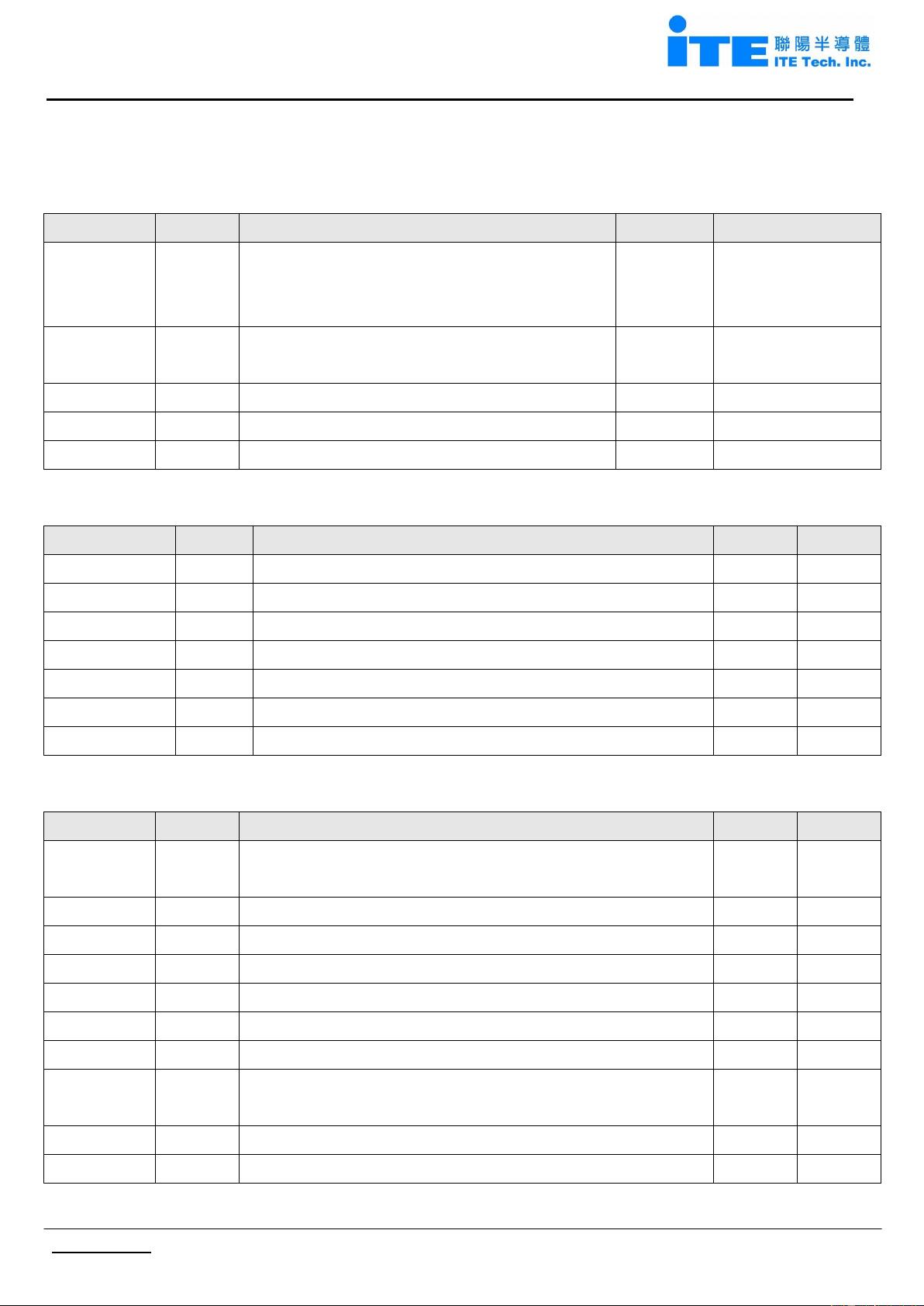

Pin Description

Digital Video Output Pins

Pin Name

Direction

Description

Type

Pin No.

QE[35:28]

QE[23:16]

QE[11:4]

Output

Digital Video Output Pins. Channel swap are

supported through register setting.

LVTTL

1-5, 51-54, 56-62,

65-69, 72-74

PCLK

Output

Output data clock. The backend controller should

use the rising edge of PCLK to strobe QE Data.

LVTTL

75

DE

Output

Data enable

LVTTL

8

HSYNC

Output

Horizontal sync. signal

LVTTL

9

VSYNC

Output

Vertical sync. signal

LVTTL

10

Digital Audio Output Pins

Pin Name

Direction

Description

Type

Pin No.

XTALIN

Input

Crystal clock input (for Audio PLL)

LVTTL

39

XTALOUT

Output

Crystal clock output (for Audio PLL)

LVTTL

38

MCLK_MUTE

Output

Audio master clock, doubles as Mute output

LVTTL

41

SCK_MCLK

Output

I2S serial clock output, doubles as audio master clock output

LVTTL

46

WS_SPDIF

Output

I2S word select output, doubles as S/PDIF audio output

LVTTL

45

I2S0

Output

I2S serial data output

LVTTL

42

I2S1_3DR

Output

I2S serial data output, doubles as doubles as 3D R/L signal

LVTTL

44

Programming Pins

Pin Name

Direction

Description

Type

Pin No.

INT#_CEC

Output

Interrupt output. Default active-low (5V-tolerant), doubles as CEC

function I/O (5V-tolerant)

LVTTL

12

SYSRSTN

Input

Hardware reset pin. Active LOW

Schmitt

47

DDCSCL0

I/O

DDC I2C Clock for HDMI Port 0 (5V-tolerant)

Schmitt

17

DDCSDA0

I/O

DDC I2C Data for HDMI Port 0 (5V-tolerant)

Schmitt

16

R0PWR5V

Input

TMDS transmitter detection for Port 0(5V-tolerant)

LVTTL

18

PCSCL

Input

Serial Programming Clock for chip programming (5V-tolerant)

Schmitt

14

PCSDA

I/O

Serial Programming Data for chip programming (5V-tolerant)

Schmitt

13

PCADR

Input

Serial Programming device address select. Device address is

0x90 when PCADR is pulled low, 0x92 otherwise

LVTTL

49

CDSENSE

Input

This pin is used to detect MHL connection (5V-tolerant)

LVTTL

19

CBUS/HPD

I/O

In MHL mode this pin is the Control Bus signal. The CBUS

LVTTL

21

剩余43页未读,继续阅读

shao15232_1

- 粉丝: 97

- 资源: 10

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论3