深入理解ARMv8架构与指令集分析

"该资源是一份关于ARMv8架构与指令集的学习笔记,涵盖了ARMv8的基本概念、执行状态、异常级别、寄存器结构、异常模型以及指令集的详细解析,旨在帮助读者深入理解这一现代处理器架构的核心要素。"

在深入探讨ARMv8架构之前,首先要理解其基础认识。ARMv8是ARM公司推出的64位架构,它扩展了传统的32位ARM(Advanced RISC Machines)架构,引入了名为AArch64的64位执行状态,同时保留了原有的32位执行状态(ARM和 Thumb 指令集)。ARMv8架构不仅增强了性能,还提高了能效,广泛应用于移动设备、服务器和嵌入式系统。

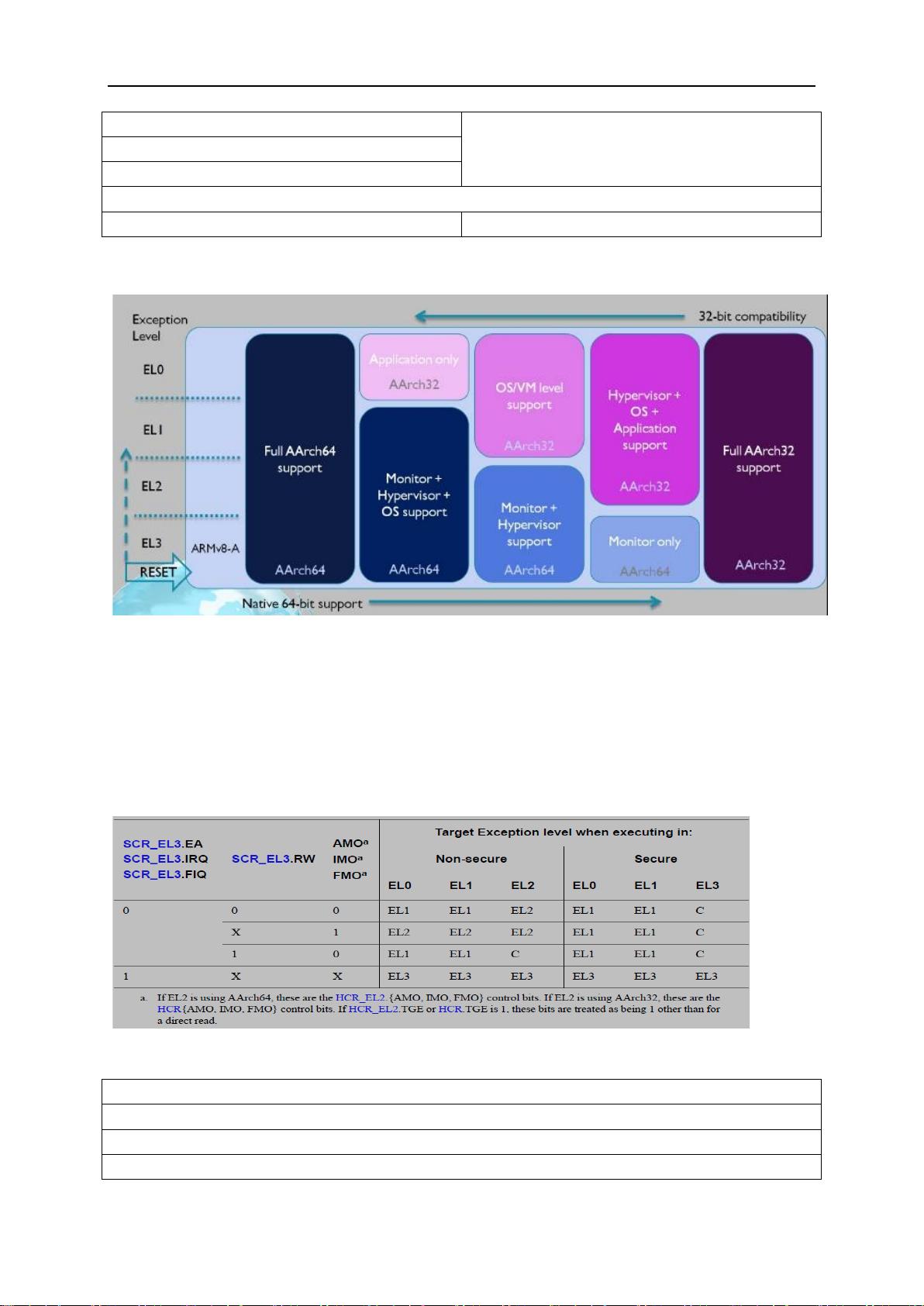

执行状态(Execution State)是ARMv8的一个关键概念,包括AArch32和AArch64。AArch32支持传统的32位ARM指令集,而AArch64则为64位指令集,提供了更高效的内存访问和计算能力。执行状态的选择通常取决于操作系统和应用的需求,可以在运行时切换。

异常级别(Exception Level, EL)是ARMv8异常模型的核心部分,用于管理不同安全级别的执行环境。EL3是最高的异常级别,通常用于安全监控或虚拟化环境,而EL0和EL1分别对应用户模式和操作系统内核模式。EL3在AArch64下通常使用64位模式,而在AArch32下可以是32位或64位。

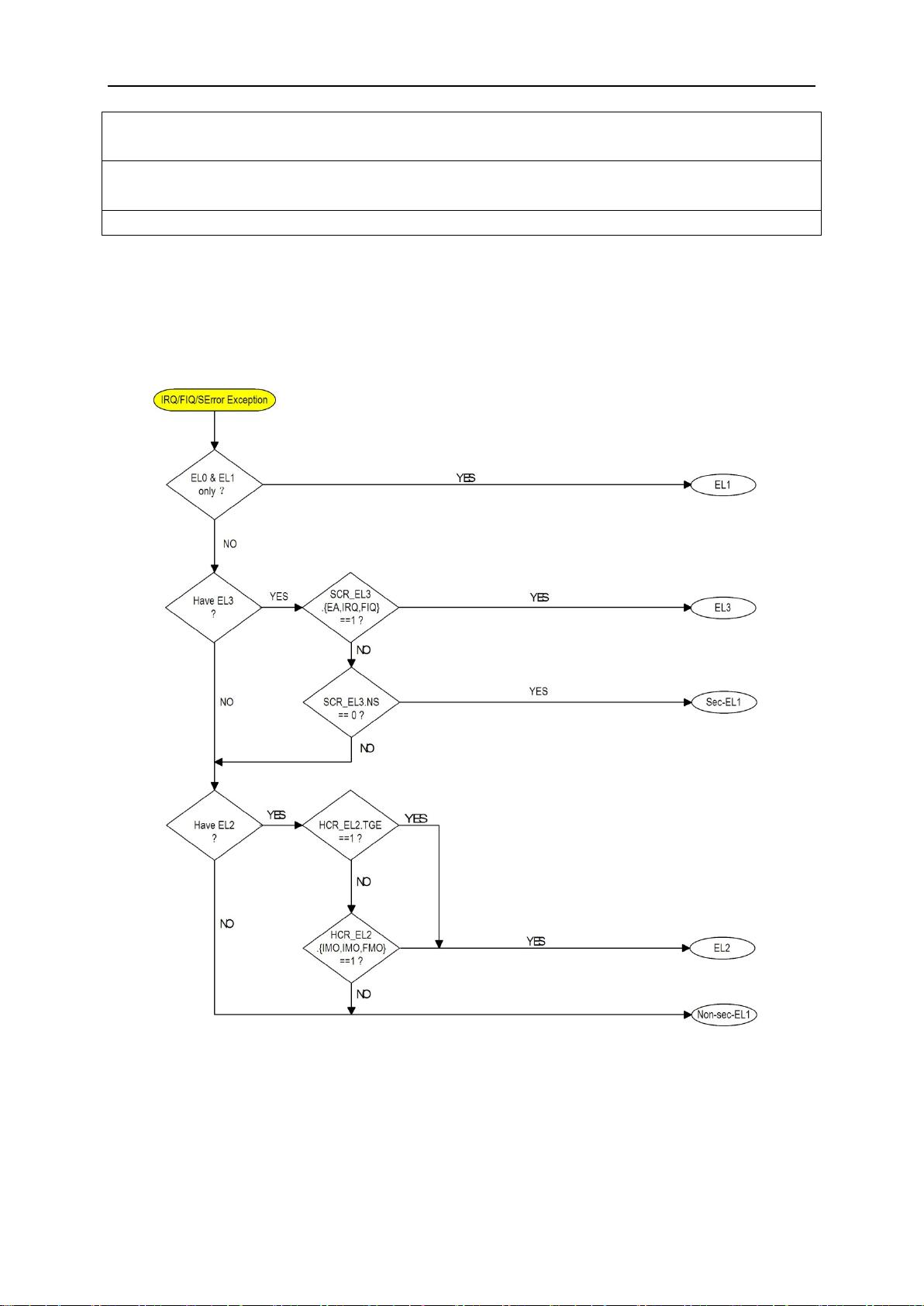

异常处理逻辑是ARMv8架构中的另一个重点,包括不同类型异常的识别(如IRQ中断、FIQ快速中断、数据abort等)以及相应的处理流程。异常发生时,处理器会保存当前执行状态,切换到适当的异常级别,并根据路由规则来决定如何响应异常。路由规则定义了异常如何从一个执行状态转移到另一个状态,以及如何处理中断和快速中断。

寄存器是处理器执行指令的基础,ARMv8架构有多种类型的寄存器,包括通用寄存器、浮点寄存器、系统寄存器等。在AArch32状态下,寄存器组织与传统的ARM指令集相似,而在AArch64状态下,寄存器数量增加,提供了更高的并行处理能力。

ARMv8指令集包括A64和A32/T32两部分。A64指令集是专门为64位环境设计的,具有简洁的指令格式和丰富的指令种类,如数据处理、加载/存储、跳转、异常产生和返回等。A32和T32指令集则用于32位环境,T32是一种更紧凑的变体,适用于减少代码大小。

这份学习笔记详尽地介绍了ARMv8架构的各个方面,从基础概念到高级特性,对于开发者和系统设计人员来说,是一份宝贵的参考资料,可以帮助他们理解和利用这一强大的处理器架构。

2016-12-29 上传

2020-03-21 上传

2023-06-25 上传

2023-08-18 上传

2019-08-08 上传

2008-03-04 上传

2017-07-10 上传

2022-03-29 上传

你必须十分努力,才能看起来毫不费力

- 粉丝: 720

- 资源: 2

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析