北京大学微处理器中心:现代指令级并行技术与流水线优化

需积分: 0 31 浏览量

更新于2024-06-30

收藏 2.54MB PDF 举报

本课程是北京大学微处理器研究开发中心计算机系统结构研究所于2014年4月21日开设的高级计算机系统结构课程,由程旭教授主讲,主题为现代指令级并行技术。课程重点讨论了流水线在提高处理器性能中的关键作用以及其中涉及的技术策略。

首先,流水线的性能优化是课程的核心内容之一。通过设计更为复杂的流水线和动态调度,处理器可以实现隐式指令级并行性,即在不显式地增加指令数量的情况下,提高并发执行能力。这种并行性有助于提升吞吐量,但同时也需要解决数据相关性问题,如真数据相关(RAW)和写后读(WAR/WAW)冒险。为确保程序正确性,处理器利用重排序缓冲器保存已完成但未提交的结果,以及提供精确中断支持。

控制冒险,特别是由于频繁的转移指令引起的,是限制流水线性能的关键因素。这些转移可能导致指令顺序混乱,影响整体执行效率。处理这种情况通常涉及到异常处理机制,例如kill操作和注入处理程序的PC地址。

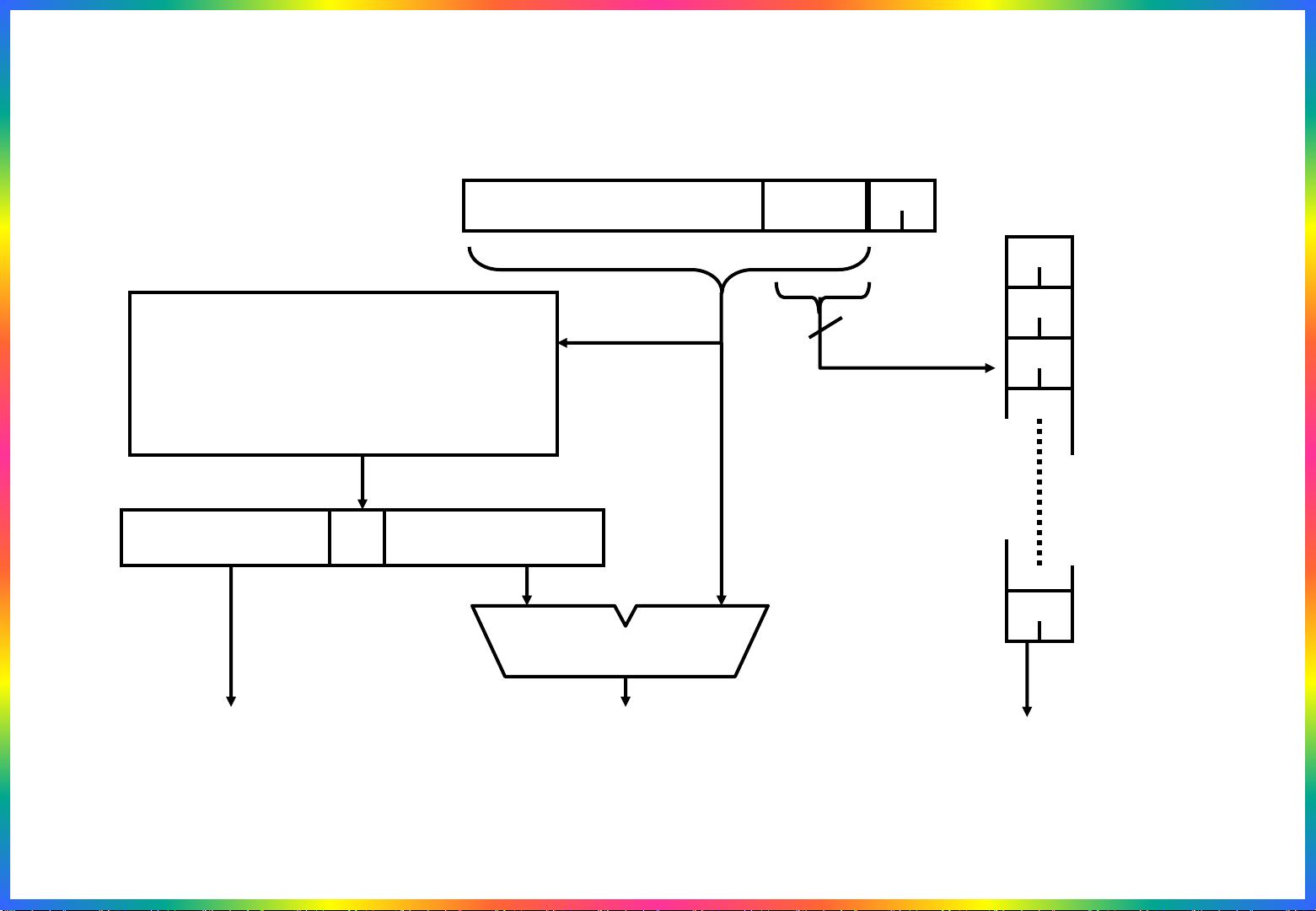

在硬件层面,课程介绍了指令流水线的总体结构,包括取指、译码、执行、提交等阶段,以及它们之间的交互。例如,取指和译码阶段是顺序进行的,而执行则允许乱序,即指令可能在不同时间完成。为了管理这些并行性,需要使用临时存储(如影子寄存器和存储缓冲器)来协调状态。

此外,课程还关注了指令缓存(I-cache)的作用,它作为高速缓冲器,缩短了从内存获取指令的时间。课程强调了控制流对性能的影响,尤其是在现代处理器中,分支延迟可能占用多个流水级,这可能导致循环展开和宽度(loop length与pipeline width)之间的权衡。

最后,MIPS架构下的转移和跳转指令在指令取指过程中存在依赖性,这意味着每条指令的执行都会受到前一条指令结果的影响。这种特性要求处理器在执行时必须考虑控制流的不确定性,以减少性能损失。

该课程深入探讨了现代计算机系统结构中的高级技术,从流水线设计到数据相关性管理,以及如何通过优化控制流处理来提升处理器性能。这对于理解计算机系统的内部工作原理和优化策略具有重要的理论价值和实践指导意义。

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-03 上传

2022-08-04 上传

点击了解资源详情

KerstinTongxi

- 粉丝: 26

- 资源: 277

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能