没有合适的资源?快使用搜索试试~ 我知道了~

首页Vivado HLS教程.pdf

Vivado HLS教程.pdf

需积分: 42 74 下载量 117 浏览量

更新于2023-05-05

评论 3

收藏 14.49MB PDF 举报

关于用vivado进行HLS开发的资料,其中有笔记对应的视频链接,可以配套视频进行学习,属于个人学习资料,不喜勿喷

资源详情

资源评论

资源推荐

Vivado HLS 教程

参考视频:https://www.bilibili.com/video/av41246874?p=1

参考文章:https://zhuanlan.zhihu.com/p/65619926

Chapter1 软件工程师该怎么了解 FPGA 架构

⚫ 对于一个软件工程师,应该掌握的程度:

1. FPGA 内部每个单元的功能;

2. 具体的算法操作和每个单元之间的对应关系;

3. 算法模型中资源的利用率;

4. 算法模型的优化方法;

⚫ CPU、DSP、GPU、FPGA 对比:

◼ CPU:运算不行,擅长管理和调度,比如读取数据、管理文件、人机交互等,例程多,辅助工具也多

◼ DSP:相比之下管理变弱,运算加强。CPU 和 DSP 都是靠高主频来解决运算量的问题,适合有大量递归操作以及不

便拆分的算法

◼ GPU:管理更弱,运算更强,多进程并发,更适合整块数据进行流处理的算法

◼ FPGA:能管理能运算,但开发周期长,复杂算法开发难度大。适合流处理算法,不管是整块数据进入还是一个一个进

入,以及实时性来说,FPGA 是最高的。

▪ 前三种处理器,为了避免将运算能力浪费在数据搬运上,一般要求累计一定量数据之后才开始计算,产生群延时,而

FPGA 所有操作都并行,因此群延时可以很小

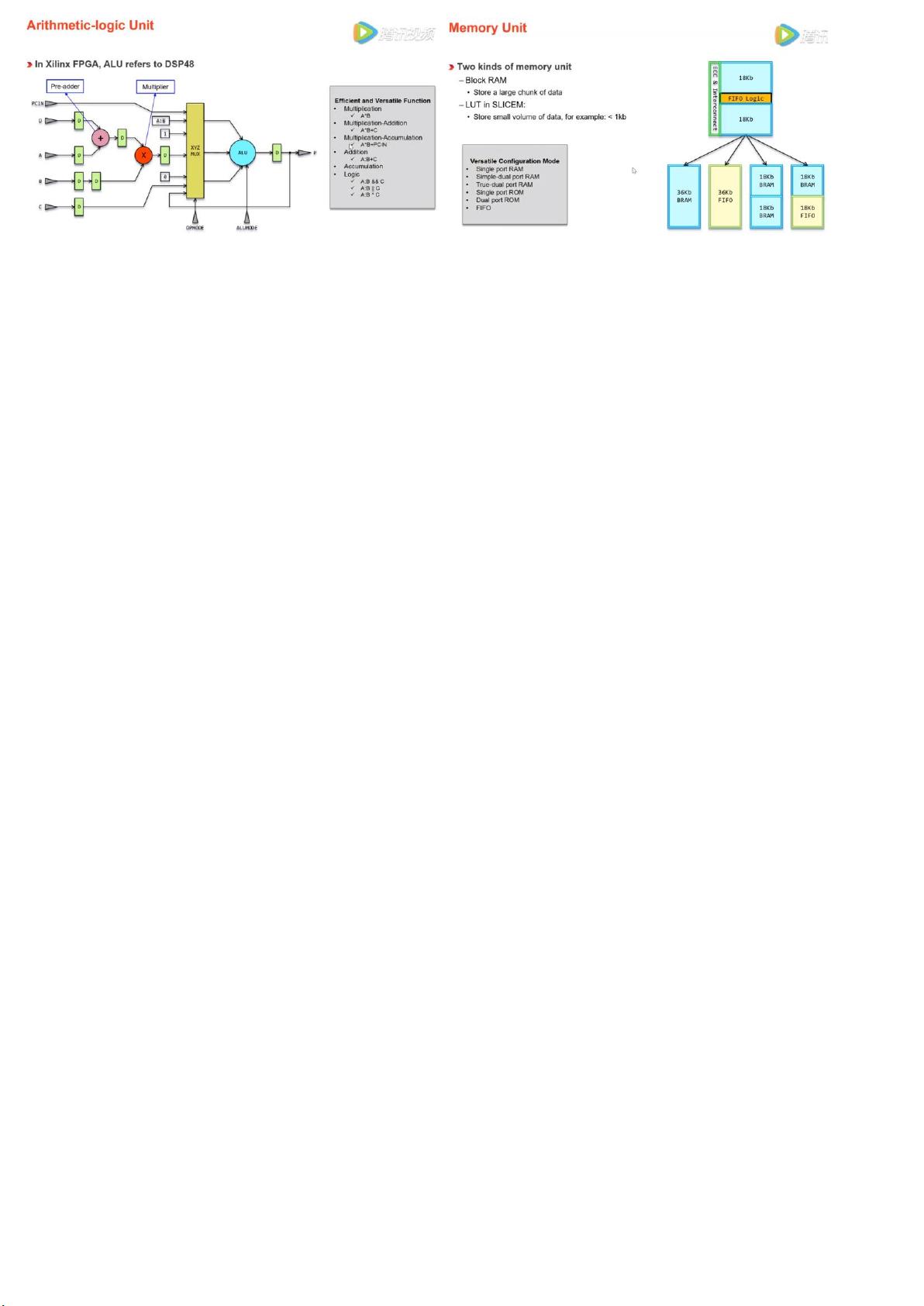

⚫ 两种存储单元

◼ Block RAM:存储大块数据

◼ Slice 中的 LUT:存储小批量的数据

⚫ 用 C/C++做算法开发应该集中于

◼ 每个 unit 的功能

◼ 每个 unit 和操作的关联

◼ 算法模型所使用的 unit

◼ 不需要关注每个 unit、ALU、存储单元的细节结构

Chapter2 vivado HLS 工作原理

⚫ ESL(Electronic System Level)发展过程:CAD(Computer Aided Design) → CAE(Computer Aided Engineering) →

EDA(Electronic Design Automation)

◼ 在 EDA 这个阶段,最典型的特征就是出现了硬件描述语言——VHDL 和 Verilog;

◼ 到了现在,就出现了 ESL(电子系统级设计方法)这个概念,它的本质是在说在 ESL 这个阶段我们希望采用具有更高

抽象度的方式去描述系统行为,所以在这个阶段有两个显著特征:

1、使用高级语言(例如 C 或者 C++), XILINX 有 Vivado HLS 这个工具;

2、使用基于模型的设计工具——System Generator;

⚫ High-level Synthesis Benefits

1、对于硬件工程师,提高项目效率,不需要考虑并行性和时序的问题,直接在算法级考虑优化;

2、对于软件工程师,可以提高系统性能,原来需要 CPU、GPU 或者 DSP 才能实现的算法现在都可以通过 FPGA 来实现,

一方面提高了吞吐率,另一方面也改善了功耗;

3、在 C/C++这个层面开发算法并且验证;

4、通过优化工具来高效指导转化过程;

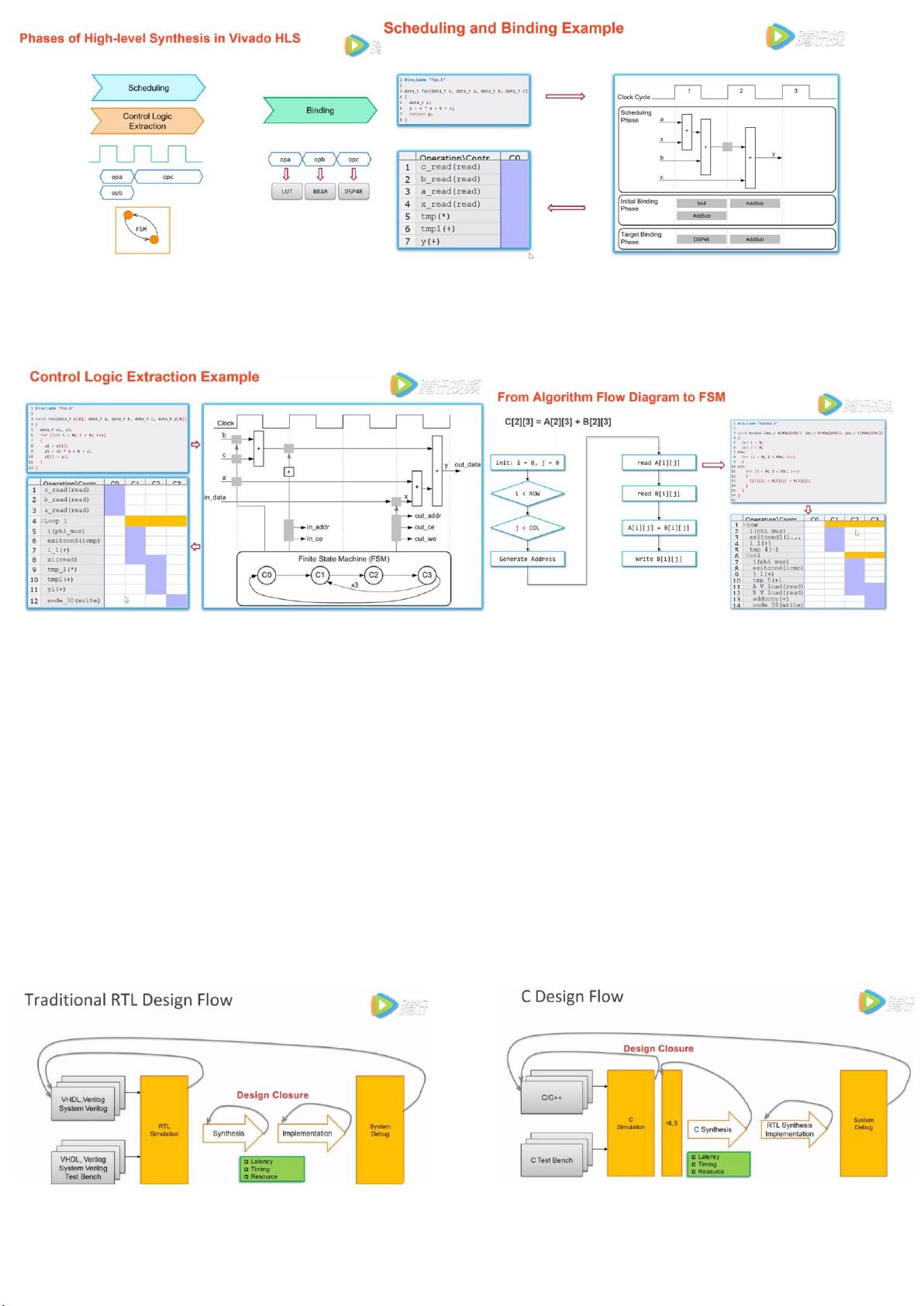

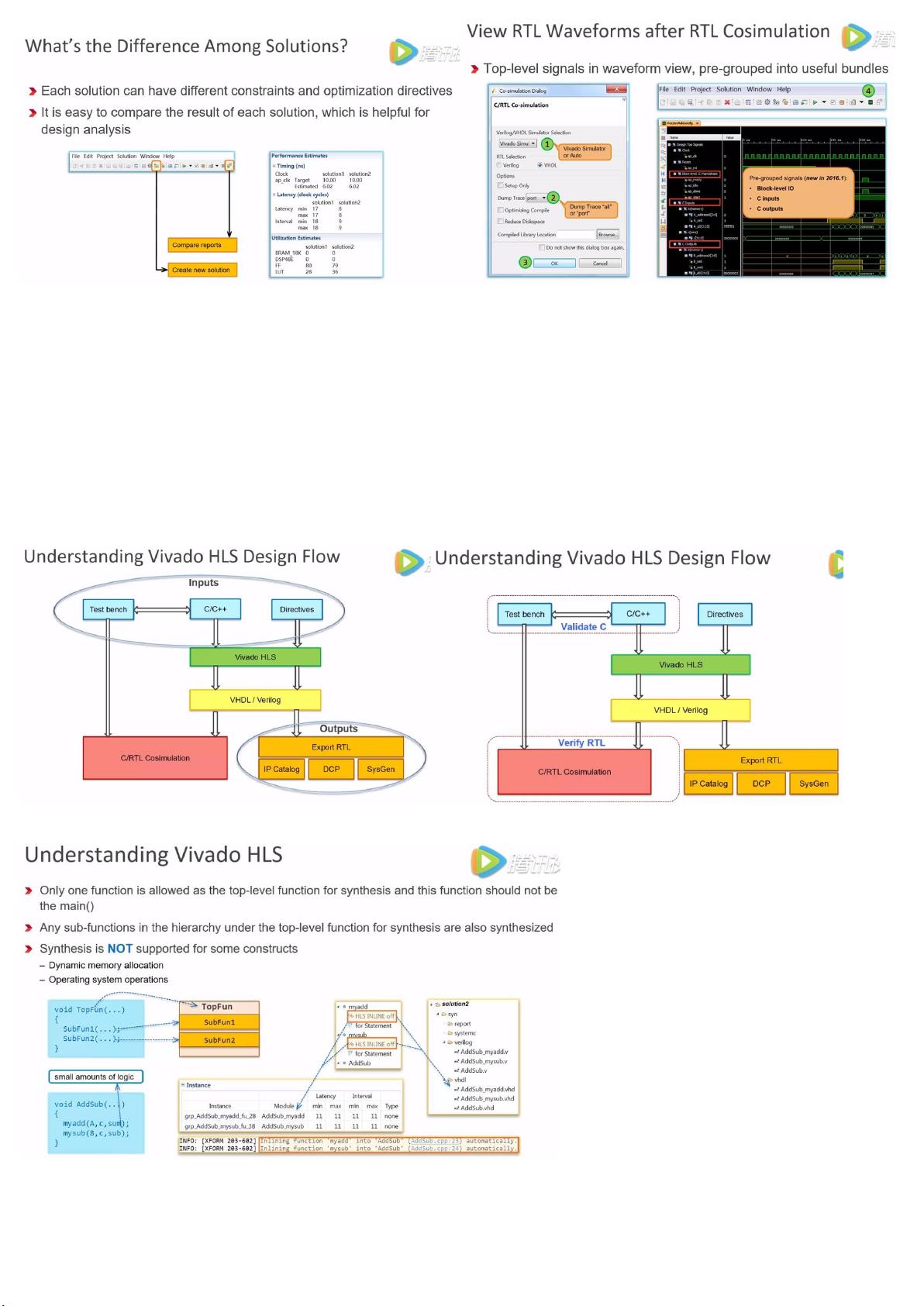

Vivado HLS 综合原理

⚫ 流程:

◼ Scheduling:确定每个时钟周期应该做什么操作,同时这个操作大概需要几个时钟周期完成,以及是否可以并行执行;

◼ Control Logic Extraction:控制逻辑的提取通常会生成一个状态机,这个可以在 HDL 代码中看到;

◼ Binding:确定每个操作需要用什么资源去实现,完成这样的一个从操作到资源映射过程;

⚫ 控制逻辑的提取例子,有四个状态,在 C0 状态执行 b+c,C1 状态产生 x 和数组的地址,C2 状态执行相应的乘法操作,C3

状态将结果写入 y 数组的对应位,如此循环几次,直到到达循环边界退出循环。

◼ 采用循环结构之后,会产生 4 个状态,每个状态执行对应的操作。

◼ 需要注意的是,生成的控制状态(左下)和状态机(右下)不是一一对应的,但它们之间非常接近。

⚫ for 循环之前有标注代码(和 C 不同),要加上对模块的特殊说明部分,方便在后续进行 solution 设置和优化

⚫ 总结

◼ Vivado HLS 的三个阶段:

◆ Scheduling

◆ Control logic extraction

◆ Binding

◼ 算法流程图可以帮助分析 HLS 产生的控制状态

◼ 控制状态时 HLS 的内部状态,用来将操作对应到时钟周期

◼ 控制状态 和 RTL 代码中状态机状态 有紧密的对应关系,但并不是一对一的对应。

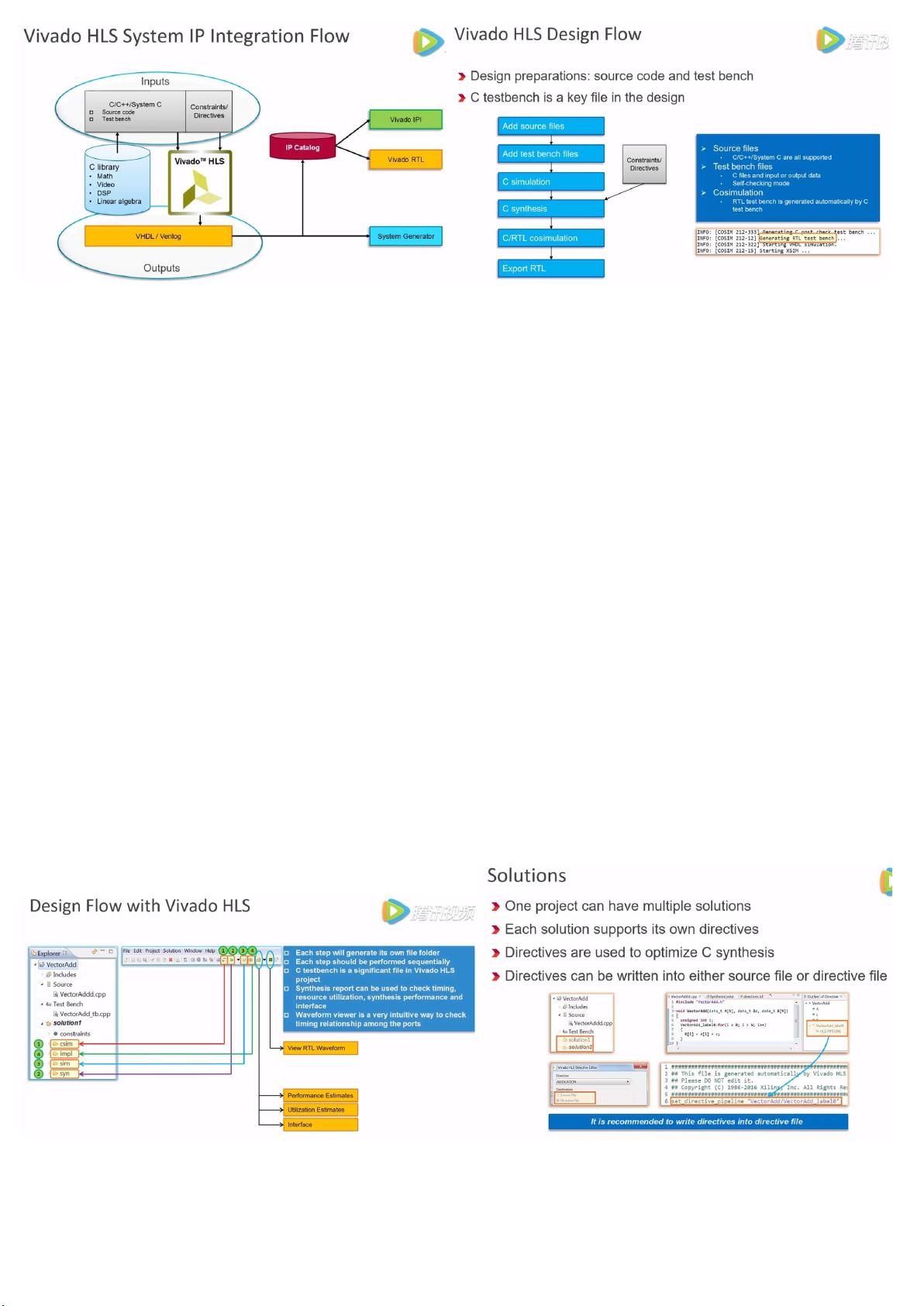

Chapter3 vivado 设计流程介绍

Vivado HLS 综合流程:

⚫ 添加源文件 source file

◼ Vivado HLS 的设计输入包括 Test bench、C/C++和 Directives

⚫ 添加测试文件 testbench file

◼ Test bench 的作用有两点:

* 一是验证 C/C++代码的正确性;

* 二是在与 RTL 的协同仿真阶段,生成用于 RTL 级验证的 Test bench;

⚫ C simulation

⚫ C synthesis

◼ 说明:

* 对于一个工程,只可以有一个顶层的函数用于综合,这个函数下面的子函数也可以被综合,通常情况下 C/C++综

合后的 RTL 代码的结构和原始的 C 函数描述的结构一致(除了子函数所需要的逻辑量很小、算法功能很简单时,

综合阶段不会单独有这个结构,将 HLS INLINE off 关掉时就会完全一致)

* 并不是所有的 C/C++语言风格的代码都能被综合,有两点需要注意:一是动态内存分配,二是操作系统层面;

* 一个 C/C++代码最后映射到 RTL 代码有三大类接口,包括 Block-level IO Handshake(握手信号)、C Inputs、C

Outputs;

⚫ C/RTL Co-simulation

⚫ 导出 RTL

◼ 相应的设计输出有 IP(在 Vivado 的 IP Catalog 中)、DCP(RTL 代码综合后的网表文件)、SysGen(HLS 之后的结果可

以导入 SysGen 中使用)

⚫ 建议:将 directives 写道 directive file 中

⚫ 总结:

◼ Vivado HLS 支持 C,C++,System C

◼ 建议对每个 C 综合设计都 创建一个 C testbench

◼ 为了得到最优的 C 综合结果,可创建多个 solutions

◼ Vivado HLS 可以支持算法加速开发

Good C Coding Style + Good Directives = Optimal Results

Chapter4 vivado 设计流程-实例

⚫ 只有一个函数可以作为顶层函数被综合,并且这个函数不能是 main() 函数

⚫ 顶层可综合函数下面的子函数也是可综合的

⚫ C 里面不可以被综合的:

◼ 动态内存分配

剩余46页未读,继续阅读

d_b_

- 粉丝: 207

- 资源: 4

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0