没有合适的资源?快使用搜索试试~ 我知道了~

首页ES7243E DS.pdf

资源详情

资源推荐

1

High Performance Stereo Audio ADC

FEATURES

• High performance multi-bit delta-sigma

audio ADC

• 101 dB signal to noise ratio

• -90 dB THD+N

• Low noise PGA

• 24-bit, 8 to 48 kHz sampling frequency

• I

2

S/PCM master or slave serial data port

• Support TDM up to 16 channels

• 256/384Fs, USB 12/24 MHz and other

non standard audio system clocks

• Auto level control (ALC) and noise gate

• Support digital mic

• Low power

APPLICATIONS

• Mic Array

• Soundbar

• Audio Interface

• Digital TV

• A/V Receiver

• DVR

• NVR

ORDERING INFORMATION

ES7243E -40°C ~ +85°C

QFN-20

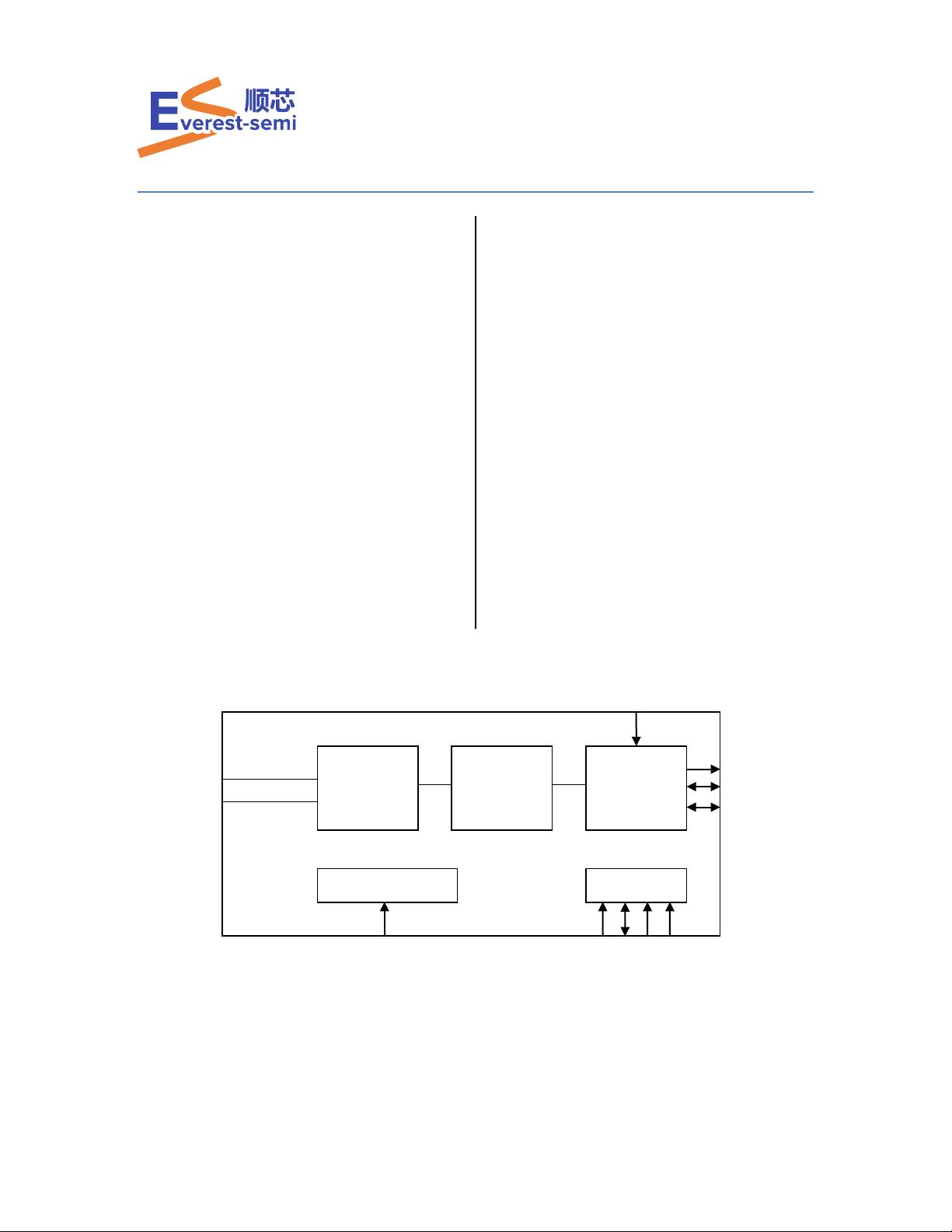

BLOCK DIAGRAM

ES7243E

AINLP/AINLN

AINRP/AINRN

Multi-bit

Delta-sigma

Modulator

Audio

Data

Interface

DSP

Clock Manager

Sample Rate Detector

I

2

C

Interface

SDOUT/AD2

SCLK

LRCK

MCLK

CCLK CDATA AD0 AD1

TDMIN

Everest Semiconductor Confidential ES7243E

Revision 2.0 2 June 2019

Latest datasheet: www.everest-semi.com

or info@everest-semi.com

1. PIN OUT AND DESCRIPTION ................................................................................................ 4

2. TYPICAL APPLICATION CIRCUIT .......................................................................................... 5

3. CLOCK MODES AND SAMPLING FREQUENCIES ............................................................... 6

4. MICRO-CONTROLLER CONFIGURATION INTERFACE ...................................................... 6

5. DIGITAL AUDIO INTERFACE .................................................................................................. 8

6. ELECTRICAL CHARACTERISTICS ..................................................................................... 10

ABSOLUTE MAXIMUM RATINGS ................................................................................................ 10

RECOMMENDED OPERATING CONDITIONS .............................................................................. 10

Note: for VDDD=1.8V, sampling frequency must be less than 24 kHz. ..................................... 10

ADC ANALOG AND FILTER CHARACTERISTICS AND SPECIFICATIONS ........................................ 10

DC CHARACTERISTICS ................................................................................................................ 11

I

2

C SWITCHING SPECIFICATIONS (SLOW SPEED MODE/HIGH SPEED MODE) ........................... 11

SERIAL AUDIO PORT SWITCHING SPECIFICATIONS ................................................................... 12

7. CONFIGURATION REGISTER DEFINITION ........................................................................ 13

REGISTER 0X00 –RESET, DEFAULT 0001 1110 ........................................................................... 13

REGISTER 0X01 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 13

REGISTER 0X02 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 13

REGISTER 0X03 – CLOCK MANAGER, DEFAULT 0010 0000 ....................................................... 14

REGISTER 0X04 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 14

REGISTER 0X05 – CLOCK MANAGER, DEFAULT 0000 0000 ....................................................... 14

REGISTER 0X06 – CLOCK MANAGER, DEFAULT 0000 0011 ....................................................... 14

REGISTER 0X07 – CLOCK MANAGER, DEFAULT 0000 0001 ....................................................... 15

REGISTER 0X08 – CLOCK MANAGER, DEFAULT 1111 1111 ....................................................... 15

REGISTER 0X09 – CLOCK MANAGER, DEFAULT 1100 0001 ....................................................... 15

REGISTER 0X0A – SDP, DEFAULT 1000 0001 ............................................................................. 15

REGISTER 0X0B – SDP, DEFAULT 1100 0000 .............................................................................. 16

REGISTER 0X0C – SDP, DEFAULT 0000 0000 .............................................................................. 16

REGISTER 0X0D – ADC CONTROL, DEFAULT 0000 0000 ............................................................ 17

REGISTER 0X0E – ADC CONTROL, DEFAULT 0000 0000 ............................................................. 17

REGISTER 0X0F – ADC CONTROL, DEFAULT 0000 0000 ............................................................. 17

REGISTER 0X10 – ADC CONTROL, DEFAULT 0000 0000............................................................. 18

REGISTER 0X11 – ADC CONTROL, DEFAULT 0000 0000............................................................. 18

REGISTER 0X12 – ADC CONTROL, DEFAULT 0000 0000............................................................. 19

REGISTER 0X13 – ADC CONTROL, DEFAULT 0000 0000............................................................. 19

REGISTER 0X14 – ADC CONTROL, DEFAULT 0000 1100............................................................. 20

Everest Semiconductor Confidential ES7243E

Revision 2.0 3 June 2019

Latest datasheet: www.everest-semi.com

or info@everest-semi.com

REGISTER 0X15 – ADC CONTROL, DEFAULT 0000 1100............................................................. 20

REGISTER 0X16 – ANALOG, DEFAULT 1111 1111 ...................................................................... 20

REGISTER 0X17 – ANALOG, DEFAULT 0000 0000 ...................................................................... 20

REGISTER 0X18 – ANALOG, DEFAULT 0010 0100 ...................................................................... 20

REGISTER 0X19 – ANALOG, DEFAULT 1000 1000 ...................................................................... 21

REGISTER 0X1A – ANALOG, DEFAULT 0100 0100 ...................................................................... 21

REGISTER 0X1B – ANALOG, DEFAULT 0100 0100 ...................................................................... 22

REGISTER 0X1C – ANALOG, DEFAULT 0100 0100 ...................................................................... 23

REGISTER 0X1D – ANALOG, DEFAULT 0000 0000 ...................................................................... 23

REGISTER 0X1E – ANALOG, DEFAULT 0000 0101 ...................................................................... 24

REGISTER 0X1F – ANALOG, DEFAULT 0000 1100 ...................................................................... 24

REGISTER 0X20 – ANALOG, DEFAULT 0000 0000 ...................................................................... 24

REGISTER 0X21 – ANALOG, DEFAULT 0000 0000 ...................................................................... 25

REGISTER 0XF7 – TEST MODE, DEFAULT 1111 0000 ................................................................. 25

REGISTER 0XF8 – TEST MODE, DEFAULT 0000 0000 ................................................................. 26

REGISTER 0XF9 – TEST MODE, DEFAULT 0000 0000 ................................................................. 26

REGISTER 0XFA – I2C CONFIGURE, DEFAULT 0000 0000 ........................................................... 26

REGISTER 0XFC – FLAG, DEFAULT 0000 0000 ............................................................................ 26

REGISTER 0XFD – CHIP ID1, DEFAULT 0111 1010 ...................................................................... 26

REGISTER 0XFE – CHIP ID2, DEFAULT 0100 0011 ...................................................................... 26

REGISTER 0XFF – CHIP VERSION, DEFAULT 0000 0000 ............................................................. 27

8. PACKAGE .............................................................................................................................. 28

9. CORPORATE INFORMATION .............................................................................................. 29

Everest Semiconductor Confidential ES7243E

Revision 2.0 4 June 2019

Latest datasheet: www.everest-semi.com

or info@everest-semi.com

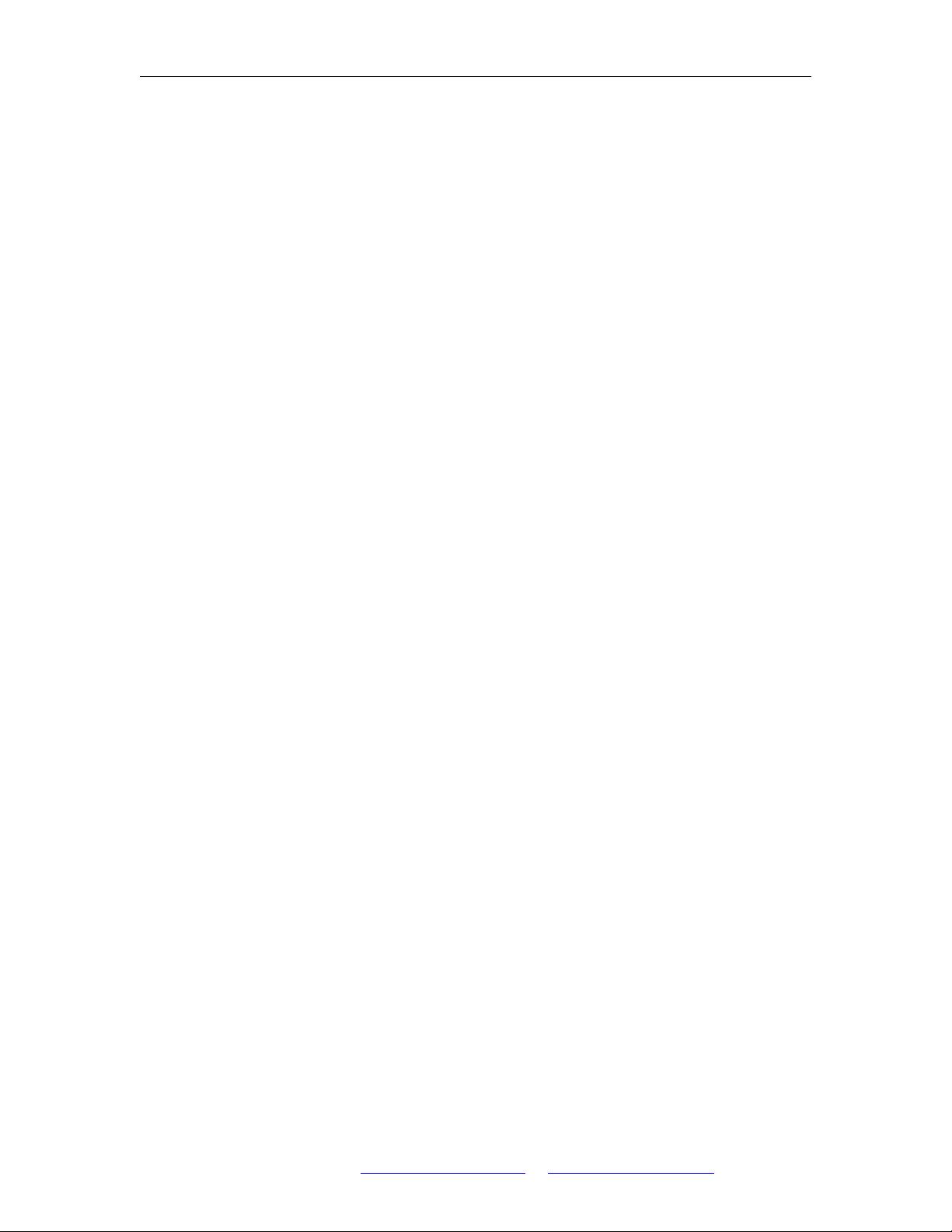

1. PIN OUT AND DESCRIPTION

Pin Name

Pin number

Input or Output

Pin Description

CCLK, CDATA

19, 18

I/O

I

2

C clock and data

AD0, AD1

17,8

I

I

2

C addresses

MCLK

20

I

Master clock

SCLK

6

I/O

Serial data bit clock

LRCK

7

I/O

Serial data left and right channel frame clock

TDMIN 2 I TDM data in

SDOUT/AD2

3

O

Serial data output/ I

2

C address AD2

AINLP, AINLN

AINRP, AINRN

9, 10

16, 15

I Analog left and right inputs

VDDP 1 I Power supply for the digital input and output

VDDD/GNDD

5, 4

I

Digital power supply

VDDA/GNDA

12, 13

I

Analog power supply

REFP

14

O

Filtering capacitor connection

REFQ

11

O

Filtering capacitor connection

ES7243E

AINRP

AD0

CDATA

CCLK

MCLK

16

17

18

19

20

10

9

8

7

6

AINLN

AINLP

AD1

LRCK

SCLK

AINRN

REFP

GNDA

VDDA

REFQ

15

14

13

12

11

VDDP

TDMIN

SDOUT/AD2

GNDD

VDDD

1

2

3

4

5

Everest Semiconductor Confidential ES7243E

Revision 2.0 5 June 2019

Latest datasheet: www.everest-semi.com

or info@everest-semi.com

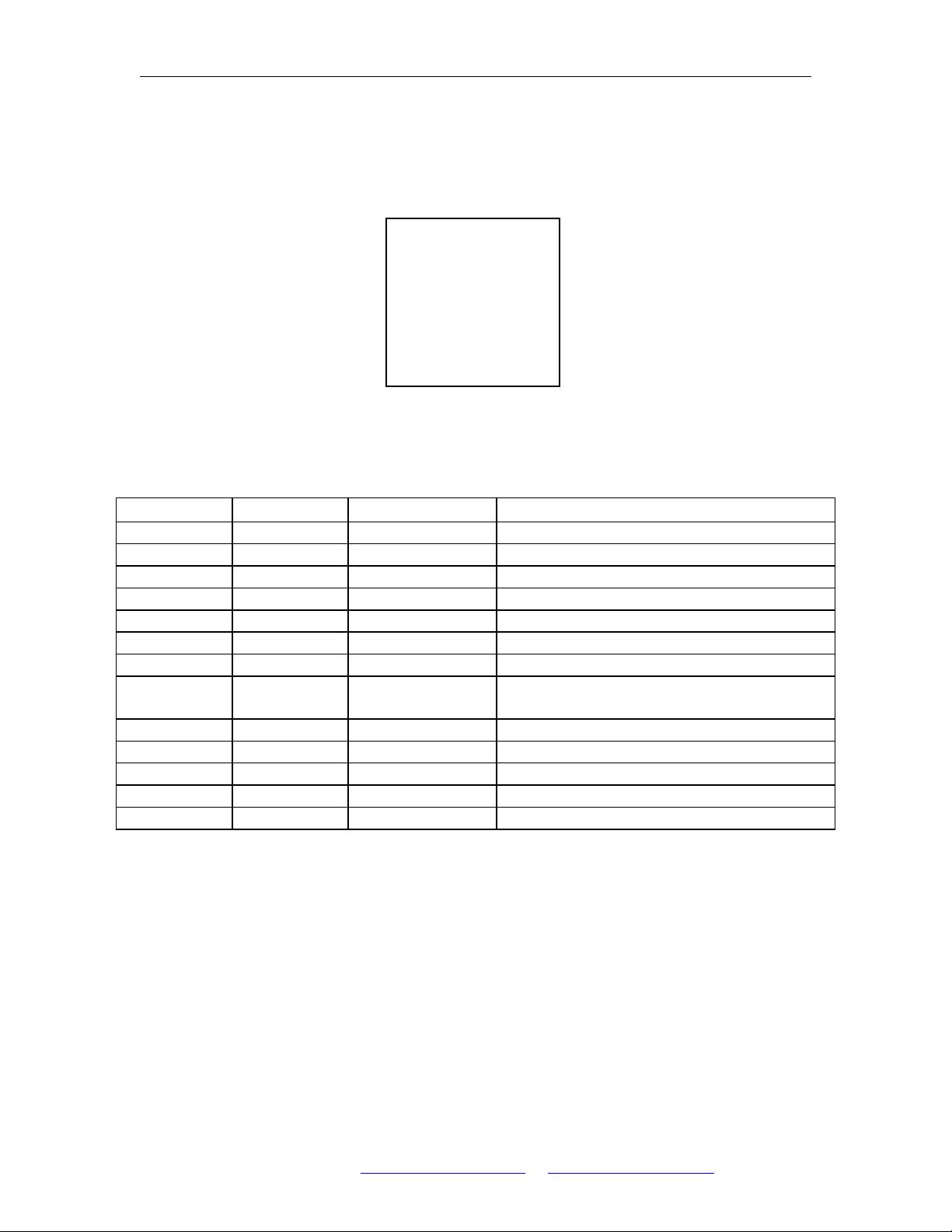

2. TYPICAL APPLICATION CIRCUIT

100nF 100nF

100K

1uF

AGND

VA

1uF

1uF

AGND

1uF

1uF

AINRP

AINLP

CPU/DSP

IIC

IIS

TDMIN

VDDP

1

TDMIN

2

GNDD

4

VDDD

5

LRCK

7

AD1

8

AINLP

9

VDDA

12

RE FQ

11

AINLN

10

AD0

17

CDATA

18

CCLK

19

MCLK

20

SDOUT

3

GNDA

13

AINRN

15

AINRP

16

SCLK

6

RE FP

14

PGND

21

ES7243E

AGNDAGND

AINRN

AINLN

1uF

1uF

VD DD

VD DP

AGND

AGND

AGND

0R

GND(SYS)

AGND

For the best performance,decoupling and filtering capacitors should be located as close to the device package as possible

Additional paralle capacitors(typically 0.1 μF) can be used, larger value capacitors(typically 10 μF) would also help

*

* *

**

*

In the layout, chip is treated as a analog device

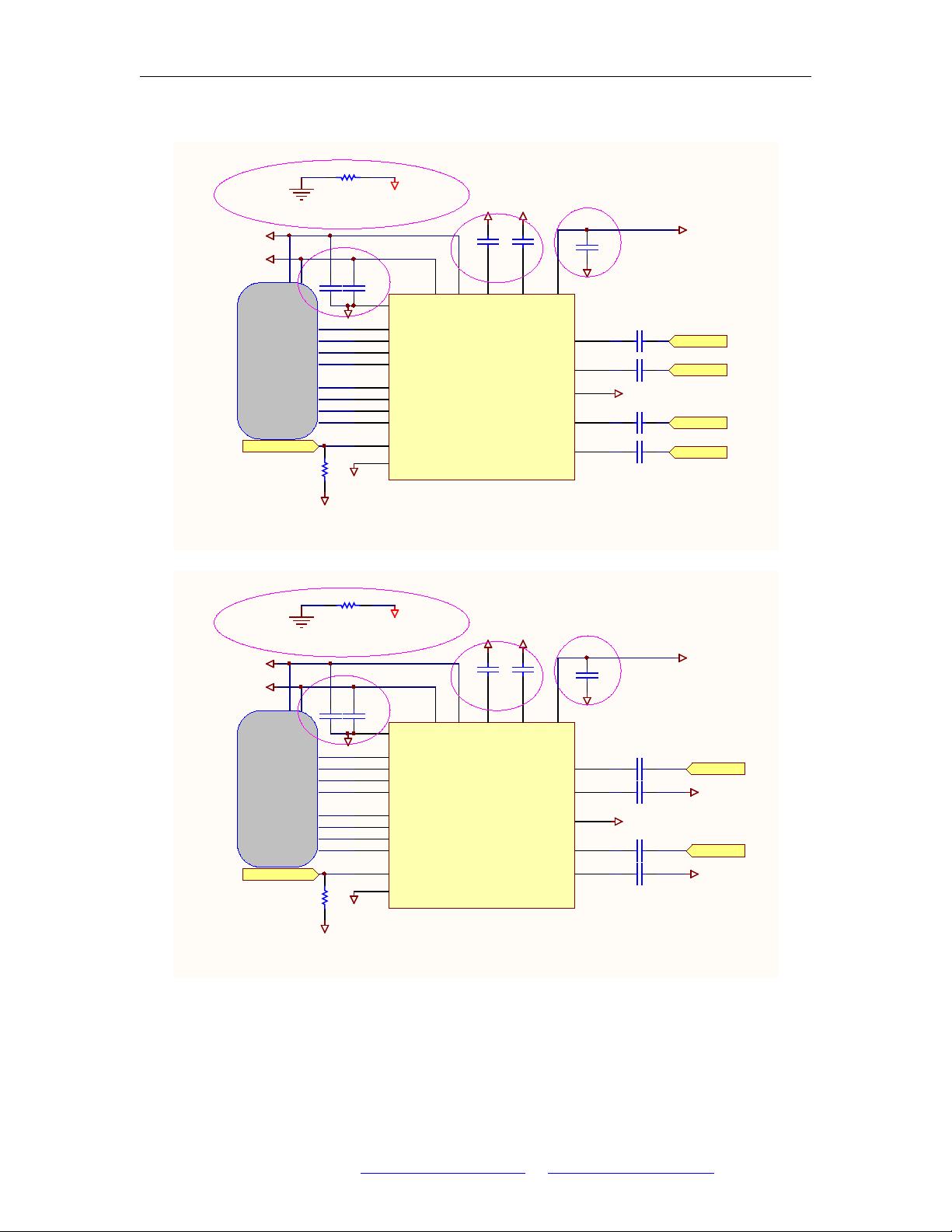

100nF 100nF

100K

1uF

AGND

VA

1uF

1uF

AGND

1uF

1uF

CPU/DSP

IIC

IIS

TDMIN

VDDP

1

TDMIN

2

GNDD

4

VDDD

5

LRCK

7

AD1

8

AINLP

9

VDDA

12

RE FQ

11

AINLN

10

AD0

17

CDATA

18

CCLK

19

MCLK

20

SDOUT

3

GNDA

13

AINRN

15

AINRP

16

SCLK

6

RE FP

14

PGND

21

ES7243E

AGNDAGND

1uF

1uF

VD DD

VD DP

AGND

AGND

AGND

0R

GND(SYS)

AGND

For the best performance,decoupling and filtering capacitors should be located as close to the device package as possible

Additional paralle capacitors(typically 0.1 μF) can be used, larger value capacitors(typically 10 μF) would also help

*

* *

**

*

In the layout, chip is treated as a analog device

AGND

AGND

AINR

AINL

剩余28页未读,继续阅读

硬族嵌入式

- 粉丝: 69

- 资源: 20

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- zigbee-cluster-library-specification

- JSBSim Reference Manual

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功