基于CPLD/FPGA的三线制同步串行通信控制器设计

32 浏览量

更新于2023-05-15

收藏 768KB PDF 举报

“本文主要探讨了三线制同步串行通信控制器接口的设计,包括硬件电路设计和基于CPLD/FPGA的优化实现。文章首先介绍了三线制同步串行通信的基本原理,然后详细阐述了传统设计方法的不足以及采用CPLD/FPGA技术的优势。在三线制同步串行通信中,数据的发送和接收依赖于共同的时钟源,通常采用编码解码技术,如NRZ-L码,来确保同步。文章还分析了通信过程中的时序逻辑,并展示了基于传统设计的硬件电路接口实现。”

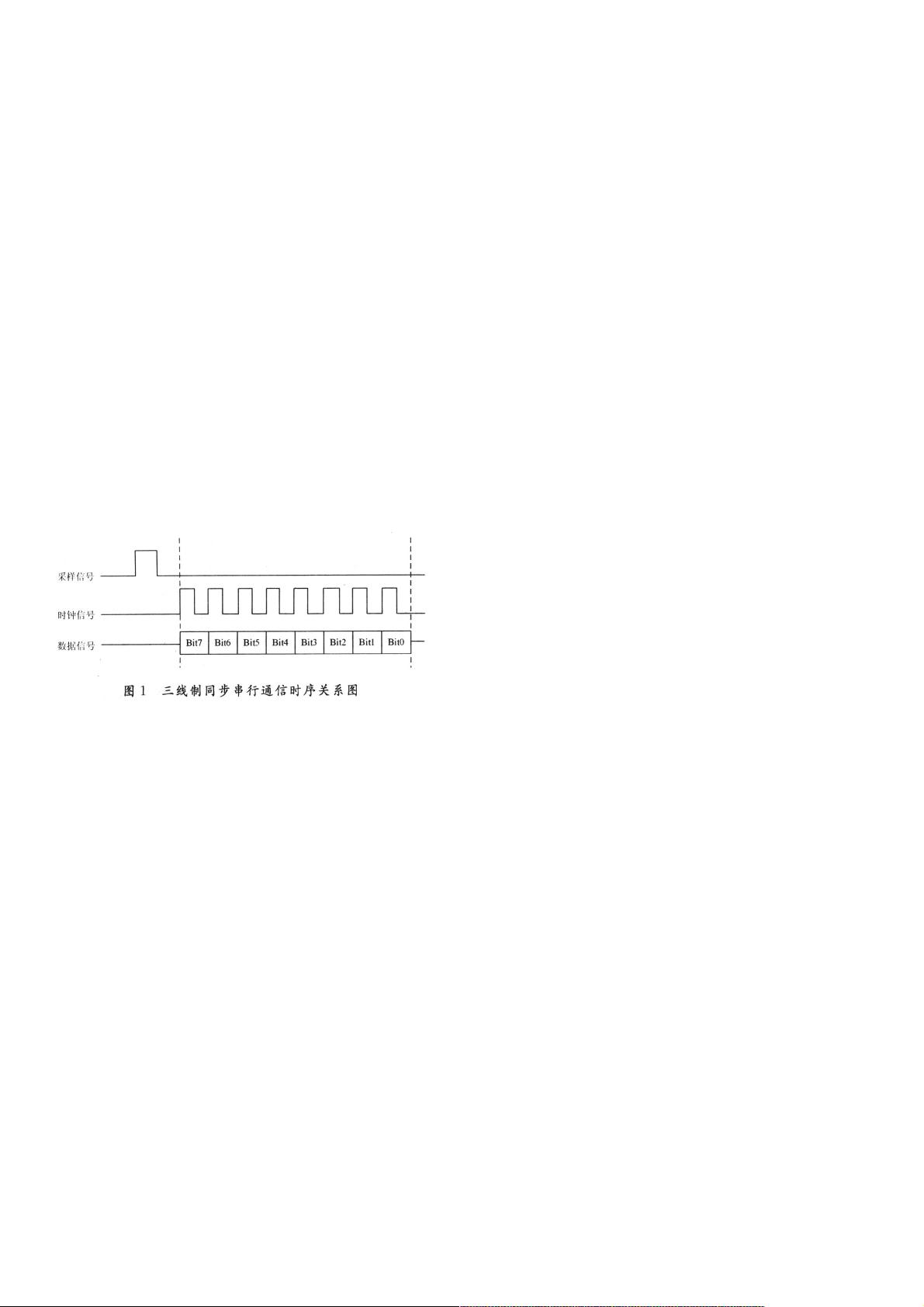

在三线制同步串行通信中,通信双方需共享一个时钟源,以确保数据传输的精确同步。这种通信方式通常使用编码器将数据和时钟结合,通过传输线传送至接收端,接收端再使用解码器提取数据。NRZ-L码是一种常用的码型,其中数据在时钟信号的上升沿被采样和传输。通信涉及三个关键信号:帧同步信号、时钟信号和串行数据信号,它们之间存在特定的时序关系。

在传统设计中,三线制同步串行通信控制器接口通常需要使用多种分立元件,如计数器、移位寄存器、触发器和门电路等。然而,这种方法存在成本高、体积大、功耗高和灵活性低的问题。为解决这些问题,文章提出了基于CPLD(复杂可编程逻辑器件)/FPGA(现场可编程门阵列)的接口设计。这种设计可以显著减少系统体积,降低功耗,并提高设计的灵活性。CPLD/FPGA不仅能够实现通信接口的功能,还能集成其他逻辑模块,便于嵌入式系统的应用。

文章进一步描述了基于传统设计的硬件电路接口,提供了接收接口的电路原理图,展示了如何使用各种基本电子元件来实现三线制同步串行通信的功能。这种传统设计方法虽然直观,但在现代嵌入式系统中,往往会被更加高效、灵活的CPLD/FPGA方案所替代。

三线制同步串行通信控制器接口设计是一个涉及硬件电路设计、同步机制理解以及可编程逻辑器件应用的综合问题。通过采用CPLD/FPGA技术,设计者可以创建更符合现代需求的通信解决方案,这在航天工程和其他需要远程通信的领域具有重要的实际应用价值。

2020-11-09 上传

2020-11-07 上传

2021-01-19 上传

2020-11-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38663113

- 粉丝: 5

- 资源: 896

最新资源

- 新代数控API接口实现CNC数据采集技术解析

- Java版Window任务管理器的设计与实现

- 响应式网页模板及前端源码合集:HTML、CSS、JS与H5

- 可爱贪吃蛇动画特效的Canvas实现教程

- 微信小程序婚礼邀请函教程

- SOCR UCLA WebGis修改:整合世界银行数据

- BUPT计网课程设计:实现具有中继转发功能的DNS服务器

- C# Winform记事本工具开发教程与功能介绍

- 移动端自适应H5网页模板与前端源码包

- Logadm日志管理工具:创建与删除日志条目的详细指南

- 双日记微信小程序开源项目-百度地图集成

- ThreeJS天空盒素材集锦 35+ 优质效果

- 百度地图Java源码深度解析:GoogleDapper中文翻译与应用

- Linux系统调查工具:BashScripts脚本集合

- Kubernetes v1.20 完整二进制安装指南与脚本

- 百度地图开发java源码-KSYMediaPlayerKit_Android库更新与使用说明