FPGA程序远程在线更新设计程序远程在线更新设计

本文以提高FPGA远程更新程序的方便性为目标,提出了一种基于EPCS Flash的远程在线更新FPGA程序的方

法,从而在应用中能够使基于FPGA的产品更加方便地维护升级。

1概述

现场可编程门阵列(Field Programmable Gate Array,FPGA)器件具有高密度、低功耗、高速、高可靠性等优点,在航空航

天、通信、工业控制等方面得到了大量应用。FPGA的处理器分为软核和硬核,并且软核处理器具有高度的灵活性和可配置

性。

由于FPGA器件采用的是SRAM工艺,在断电的情况下FPGA内的配置数据将丢失,所以需要非易失的存储器来结合FPGA完

成嵌入式系统的设计。EPCS(Erasable Programmable Configurable Serial)Flash属于串行接口Flash,具有接口简单、体

积小、配置方便的特点,通常用来存储FPGA的配置文件和Nios II的软件可执行代码。在经过合理的配置后,系统在上电后就

可以从EPCS Flash中读取这些文件来启动整个系统。

为了能使系统得到更灵活的应用,充分发挥FPGA的灵活性、高效性,FPGA的软硬件程序都需要方便的更新和升级功能;而

当形成产品后,通过JTAG和Nios II IDE工具来联合完成对EPCS Flash的更新烧写很不方便。为此,本文结合Altera公司提供

的工具,提出了一种远程在线更新FPGA配置文件和Nios II程序文件的方法。

2系统硬件结构

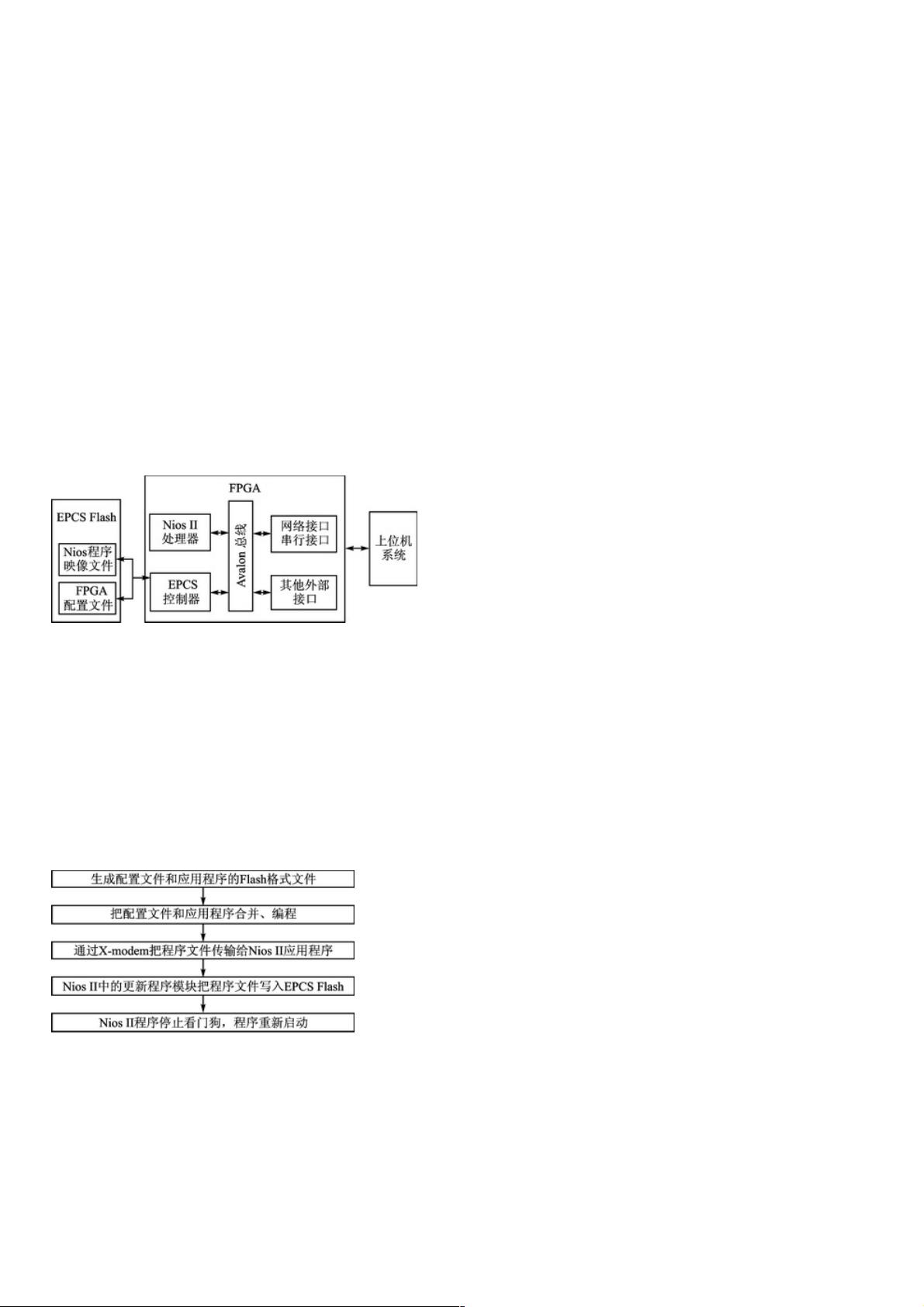

系统硬件结构如图1所示。

图1系统硬件结构图

系统主要有上位机系统、FPGA系统、EPCS Flash三个主体部分。上位机系统提供人机交互的部分,FPGA系统包括Nios II处

理器、EPCS控制器、网络及串行接口和其他外部接口,EPCS Flash主要用于存储FPGA的配置文件和Nios程序映像文件。上

位机系统通过FPGA集成的网络及串行接口来完成通信工作。

FPGA采用Altera公司的Cyclone III系统的EP3C40F484I7N芯片。它具有低功耗、高集成度、易于使用的特性。EPCS Flash

采用Altera公司的EPCS16SI16N芯片,它支持多种可配置的时钟源,最高支持100 MHz的外部时钟源,具有16 Mb的存储空

间,足够满足一般的FPGA配置文件和Nios程序文件的存储需要。

3更新程序处理流程

更新FPGA的配置文件和Nios II的应用程序的流程如图2所示。

图2更新程序处理流程

本方法把由Nios II IDE生成的FPGA配置文件和Nios II程序文件合并,并编程为一个可以直接执行的、包含FPGA配置文件和

Nios II程序文件的二进制BIN文件。然后把该文件通过Xmodem协议由上位机系统传输给Nios II的应用程序。Nios II的应用程

序接收到完整的BIN文件后,把该BIN文件写入到EPCS Flash中。最后,Nios II的应用程序停止看门狗,程序重新启动,即完

成了FPGA的远程在线更新程序的过程。

4合并程序文件

Nios II的启动要经历两个过程:

① FPGA器件本身的配置过程。如果内部逻辑中使用了Nios II,则配置完成的FPGA中包含有Nios II软核CPU。