没有合适的资源?快使用搜索试试~ 我知道了~

首页苹果A1502主板电路图详解

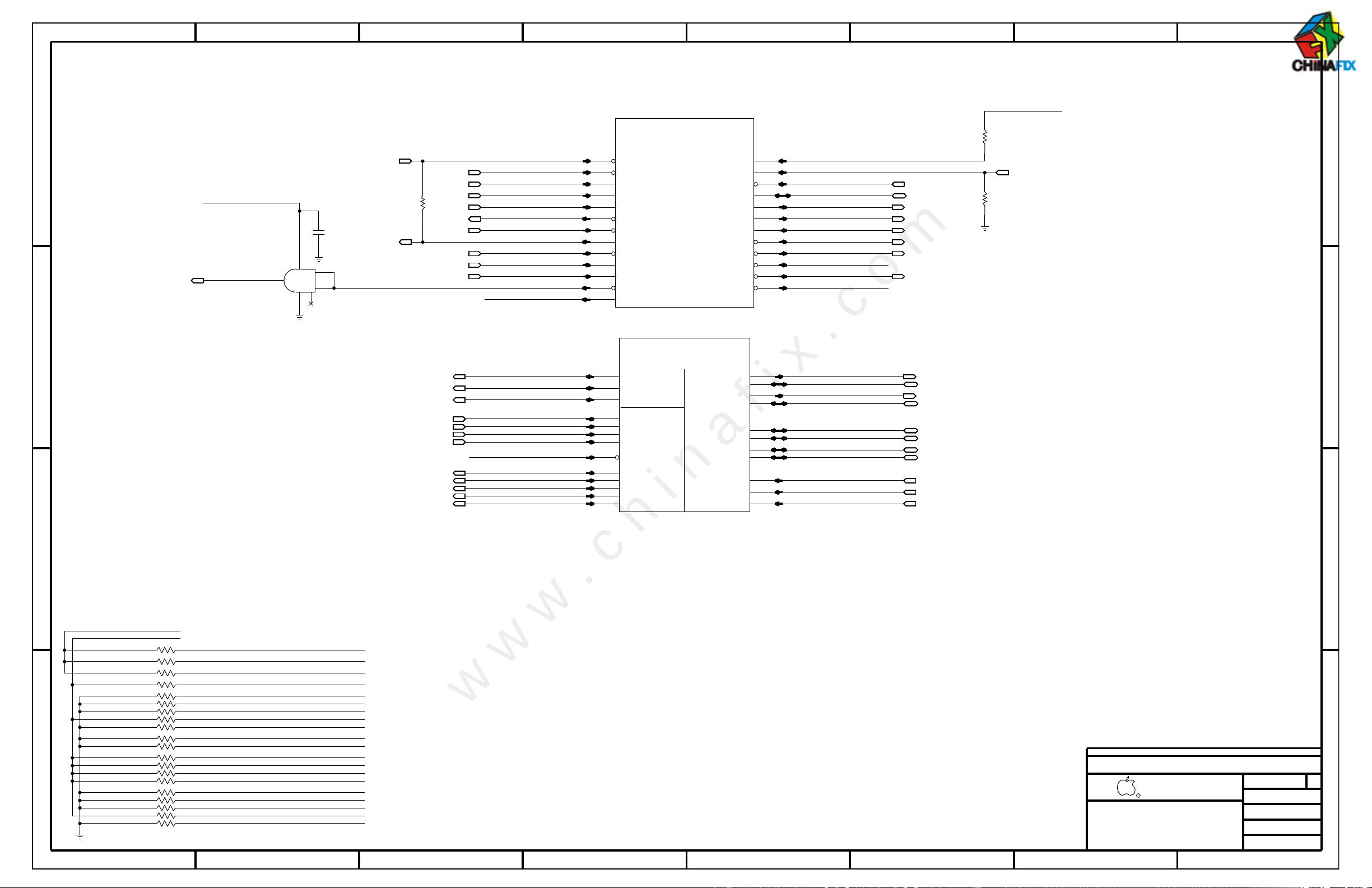

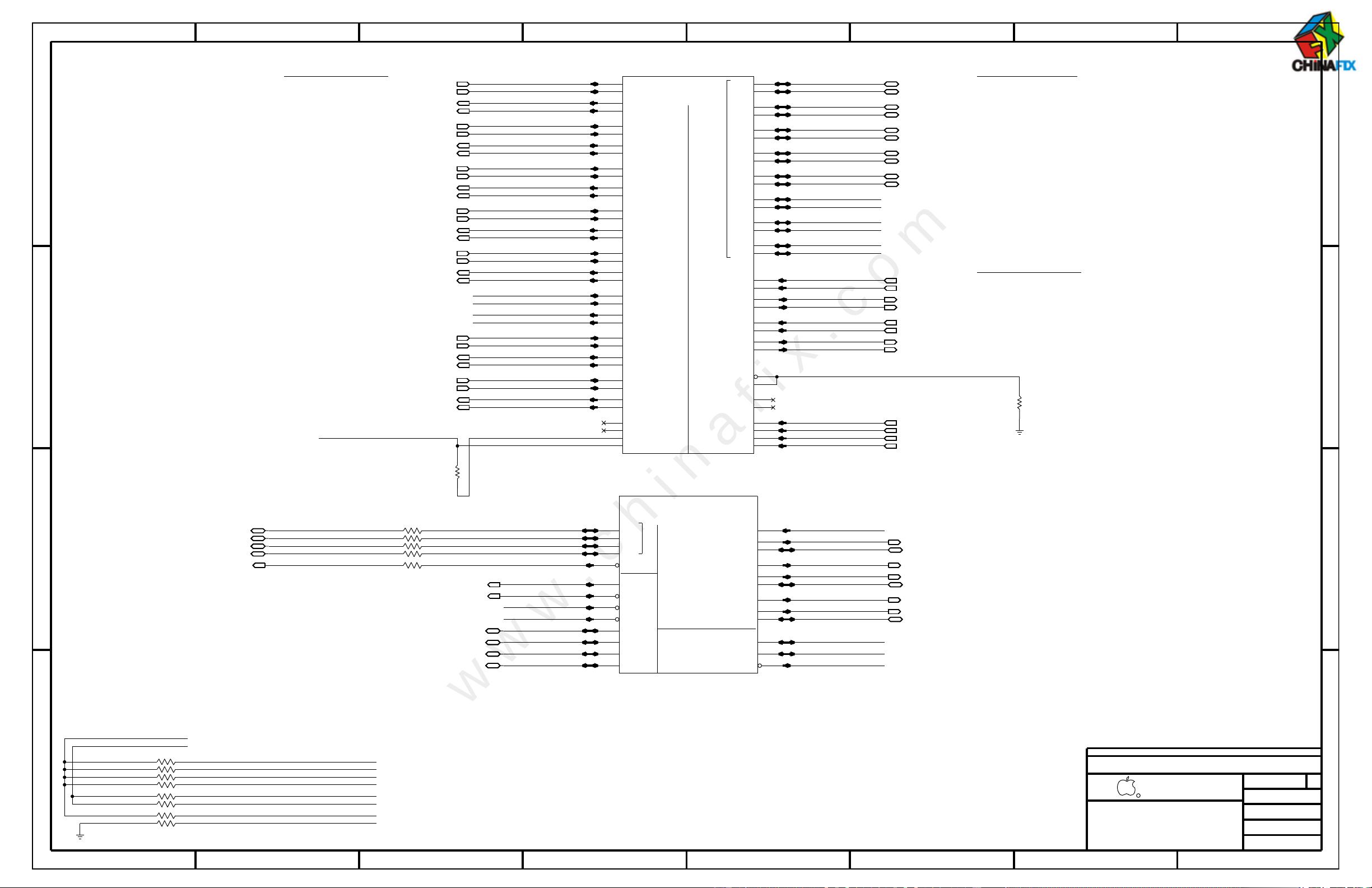

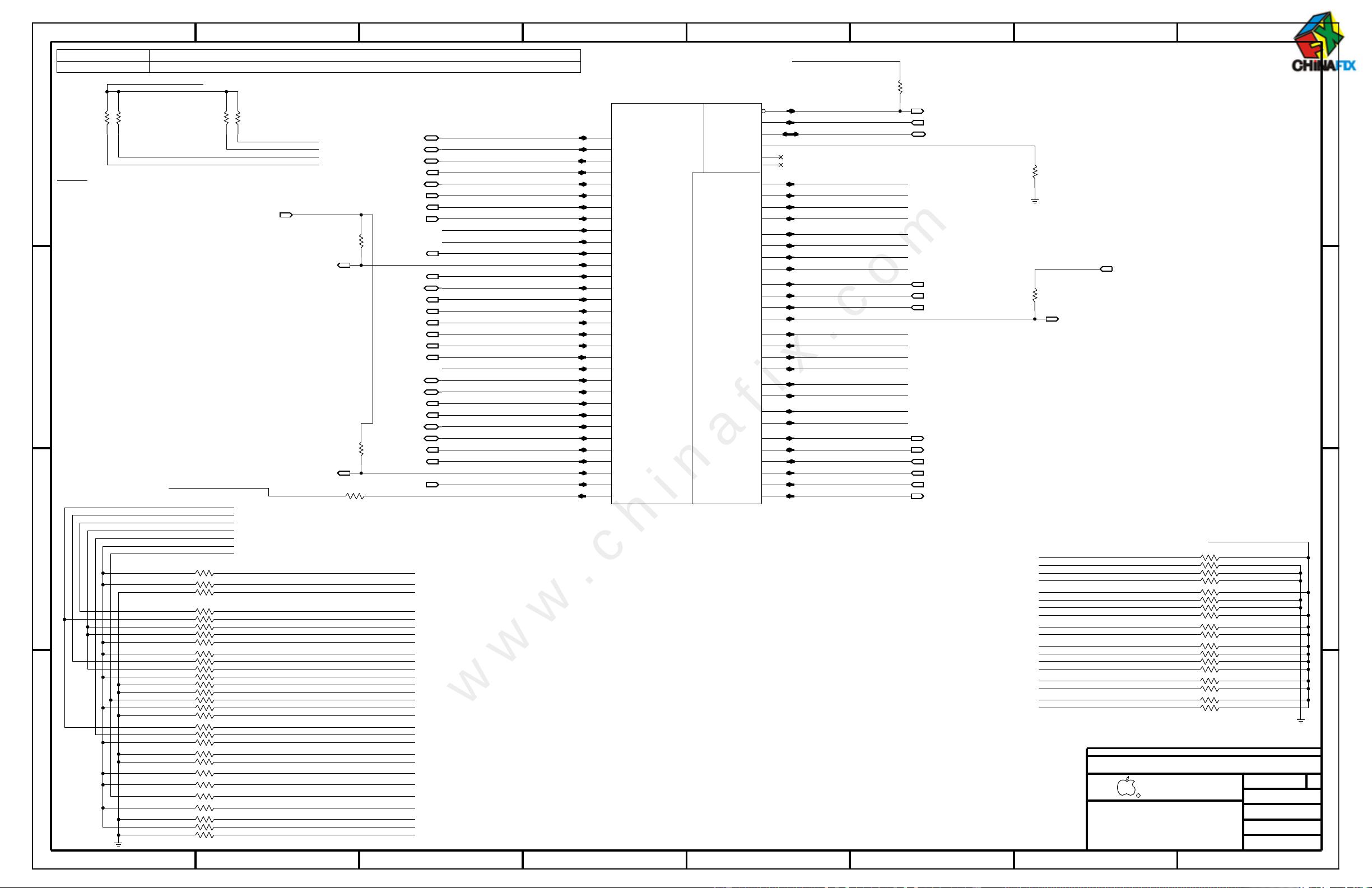

"该资源是一份关于MacBook Pro A1502的电路图,主要针对苹果A1502型号的主板,其板号为820-3476-A。这份电路图详细列出了设备内部的电子组件、连接线路以及各个部分的功能,对维修、故障排查和硬件升级具有重要参考价值。由于电路图内容较多,包含了多个章节和子项,涵盖了电源管理、显示接口、内存、存储、无线通信、音频、I/O接口等多个关键系统。"

MacBook Pro A1502是一款由苹果公司推出的高性能笔记本电脑,其电路图是理解该设备硬件结构和工作原理的重要文档。电路图通常包含以下关键部分:

1. **电源管理系统**:这部分描述了电池、充电电路、电源适配器与主板之间的交互,以及如何为设备的各个组件供电。

2. **显示接口**:包括集成显卡和外接显示器的连接,如Thunderbolt、HDMI等接口的工作原理。

3. **内存(RAM)**:详细展示内存插槽的位置,以及内存条如何与主板通信,以支持高效的计算任务。

4. **存储系统**:涵盖SSD或HDD的连接方式,数据传输路径,以及如何与主板上的SATA或PCIe接口配合工作。

5. **无线通信模块**:包括Wi-Fi和蓝牙的天线布局,以及无线芯片组的连接细节。

6. **音频系统**:描述音频编解码器,扬声器和麦克风的连接,以及音频信号的处理流程。

7. **输入/输出(I/O)接口**:如USB、MagSafe、耳机插孔、SD卡读卡器等,这些接口如何与主板上的控制器通信。

8. **其他组件**:包括键盘、触控板、传感器等组件的电路连接,以及它们如何与主板交互。

电路图的使用对于专业技术人员至关重要,他们可以通过图中的信息快速定位问题,例如识别短路、断路或其他硬件故障。同时,对于有经验的DIY爱好者,电路图也提供了升级硬件的可能性,如更换更大的内存或提升存储性能。

在进行任何维修或升级操作前,理解并参照电路图是非常必要的,可以避免对设备造成不必要的损坏。不过,由于涉及到复杂的电子元件和高压电流,如果没有专业知识和技能,建议寻求专业人士的帮助。在www.chinafix.com这样的网站上,可能能找到更具体的电路图内容和相关的技术支持。

w w w . c h i n a f i x . c o m

IN

OUT

IN

OUT

OUT

IN

IN

IN

IN

OUT

OUT

SLP_WLAN*/GPIO29

SLP_S0*

BATLOW*/GPIO72

ACPRESENT/GPIO31

PWRBTN*

SUSWARN*/SUSPWRDNACK/GPIO30

RSMRST*

PCH_PWROK

APWROK

SYS_RESET*

SUSACK*

PLTRST*

SYS_PWROK

DPWROK

DSWVRMEN

CLKRUN*/GPIO32

WAKE*

SLP_S5*/GPIO63

SUSCLK/GPIO62

SUS_STAT*/GPIO61

SLP_S4*

SLP_S3*

SLP_A*

SLP_SUS*

SLP_LAN*

SYSTEM POWER MANAGEMENT

SYM 8 OF 19

OUT

OUT

OUT

OUT

BI

IN

IN

OUT

OUT

GPIO53

GPIO51

GPIO54

GPIO52

GPIO55

PME*

PIRQC*/GPIO79

PIRQD*/GPIO80

PIRQA*/GPIO77

PIRQB*/GPIO78

EDP_BKLEN

EDP_BKLCTL

EDP_HPD

DDPC_HPD

DDPC_AUXP

DDPB_AUXP

DDPB_HPD

DDPB_AUXN

DDPC_AUXN

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_CTRLCLK

DDPB_CTRLDATA

EDP_VDDEN

SIDEBAND

eDP

DISPLAY

PCI

SYM 9 OF 19

OUT

BI

BI

BI

BI

BI

BI

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

IN

IN

OUT

IN

NC

08

NC

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87

6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

SLP_S0# Isolation

SLP_S0# can be driven high outside of S0

U1420 ensures signal will only be high in S0.

(IPD-PLTRST#)

(IPU)

(IPU)

(IPD-DeepSx)

(IPD-DeepSx)

(IPD-PLTRST#)

(IPU)

R1400 kept for debug purposes.

61

72

13 18 36

38

38

15 16 18

13 17 72

13 17 72

16 17 36 72

17 36 68 72

13 40 61

13 17 18 36 61 63 68

OMIT_TABLE

CRITICAL

HASWELL-ULT

2C+GT2

BGA-TSP

U0500

AJ8

AB5

AN4

V5

AV5

AW7

AY7

AG7

AL7

AW6

AL5

AJ7AF3

AT4

AJ6

AP5

AP4

AM5

AG4

AK2

AE6

AV4

AG2

AC3

AJ5

13

18 29 36 61 63

13 36 61

37

36 45 68

13 36 45 68

13 29 31 72

5%

201

1/20W

MF

100K

R1451

1

2

36

72

5%

201

1/20W

MF

330K

R1450

1

2

13

62

62 68

2C+GT2

BGA-TSP

CRITICAL

OMIT_TABLE

HASWELL-ULT

U0500

C5

B5

B9

C9

C8

B6

A6

D9

D11

A8

B8

A9

D6

C6

R5

L1

L4

L3

U7

U6

P4

N4

N2

AD4

13

62

23 74

64 66 74

64 66 74

23 74

28

64 66

64 66

28

23

64 66

62

5% 201

1/20W

MF

100K

R1446

12

5% 201

1/20W

MF

100K

R1445

12

5% 201

1/20W

MF

100K

R1442

12

5% 201

1/20W

MF

100K

R1443

12

5% 201

1/20W

MF

10K

R1441

12

5%

0

0201

1/20W

MF

NO STUFF

R1400

1

2

5% 201

1/20W

MF

100K

R1440

12

13

24

13 36

13 68

13 68

13 68

13 64 66

13 68

13 68

13 25 36

5%

201

1/20W

MF

10K

R1455

12

5%

201

1/20W

MF

10K

R1410

12

5% 201

1/20W

MF

100K

R1447

12

5% 201

1/20W

MF

100K

R1448

12

5% 201

1/20W

MF

100K

R1449

12

5%

201

1/20W

MF

100K

R1431

12

5%

201

1/20W

MF

100K

R1430

12

36

37

13 61

5%

201

1/20W

MF

1K

R1405

12

5%

201

1/20W

MF

10K

R1452

12

5%

201

1/20W

MF

100K

R1460

12

5%

201

1/20W

MF

100K

R1461

12

5%

201

1/20W

MF

100K

R1462

12

5%

201

1/20W

MF

100K

R1464

12

5%

201

1/20W

MF

100K

R1463

12

13

16 36 72

SOT891

74LVC1G08

CRITICAL

U1420

2

1

35

6

4

0.1UF

10V

10%

X5R-CERM

0201

C1420

1

2

SYNC_MASTER=J44

SYNC_DATE=08/12/2013

PCH PM/PCI/GFX

PCH_SUSWARN_L

PCH_SUSACK_L

DPMUX_HPD_OUT

DP_HDMI_TBT_AUX_P

NC_PM_SLP_A_L

DP_HDMI_TBT_AUX_N

DP_TBTSNK0_AUXCH_C_P

DP_TBTSNK0_AUXCH_C_N

DP_TBTSNK0_DDC_DATA

DP_HDMI_TBT_DDC_CLK

DP_TBTSNK0_HPD

DP_INT_HPD

PPVRTC_G3H

PM_SLP_S3_L

PM_SLP_S4_L

PM_CLK32K_SUSCLK_R

PM_SLP_S5_L

PCIE_WAKE_L

DP_HDMI_TBT_DDC_DATA

DP_TBTSNK0_DDC_CLK

TP_PCH_SLP_LAN_L

PM_SLP_SUS_L

NC_PCI_PME_L

TBT_PWR_REQ_L

SMC_RUNTIME_SCI_L

AUD_IP_PERIPHERAL_DET

AUD_I2C_INT_L

HDMITBTMUX_LATCH

ENET_LOW_PWR

AUD_IPHS_SWITCH_EN

AUD_PWR_EN

ODD_PWR_EN_L

PM_BATLOW_L

SMC_ADAPTER_EN

PM_PWRBTN_L

PM_RSMRST_L

PLT_RESET_L

PM_PCH_PWROK

PM_PCH_PWROK

PM_PCH_SYS_PWROK

PM_SYSRST_L

LPC_PWRDWN_L

PM_CLKRUN_L

PM_DSW_PWRGD

PCH_DSWVRMEN

EDP_PANEL_PWR

PCIE_WAKE_L

PM_CLKRUN_L

PM_SLP_S5_L

SMC_RUNTIME_SCI_L

TBT_PWR_REQ_L

AUD_I2C_INT_L

ODD_PWR_EN_L

HDMITBTMUX_LATCH

ENET_LOW_PWR

AUD_IPHS_SWITCH_EN

AUD_PWR_EN

PP3V3_S5

PM_PWRBTN_L

PM_BATLOW_L

TP_PCH_SLP_WLAN_L

EDP_BKLT_PWM

PP3V3_S0

PCH_PM_SLP_S0_L

PM_SLP_S0_L

EDP_BKLT_EN

PM_SLP_S4_L

PM_SLP_S3_L

PM_SLP_S0_L

AUD_IP_PERIPHERAL_DET

EDP_PANEL_PWR

EDP_BKLT_EN

PM_SLP_SUS_L

PP3V3_S0

13 OF 78

<BRANCH>

<SCH_NUM>

<E4LABEL>

14 OF 120

68

8

12

17 65

66

72

13 29 31 72

13 36 45 68

13 36 61

13 36

13 24

13 68

13 68

13 64 66

13 68

13 68

13 61

8

11 15

16 17 18 26 27 29 56 59

60 61 65 68 77

13 16 36 72

13 25 36

8

11

12 13 15 17 18 24 28 30

37 38 39 40 41 42 43 44 46 47

50 61 62 64 65 68 77

13 18 29 36 61 63

13 17 18 36 61 63 68

13 18 36

13 68

13 62

13 62

13 40 61

8

11 12

13 15 17 18 24 28 30 37

38 39 40 41 42 43 44 46 47 50

61 62 64 65 68

77

w w w . c h i n a f i x . c o m

SPI_IO3

SPI_MISO

SPI_IO2

SPI_CS2*

SPI_MOSI

SPI_CS0*

SPI_CS1*

LFRAME*

LAD2

LAD3

LAD1

SPI_CLK

LAD0

SMBALERT*/GPIO11

SMBCLK

SMBDATA

SML0ALERT*/GPIO60

SML0CLK

SML0DATA

SML1CLK_GPIO75

SML1ALERT*/PCHHOT*/GPIO73

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST*

SYM 7 OF 19

LPC

SMBUS

SPI

C-LINK

OUT

IN

IN

IN

OUT

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

PCIE_RCOMP

PCIE_IREF

RSVD

RSVD

PETP1/USB3TP2

PETN1/USB3TN2

PERP1/USB3RP2

PERN1/USB3RN2

PETP4

PETN4

PERP4

PERN4

PETP3

PETN3

PERP3

PERN3

PETP5_L3

PETN5_L3

PETP5_L2

PETN5_L2

PERP5_L2

PERN5_L2

PETP5_L1

PETN5_L1

PERP5_L1

PERN5_L1

PERN2/USB3RN3

PERP2/USB3RP3

PETN2/USB3TN3

PETP2/USB3TP3

USB2P7

USB2N7

PERP5_L3

PERN5_L3

PETP5_L0

PETN5_L0

PERP5_L0

PERN5_L0

OC1*/GPIO41

OC0*/GPIO40

OC2*/GPIO42

OC3*/GPIO43

RSVD

RSVD

USBRBIAS*

USBRBIAS

USB3TP1

USB3TN1

USB3RP1

USB3RN1

USB3TP0

USB3TN0

USB3RP0

USB3RN0

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB

PCI-E

SYM 11 OF 19

IN

IN

NC

NC

OUT

OUT

IN

IN

OUT

IN

OUT

IN

IN

NC

NC

BI

BI

BI

IN

BI

BI

BI

BI

BI

OUT

BI

BI

OUT

BI

BI

BI

BI

OUT

OUT

OUT

OUT

IN

BI

BI

OUT

BI

OUT

BI

BI

IN

BI

BI

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87

6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

page, may be wire-ORed into other signals.

SML1ALERT# pull-up not provided on this

Unused

(& Ethernet if combo)

Thunderbolt lane 3

Thunderbolt lane 2

Thunderbolt lane 1

PCIe Port Assignments:

USB3 Port Assignments:

Thunderbolt lane 0

Reserved: FireWire

AirPort

Camera

Ext B (SS)

USB Port Assignments:

Ext A (LS/FS/HS)

Ext B (LS/FS/HS)

BT

IR

Reserved: SD (HS)

(IPU/IPD)

(IPU)

(IPU/IPD)

(IPU/IPD)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

(IPU)

Trackpad

Reserved: Camera

(IPD)

SD Card Reader

Ext A (SS)

Otherwise, 100k pull-up to 3.3V SUS required.

(IPU)

CRITICAL

2C+GT2

BGA-TSP

OMIT_TABLE

HASWELL-ULT

U0500

AF2

AD2

AF4

AU14

AW12

AY12

AW11

AV12

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AA3

Y7

Y4

AC2

Y6

AF1

AA4

AA2

23

68 70

100K

5% MF

1/20W

201

R1580

12

100K

5%

1/20W

MF

201

R1581

12

14

16 33

14 16 63

14 16

38

14 16

23 68 70

14 68

23 68 70

23 68 70

23 68 70

23 68 70

23 68 70

23 68 70

23 68 70

23 68 70

63 71

63 71

63 68 71

63 68 71

32 70

32 70

32 68 70

32 68 70

63 68 70

63 68 70

OMIT_TABLE

2C+GT2

BGA-TSP

HASWELL-ULT

CRITICAL

U0500

AL3

AT1

AH2

AV3B27

A27

G17

F15

G11

F13

F10

F8

H10

E6

F17

G15

F11

G13

E10

E8

G10

F6

C30

B31

C29

B29

C23

B23

B21

B22

C31

A31

B30

A29

C22

A23

C21

A21

AM10

AN10

E13

E15

AN8

AR7

AR8

AR10

AM15

AM13

AP11

AR13

AM8

AT7

AP8

AT10

AL15

AN13

AN11

AP13

G20

E18

H20

F18

C33

B33

B34

A33

AJ11

AJ10

63

68 70

63 68 70

3.01K

201

MF

1%

PLACE_NEAR=U0500.A27:2.54mm

1/20W

R1500

1

2

63

68 71

63 68 71

63 68 71

63 68 71

33 68 71

23 68 70

33 68 71

33 68 71

33 68 71

22.6

201

1%

1/20W

MF

PLACE_NEAR=U0500.AJ10:2.54mm

R1570

1

2

34

71

34 71

66 71

23 68 70

66 71

29 71

29 71

63 71

63 71

23 68 70

33 71

33 71

36 45 68 72

36 45 68 72

36 45 68 72

36 45 68 72

36 45 68 72

1/20W

5%

201

MF

33

R1543

12

201

1/20W

MF5%

33

R1542

12

23

68 70

33

MF

201

5%

1/20W

R1544

12

5%

1/20W

201

MF

33

R1540

12

1/20W

5%

201

MF

33

R1541

12

45

72

45 72

32 36 39 43 68 72 76

23 68 70

32 36 39 43 68 72 76

39 72

39 72

16 19 39 63 68 72

16 19 39 63 68 72

45 72

45 72

23 68 70

14 45 72

14 45 72

201

1/20W

MF5%

100K

R1591

12

1K

5% MF

1/20W

201

R1549

12

100K

5%

1/20W

MF

201

R1590

12

1K

5% MF

1/20W

201

R1548

12

100K

5%

1/20W

MF

201

R1582

12

100K

201

MF5%

1/20W

R1583

12

SYNC_DATE=08/12/2013

SYNC_MASTER=J44

PCH PCIe/USB/LPC/SPI/SMBus

PP3V3_SUS

XDP_USB_EXTD_OC_L

XDP_USB_EXTC_OC_L

XDP_USB_EXTB_OC_L

XDP_USB_EXTA_OC_L

WOL_EN

LPC_AD_R<0>

LPC_AD<2>

PCH_SML1ALERT_L

PP1V05_S0SW_PCH_VCCUSB3PLL

PCH_PCIE_RCOMP

USB_EXTA_P

USB_EXTB_P

USB_BT_N

NC_USB_IRP

USB_TPAD_N

USB_TPAD_P

TP_USB_5N

USB_BT_P

NC_PCIE_FW_R2D_CN

LPC_AD_R<2>

LPC_AD_R<1>

LPC_FRAME_L

NC_USB_IRN

USB3_EXTA_D2R_P

USB_EXTB_N

PCIE_TBT_D2R_P<0>

PCIE_TBT_R2D_C_N<0>

USB3_EXTB_R2D_C_P

PCIE_AP_D2R_N

PCH_SMBALERT_L

TP_USB_5P

NC_USB_CAMERAN

NC_USB_CAMERAP

NC_USB_SDP

NC_USB_SDN

USB_EXTA_N

USB3_EXTB_R2D_C_N

USB3_EXTB_D2R_P

USB3_EXTB_D2R_N

USB3_EXTA_R2D_C_N

USB3_EXTA_R2D_C_P

USB3_EXTA_D2R_N

USB3RPCIE_SD_R2D_C_N

USB3RPCIE_SD_D2R_P

USB3RPCIE_SD_D2R_N

NC_PCIE_FW_R2D_CP

NC_PCIE_FW_D2RP

PCIE_AP_R2D_C_N

PCIE_AP_D2R_P

PCIE_TBT_R2D_C_P<3>

PCIE_TBT_R2D_C_N<3>

PCIE_TBT_R2D_C_P<2>

PCIE_TBT_R2D_C_N<2>

PCIE_TBT_D2R_P<2>

PCIE_TBT_D2R_N<2>

PCIE_TBT_R2D_C_P<1>

PCIE_TBT_R2D_C_N<1>

PCIE_TBT_D2R_P<1>

PCIE_TBT_D2R_N<1>

PCIE_CAMERA_D2R_N

PCIE_CAMERA_D2R_P

PCIE_CAMERA_R2D_C_N

PCIE_TBT_D2R_P<3>

PCIE_TBT_D2R_N<3>

PCIE_TBT_R2D_C_P<0>

PCIE_AP_R2D_C_P

NC_PCIE_FW_D2RN

USB3RPCIE_SD_R2D_C_P

SPI_CLK_R

LPC_AD<0>

LPC_AD<1>

LPC_AD<3>

SML_PCH_0_CLK

SMBUS_PCH_DATA

SMBUS_PCH_CLK

NC_CLINK_DATA

NC_CLINK_RESET_L

NC_CLINK_CLK

PCIE_TBT_D2R_N<0>

PCH_USB_RBIAS

TP_SPI_CS2_L

TP_SPI_CS1_L

SPI_CS0_R_L

PCIE_CAMERA_R2D_C_P

LPC_FRAME_R_L

LPC_AD_R<3>

SPI_MOSI_R

SPI_MISO

SPI_IO<3>

SPI_IO<2>

XDP_USB_EXTA_OC_L

XDP_USB_EXTB_OC_L

XDP_USB_EXTC_OC_L

XDP_USB_EXTD_OC_L

SMBUS_SMC_1_S0_SDA

SMBUS_SMC_1_S0_SCL

SML_PCH_0_DATA

PP3V3_SUS

SPI_IO<2>

SPI_IO<3>

PCH_SMBALERT_L

WOL_EN

14 OF 78

15 OF 120

<E4LABEL>

<SCH_NUM>

<BRANCH>

8

11

14 45 59 60 61 65

14 16

14 16

14 16 63

14 16 33

8

11

72

71

66

14

71

66

71

66 71

66 71

66 71

66

66

66

66

66

66

71

8

11

14 45 59 60 61 65

14 45 72

14 45 72

14

14 68

w w w . c h i n a f i x . c o m

IN

OUT

BI

BI

OUT

IN

IN

IN

IN

OUT

OUT

SERIRQ

THRMTRIP*

RCIN*/GPIO82

PCH_OPI_COMP

RSVD

RSVD

GSPI0_CS*/GPIO83

GSPI0_MISO/GPIO85

GSPI0_CLK/GPIO84

GSPI1_CLK/GPIO88

GSPI1_CS*/GPIO87

GSPI0_MOSI/GPIO86

GSPI_MOSI/GPIO90

GSPI1_MISO/GPIO89

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART1_RXD/GPIO0

UART0_CTS*/GPIO94

UART0_RTS*/GPIO93

UART1_CTS*/GPIO3

UART1_RST*/GPIO2

UART1_TXD/GPIO1

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C0_SDA/GPIO4

I2C1_SCL/GPIO7

SDIO_CMD/GPIO65

SDIO_CLK/GPIO64

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D0/GPIO66

SDIO_D3/GPIO69

BMBUSY*/GPIO76

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

GPIO15

GPIO17

GPIO16

GPIO24

GPIO28

GPIO27

GPIO26

GPIO56

GPIO57

GPIO58

GPIO59

GPIO47

GPIO44

GPIO48

GPIO49

GPIO50

HSIOPC/GPIO71

GPIO13

GPIO25

GPIO14

GPIO45

GPIO46

GPIO9

GPIO10

DEVSLP0*/GPIO33

DEVSLP1*/GPIO38

SDIO_POWER_EN/GPIO70

DEVSLP2*/GPIO39

SPKR/GPIO81

SYM 10 OF 19

CPU/MISC

GPIO

LPIO

OUT

IN

IN

IN

IN

BI

BI

BI

NC

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

NC

OUT

BI

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

IN

BI

BI

BI

IN

BI

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87

6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

BOM OPTIONS

BOM GROUP

TABLE_BOMGROUP_HEAD

TABLE_BOMGROUP_ITEM

RR/FR: DPHDMIMUX_SEL_TBT, requires 100k pull-up to TBTLC

CR: TBT_GO2SX_BIDIR, requires 100k pull-up to SUS

Requires connection to SMC via 1K series R

platform does not use SD card

R1616 should also be stuffed if

(IPD-PLTRST#)

(IPD-PLTRST#)

GPIO12:

Redwood Ridge: Alias to TBT_CIO_PLUG_EVENT_L, requires pull-up (S0).

Cactus Ridge: Alias to TBT_CIO_PLUG_EVENT, requires pull-down.

Pull-up/down on chipset support page (depends on TBT controller)

(IPD-PLTRST#)

(IPD-DeepSx)

(IPD-RSMRST#)

(IPD)

(IPD)

TBTLC for CR, S0 for RR

Pull-up on TBT page

1/20W

5% 201

MF

10K

R1652

12

MF5%

1/20W

100K

201

R1668

12

MF

2015%

1/20W

100K

R1669

12

MF

2015%

100K

1/20W

R1672

12

MF

2015%

1/20W

100K

R1674

12

MF

2015%

100K

1/20W

R1673

12

MF

2015%

1/20W

100K

R1675

12

MF

2015%

1/20W

100K

R1676

12

100K

1/20W

5% 201

MF

R1678

12

MF

2015%

1/20W

100K

R1677

12

100K

1/20W

5% 201

MF

R1679

12

5%

1/20W

MF

201

100K

R1639

1

2

1/20W

MF

1K

2015%

R1641

12

1/20W

MF

100K

2015%

R1629

12

201

MF

5%

100K

1/20W

R1621

1

2

13

15 16 18

18 23

23 64 66

15 36 45 68

63

15 29

MF

1/20W

100K

5%

201

R1671

1

2

13

15 16 18

15 64

15 18

100K

MF

2015%

1/20W

R1670

12

RAMCFG3:H

1/20W

5%

201

MF

100K

R1631

1

2

1/20W

5%

201

MF

100K

RAMCFG2:H

R1636

1

2

RAMCFG1:H

1/20W

5%

MF

201

100K

R1635

1

2

RAMCFG0:H

100K

1/20W

MF

201

5%

R1611

1

2

24

15

68

2C+GT2

HASWELL-ULT

BGA-TSP

CRITICAL

OMIT_TABLE

U0500

P1

P2

L2

N5

AM2

AT3

AH4

AD6

Y1

T3

AD5

AM4

AN3

AN5

AD7

AK4

AG5

AG3

AB6

U4

Y3

P3

AG6

AP1

AL4

AT5

AU2

AM3

L6

R6

N6

L8

L5

R7

N7

K2

Y2

F3

F2

F1

G4

AM7

AW15

V4

AB21

AF20

E3

F4

D3

E4

C3

E2

C4

T4

V2

D60

G1

J2

J1

K3

J4

J3

K4

G2

15

62

15 68

15 62 68

38

15 68

15 16

15 16 18

15 16 45 68

55

15 30 60 61

15 68

15 63

15 23

15 16

15 16

15 18

15 60

15 45 68 72

15 18

15 68

15 30

15 29

30

15 36

15 63

37 72

15 16

15 16 18

15 16 18

15 16 18

18 23 72

15 16 18

201

MF

1/20W

1K

5%

R1650

1

2

100K

1/20W

5% MF

201

R1610

12

100K

5% 201

1/20W

MF

R1614

12

100K

1/20W

201

MF5%

R1615

12

SD_ON_MLB

1/20W

MF

2015%

100K

R1616

12

201

MF5%

1/20W

100K

R1617

12

MF

2015%

1/20W

100K

R1618

12

5% MF

201

1/20W

100K

R1619

12

MF

1/20W

2015%

100K

R1620

12

MF

201

1/20W

5%

100K

R1622

12

MF

100K

5% 201

1/20W

R1623

12

100K

1/20W

201

MF5%

R1624

12

201

100K

1/20W

MF5%

R1625

12

1/20W

100K

201

MF5%

R1626

12

201

MF

1/20W

100K

5%

R1627

12

100K

1/20W

2015% MF

R1628

12

MF

100K

2015%

1/20W

R1630

12

MF

2015%

1/20W

100K

NO STUFF

R1632

12

100K

1/20W

201

MF5%

R1633

12

1/20W

5% 201

MF

100K

R1634

12

5% MF

1/20W

100K

201

R1640

12

MF

2015%

100K

1/20W

R1637

12

MF

2015%

100K

1/20W

R1638

12

100K

MF

2015%

1/20W

R1691

12

10K

MF

2015%

1/20W

R1694

12

100K

1/20W

5% 201

MF

R1693

12

PLACE_NEAR=U0500.AW15:2.54mm

49.9

201

1%

1/20W

MF

R1655

1

2

100K

MF5%

1/20W

201

R1695

12

MF

2015%

1/20W

100K

R1660

12

100K

MF

2015%

1/20W

R1661

12

100K

1/20W

5% 201

MF

R1662

12

MF

2015%

1/20W

100K

R1663

12

MF

2015%

1/20W

47K

R1664

12

2015%

1/20W

47K

MF

R1665

12

1/20W

5% 201

MF

47K

R1666

12

MF

2015%

1/20W

47K

R1667

12

RAMCFG3:H,RAMCFG2:H,RAMCFG1:H,RAMCFG0:H

RAMCFG_SLOT

PCH GPIO/MISC/LPIO

SYNC_MASTER=J44

SYNC_DATE=08/12/2013

SPIROM_USE_MLB

XDP_SDCONN_STATE_CHANGE_L

PP3V3_S3RS0_CAMERA

TPAD_SPI_IF_EN

JTAG_TBT_TMS_PCH

CAMERA_PWR_EN_PCH

SD_PWR_EN

XDP_JTAG_ISP_TDI

PCH_HSIO_PWR_EN

XDP_JTAG_ISP_TCK

FW_PWR_EN

SSD_DEVSLP

AP_S0IX_WAKE_SEL

PP3V3_S3

PP3V3_S0

PP3V3_S3

PP3V3_S0

PP3V3_S3

HDMITBTMUX_FLAG_L

TPAD_SPI_CS_L

PCH_GSPI0_MOSI

PCH_GSPI0_MISO

PCH_GSPI0_CLK

PCH_GSPI0_CS_L

PCH_UART1_CTS_L

PCH_I2C1_SDA

PCH_I2C0_SCL

PCH_I2C0_SDA

PCH_UART1_RTS_L

PCH_UART1_RXD

PCH_UART1_TXD

TPAD_SPI_CS_L

TPAD_SPI_MOSI

AP_S0IX_WAKE_L

HDMITBTMUX_FLAG_L

JTAG_ISP_TDO

AP_RESET_L

XDP_PCH_GPIO76

XDP_LPCPLUS_GPIO

XDP_PCH_GPIO17

TBT_PWR_EN

XDP_MLB_RAMCFG1

XDP_MLB_RAMCFG3

PP3V3_S0

HDMITBTMUX_SEL_TBT

XDP_JTAG_ISP_TDI

SD_RESET_L

XDP_MLB_RAMCFG1

XDP_MLB_RAMCFG0

XDP_MLB_RAMCFG2

PP1V05_S0

PM_THRMTRIP_L

LPC_SERIRQ

TBT_CIO_PLUG_EVENT_L

PCH_GSPI0_CS_L

PCH_GSPI0_MISO

TPAD_SPI_MISO

PCH_UART1_CTS_L

PCH_UART1_RTS_L

PCH_I2C0_SDA

PCH_HSIO_PWR_EN

FW_PWR_EN

XDP_PCH_GPIO76

MEM_VDD_SEL_1V5_L

XDP_MLB_RAMCFG0

XDP_LPCPLUS_GPIO

JTAG_TBT_TMS_PCH

TPAD_SPI_IF_EN

XDP_MLB_RAMCFG3

CAMERA_PWR_EN_PCH

PCH_STRP_TOPBLK_SWP_L

LCD_PSR_EN

LCD_IRQ_L

ENET_MEDIA_SENSE

PCH_UART1_RXD

PCH_I2C1_SCL

PCH_I2C1_SDA

PCH_I2C0_SCL

PLT_RESET_L

TPAD_SPI_CLK

PCH_OPI_COMP

BT_PWRRST_L

ENET_MEDIA_SENSE

LCD_IRQ_L

PCH_UART1_TXD

PCH_GSPI0_MOSI

PCH_GSPI0_CLK

XDP_PCH_GPIO17

TPAD_SPI_INT_L

SD_RESET_L

SMC_WAKE_SCI_L

SSD_PWR_EN

TPAD_USB_IF_EN

TPAD_SPI_INT_L

FW_PME_L

LPC_SERIRQ

JTAG_ISP_TDO

AP_S0IX_WAKE_SEL

FW_PME_L

SSD_RESET_L

HDD_PWR_EN

PP3V3_S5

LCD_PSR_EN

PCH_I2C1_SCL

TPAD_SPI_CLK

AP_S0IX_WAKE_L

TPAD_SPI_MISO

PP3V3_S0

TPAD_SPI_MOSI

XDP_JTAG_ISP_TCK

PLT_RESET_L

BT_PWRRST_L

TBT_POC_RESET_L

TBT_PWR_EN

SD_PWR_EN

XDP_SDCONN_STATE_CHANGE_L

HDD_PWR_EN

PCH_TBT_PCIE_RESET_L

SSD_PWR_EN

TPAD_USB_IF_EN

SMC_WAKE_SCI_L

PP3V3_S0

SPIROM_USE_MLB

PCH_TCO_TIMER_DISABLE

XDP_MLB_RAMCFG2

SSD_DEVSLP

16 OF 120

<E4LABEL>

<SCH_NUM>

<BRANCH>

15 OF 78

15

45 68 72

15 16 18

31 42

15

15 18

15 18

15 63

15 16

15 60

15 16

15 68

15 30

15 29

15 18 19 39 42 60 65 68

8

11

12 13 15 17 18 24 28 30 37

38 39 40 41 42 43 44 46 47 50

61 62 64 65 68 77

15 18 19 39 42 60 65 68

8

11

12 13 15 17 18 24 28 30 37

38 39 40 41

42 43 44 46 47 50 61 62 64 65

68

77

15 18 19 39 42 60 65 68

15 64

15

15

15

15

15

15

15

15

15

15

15

15

15

15

15 16

15 16 45 68

15 16

15 23

15 16 18

8

11

12 13 15 17 18 24 28 30 37

38 39 40 41 42 43 44 46 47 50

61 62 64 65 68 77

15 16 18

15 16 18

15 16 18

6

8

11

16 17 37 53 57 60 61

65 68

15

15

15

15

15

15

15

15

15

15

15

15

72

15 68

15 68

15 62 68

15

15

15

15

15 63

15 36

15 30 60 61

15

15

15 68

15 36 45 68

15 18

15 68

8

11

13 16 17 18 26 27 29 56 59

60 61 65 68 77

15 62

15

15

15 29

15

8

11

12 13 15 17 18 24 28 30

37 38 39 40 41 42 43 44 46 47

50 61 62 64 65 68 77

15

15

8

11

12 13 15 17 18 24 28 30

37 38 39 40 41 42 43 44 46 47

50 61 62 64 65 68 77

w w w . c h i n a f i x . c o m

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

IN

OUT

IN

OUT

OUT

IN

NC

NC

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

TP

TP

TP

TP

TP

TP

OUT

OUT

OUT

G

D

S G

D

SG

D

S G

D

S

OUT

OUT

OUT

IN

OUT

IN

OUT

IN

IN

TP

OUT

IN

BI

OUT

TP

TP

BI

TP

BI

TP

BI

OUT

BI

IN

OUT

OUT

OUT

OUT

BI

IN

BI

IN

OUT

IN

OUT

BI

TP

IN

OUT

GND

VCC

NCNC

YA

NC

IN

NC

IN

TP

IN

TP

IN

IN

BI

IN

OUT

IN

IN

IN

IN

IN

Apple Inc.

THE INFORMATION CONTAINED HEREIN IS THE

PROPRIETARY PROPERTY OF APPLE INC.

124578

B

D

87

6 5 4 3

C

B

A

NOTICE OF PROPRIETARY PROPERTY:

PAGE

12

D

A

C

PAGE TITLE

SHEET

IV ALL RIGHTS RESERVED

R

D

SIZE

DRAWING NUMBER

REVISION

BRANCH

6 3

THE POSESSOR AGREES TO THE FOLLOWING:

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

II NOT TO REPRODUCE OR COPY IT

NOTE: Should force PCH GPIO47 high to ensure TBT router powered to avoid leakage/clamping of signals.

These signals do not connect to XDP connector in this architecture, only accessible

via Top-Side Probe. Nets are listed here to show XDP associations and to make clear

what restrictions exist on PCH GPIOs when Top-Side Probe is used for PCH debug.

PCH/XDP Signals

USB Overcurrents are aliased, do not cause USB OC# events during PCH debug.

SDCONN_STATE_CHANGE_L is aliased, do not plug/unplug SD Cards during PCH debug.

PCH XDP Signals

VCC_OBS_AB

SSD_PCIEx_SEL_L straps are connected via 1K to common net.

LPCPLUS_GPIO is aliased, do not attempt use during PCH debug.

Unused & MLB_RAMCFGx GPIOs have TPs.

NOTE: Must not short XDP pins together!

Non-XDP Signals

NOTE: XDP_DBRESET_L pulled-up to 3.3V on PCH Support Page

TDI and TMS are terminated in CPU.

HOOK2

TDO

TRSTn

Merged (CPU/PCH) Micro2-XDP

OBSFN_D0

SCL

OBSDATA_D2

OBSDATA_A1

Use with 921-0133 Adapter Flex to

NOTE: This is not the standard XDP pinout.

TCK0

TCK1

SDA

HOOK1

HOOK3

OBSDATA_B3

OBSDATA_B2

PWRGD/HOOK0

OBSDATA_B1

OBSDATA_B0

OBSFN_B0

OBSDATA_A2

OBSDATA_A3

OBSFN_B1

OBSDATA_A0

TDI

TMS

ITPCLK/HOOK4

XDP_PRESENT#

DBR#/HOOK7

OBSDATA_D3

ITPCLK#/HOOK5

OBSFN_D1

OBSDATA_D1

OBSDATA_D0

OBSDATA_C2

OBSDATA_C3

OBSDATA_C1

OBSFN_C1

OBSDATA_C0

OBSFN_C0

518S0847

support chipset debug.

Extra BPM Testpoints

RESET#/HOOK6

VCC_OBS_CD

OBSFN_A1

OBSFN_A0

CPU JTAG Isolation

JTAG_ISP (non-TMS) nets are aliased, do not attempt bit-banged JTAG during PCH debug.

6

70

13

15 18

6

70

6

70

6

70

6

70

6

70

6

70

13

36 72

13 17 36 72

12 16 70

17 72

6

70

12

16 70

12 16 70

5% 201

1/20W

MF

XDP

1K

PLACE_NEAR=U0500.AG7:2.54mm

R1805

12

5% 201

1/20W

MF

XDP

51

PLACE_NEAR=U0500.E60:28mm

R1813

21

5%

0

402

MF-LF

XDP

1/16W

R1804

12

5%

0

0201

1/20W

MF

XDP

PLACE_NEAR=U5000.J3:2.54mm

R1802

12

5% 201

1/20W

MF

1K

XDP

PLACE_NEAR=U0500.C61:2.54mm

R1800

12

6

70

M-ST-SM1

CRITICAL

DF40RC-60DP-0.4V

XDP_CONN

J1800

1

10

1112

1314

1516

1718

19

2

20

2122

2324

2526

2728

29

3

30

3132

3334

3536

3738

39

4

40

4142

4344

4546

4748

49

5

50

5152

5354

5556

5758

59

6

60

61

62

6364

78

9

6

70

6

70

6

70

6

70

6

70

6

70

6

70

6

70

6

70

6

70

TP-P6

TP1806

1

TP-P6

TP1807

1

TP-P6

TP1805

1

TP-P6

TP1804

1

TP-P6

TP1803

1

TP-P6

TP1802

1

8

5%

150

402

MF-LF

1/16W

R1830

1

2

5% 201

1/20W

MF

51

XDP

PLACE_NEAR=U0500.F62:28mm

R1810

12

12

16 70

5%

XDP

MF-LF

402

1/16W

1K

R1831

1

2

5% 201

1/20W

MF

51

PLACE_NEAR=U0500.AE62:28mm

NO STUFF

R1896

21

5% 201

1/20W

MF

51

XDP

PLACE_NEAR=U0500.AD62:28mm

R1892

21

5% 201

1/20W

MF

51

XDP

PLACE_NEAR=U0500.AD61:28mm

R1891

21

5% 201

1/20W

MF

XDP

51

PLACE_NEAR=U0500.AE61:28mm

R1890

21

5% 201

1/20W

MF

1K

PLACE_NEAR=U0500.AE63:28mm

NO STUFF

R1899

21

5%

0

0201

1/20W

MF

XDP

PLACE_NEAR=J1800.58:28mm

R1835

12

12

16 70

PLACE_NEAR=J1800.57:28mm

XDP

SOT-563

DMN5L06VK-7

CRITICAL

Q1842

6

2

1

XDP

SOT-563

DMN5L06VK-7

CRITICAL

PLACE_NEAR=J1800.51:28mm

Q1840

3

5

4

PLACE_NEAR=J1800.55:28mm

CRITICAL

XDP

DMN5L06VK-7

SOT-563

Q1842

3

5

4

CRITICAL

XDP

DMN5L06VK-7

SOT-563

PLACE_NEAR=J1800.53:28mm

Q1840

6

2

1

6

12

16 70

6

70

6

70

6

16

70

XDP

CERM-X5R

0201

6.3V

0.1UF

10%

C1801

1

2

15

16 18

14

14 16 63

6

70

14 16

63

TP-P6

TP1870

1

14

16 33 14 16 33

15 18

14

TP-P6

TP1874

1

XDP

CERM-X5R

0201

6.3V

0.1UF

10%

C1800

1

2

TP-P6

TP1876

1

15

18

TP-P6

TP1877

1

15

18

TP-P6

TP1878

1

15

18

12

15

15 18 23

12

12

12

5% 201

1/20W

MF

1K

R1881

12

5% 201

1/20W

MF

1K

R1882

12

6

70

5% 201

1/20W

MF

1K

R1883

12

5% 201

1/20W

MF

1K

R1884

12

30

15

16 45 68

6

70

15

15 18

23

15 16 45 68

TP-P6

TP1887

1

XDP

CERM-X5R

0201

6.3V

0.1UF

10%

C1804

1

2

XDP

CERM-X5R

0201

6.3V

0.1UF

10%

C1806

1

2

6

70

6

12

16 70

5% 201

1/20W

MF

PLACE_NEAR=U0500.AU62:28mm

NO STUFF

51

R1897

21

74LVC1G07GF

SOT891

U1845

2

3

1

5

6

4

16V

0201

X5R-CERM

0.1UF

10%

C1845

1

2

6

70

5%

201

1/20W

MF

330K

R1845

1

2

17

36 61

TP-P6

TP1873

1

15

16 18

TP-P6

TP1886

1

6

70

6

70

14

19 39 63 68 72

14 19 39 63 68 72

6

16

70

6

70

8

17

70

6

70

6

70

6

70

SYNC_MASTER=J44

CPU/PCH Merged XDP

SYNC_DATE=08/12/2013

CPU_PWR_DEBUG

CPU_CFG<4>

XDP_SYS_PWROK

PP3V3_S5

ALL_SYS_PWRGD

PP5V_S0

XDP_PCH_TMS

XDP_PCH_TMS

XDP_CPUPCH_TRST_L

CPU_CFG<1>

XDP_PCH_TDO

XDP_PCH_TDI

XDP_CPU_PRESENT_L

MAKE_BASE=TRUE

XDP_CPUPCH_TRST_L

XDP_CPU_TCK

XDP_BPM_L<6>

XDP_BPM_L<7>

XDP_BPM_L<5>

XDP_BPM_L<4>

XDP_BPM_L<3>

XDP_BPM_L<2>

PP1V05_SUS

PCH_JTAGX

XDP_PCH_TDI

XDP_CPU_TDO

XDP_PCH_TDO

PP1V05_S0

XDP_CPU_PRDY_L

XDP_CPU_PREQ_L

CPU_CFG<0>

CPU_CFG<2>

XDP_BPM_L<1>

XDP_BPM_L<0>

CPU_CFG<5>

CPU_CFG<6>

CPU_CFG<7>

SMBUS_PCH_CLK

XDP_PCH_TCK

CPU_VCCST_PWRGD

XDP_CPU_PWRBTN_L

PP1V05_S0

CPU_CFG<3>

PM_PWRBTN_L

PCH_JTAGX

PM_PCH_SYS_PWROK

CPU_CFG<17>

CPU_CFG<16>

CPU_CFG<8>

CPU_CFG<9>

CPU_CFG<18>

CPU_CFG<12>

CPU_CFG<13>

CPU_CFG<14>

CPU_CFG<15>

XDP_CPURST_L

PLT_RESET_L

XDP_CPU_TDO

XDP_CPUPCH_TRST_L

XDP_CPUPCH_TRST_L

XDP_CPU_TDI

XDP_CPU_TMS

CPU_CFG<10>

CPU_CFG<11>

CPU_CFG<19>

XDP_PCH_TCK

XDP_TRST_L

XDP_DBRESET_L

XDP_JTAG_CPU_ISOL_L

XDP_CPU_VCCST_PWRGD

XDP_CPU_TCK

SSD_PCIE_SEL_L

XDP_USB_EXTA_OC_L

XDP_USB_EXTB_OC_L

XDP_SDCONN_STATE_CHANGE_L

JTAG_ISP_TCK

XDP_LPCPLUS_GPIO

XDP_MLB_RAMCFG0

XDP_USB_EXTA_OC_L

MAKE_BASE=TRUE

XDP_USB_EXTB_OC_L

MAKE_BASE=TRUE

XDP_USB_EXTC_OC_L

MAKE_BASE=TRUE

XDP_SDCONN_STATE_CHANGE_L

XDP_USB_EXTD_OC_L

XDP_MLB_RAMCFG1

MAKE_BASE=TRUE

XDP_JTAG_ISP_TCK

XDP_SSD_PCIE1_SEL_L

XDP_PCH_GPIO76

MAKE_BASE=TRUE

XDP_JTAG_ISP_TDI

SMBUS_PCH_DATA

JTAG_ISP_TDI

MAKE_BASE=TRUE

XDP_LPCPLUS_GPIO

XDP_SSD_PCIE0_SEL_L

XDP_SSD_PCIE2_SEL_L

XDP_PCH_GPIO17

XDP_SSD_PCIE3_SEL_L

XDP_MLB_RAMCFG3

XDP_MLB_RAMCFG2

18 OF 120

<E4LABEL>

<SCH_NUM>

<BRANCH>

16 OF 78

72

8

11

13 15 17 18 26 27 29 56

59 60 61 65 68 77

17 32 41 44 45 53 54 58 60 61

65 68

12 16 70

6

12

16 70

6

12

16 70

6

16

70

59 65

12 16 70

12 16 70

6

16

70

12 16 70

6

8

11

15 16 17 37 53 57 60

61 65 68

72

6

8

11

15 16 17 37 53 57 60

61 65 68

12 16 70

70

70

剩余77页未读,继续阅读

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-11-25 上传

2020-11-25 上传

2022-02-28 上传

2023-03-01 上传

2020-11-25 上传

clx0430

- 粉丝: 1

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功