没有合适的资源?快使用搜索试试~ 我知道了~

首页ADV7842软件控制使用手册

资源详情

资源评论

资源推荐

Software User Guide

UG-206

One Technology Way • P. O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Te l: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

ADV7842 I

2

C Register Maps

1

This software user guide documents the I

2

C register maps for the ADV7842. The ADV7842 is a dual HDMI® fast switching receiver with a

12-bit, 170 MHz video and graphics digitizer and a 3D comb filter decoder.

This user guide consists of three sections. The first section provides detailed register tables for the register maps of twelve functional

blocks. The second section provides detailed signal documentation for each register. The third section consists of a detailed index.

2

TABLE OF CONTENTS

1 Register Tables ......................................................................................................................................... 3

1.1 IO Map .................................................................................................................................................................................. 3

1.2 CP Map ................................................................................................................................................................................. 9

1.3 VDP Map ............................................................................................................................................................................ 16

1.4 AFE Map ............................................................................................................................................................................. 22

1.5 SDP Map ............................................................................................................................................................................. 24

1.6 CEC Map ............................................................................................................................................................................. 28

1.7 AVLINK Map ....................................................................................................................................................................... 32

1.8 SDP IO Map ........................................................................................................................................................................ 36

1.9 HDMI Map .......................................................................................................................................................................... 40

1.10 Repeater Map .................................................................................................................................................................... 44

1.11 Infoframe Map .................................................................................................................................................................. 48

1.12 DPLL Map ........................................................................................................................................................................... 55

2 Signal Documentation .......................................................................................................................... 56

2.1 IO Map ................................................................................................................................................................................ 56

2.2 CP Map ............................................................................................................................................................................. 110

2.3 VDP Map .......................................................................................................................................................................... 130

2.4 AFE Map ........................................................................................................................................................................... 139

2.5 SDP Map ........................................................................................................................................................................... 149

2.6 CEC Map ........................................................................................................................................................................... 164

2.7 AVLINK Map ..................................................................................................................................................................... 171

2.8 SDP IO Map ...................................................................................................................................................................... 177

2.9 HDMI Map ........................................................................................................................................................................ 185

2.10 Repeater Map .................................................................................................................................................................. 198

2.11 Infoframe Map ................................................................................................................................................................ 204

2.12 DPLL Map ......................................................................................................................................................................... 210

3 Index ...................................................................................................................................................... 211

REVISION HISTORY

11/10-Revision 0: Initial Version

ADV7842 Software User Guide Rev. 0

3

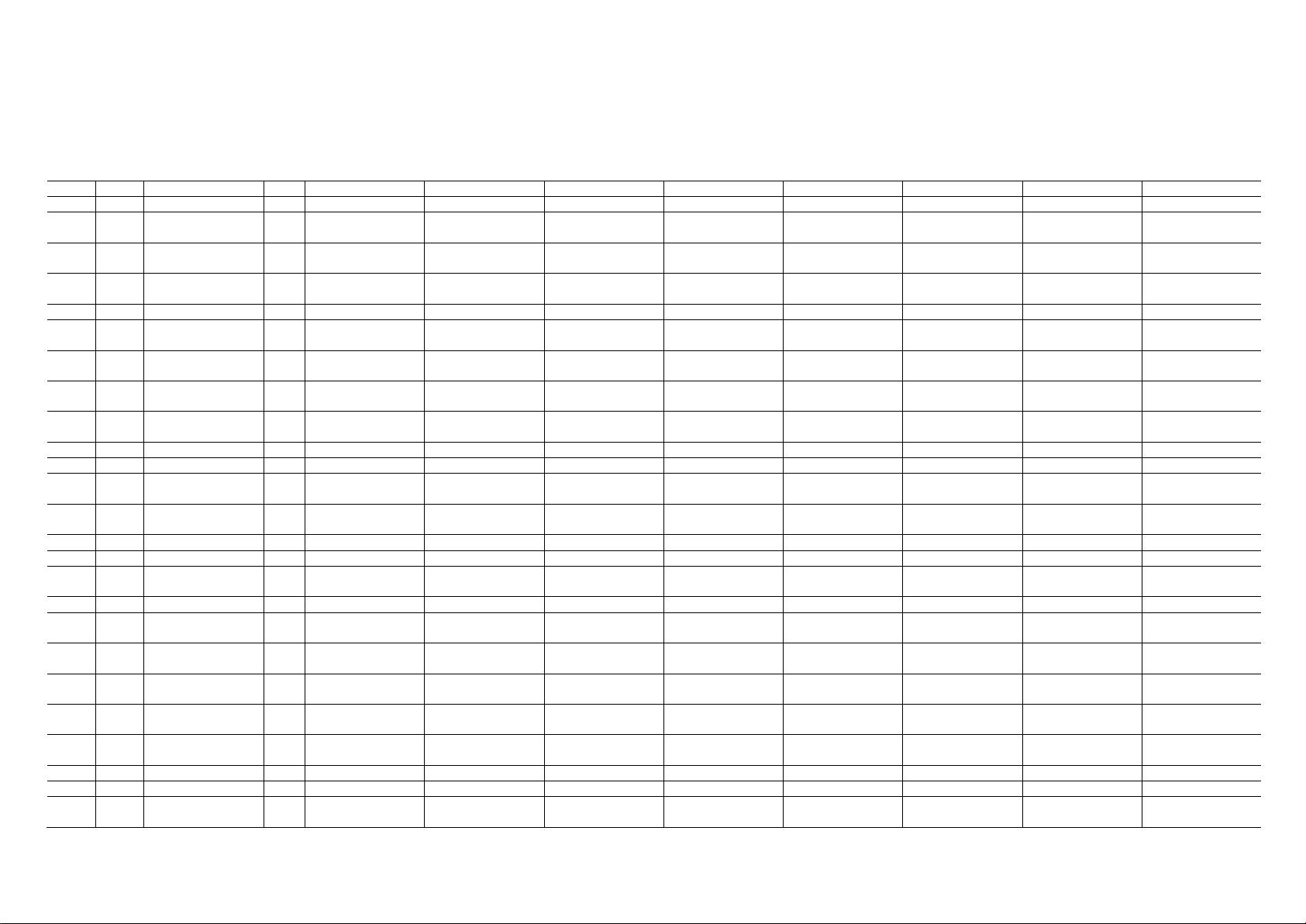

1 REGISTER TABLES

1.1 IO MAP

ADD

DEF

REGISTER NAME

ACC

7

6

5

4

3

2

1

0

0x00

0x08

VIDEO STANDARD

rw

-

-

VID_STD[5]

VID_STD[4]

VID_STD[3]

VID_STD[2]

VID_STD[1]

VID_STD[0]

0x01

0x06

PRIMARY MODE

rw

ADC_HDMI_SIMUL

T_MODE

V_FREQ[2]

V_FREQ[1]

V_FREQ[0]

PRIM_MODE[3]

PRIM_MODE[2]

PRIM_MODE[1]

PRIM_MODE[0]

0x02

0xF0

IO_REG_02

rw

INP_COLOR_SPAC

E[3]

INP_COLOR_SPAC

E[2]

INP_COLOR_SPAC

E[1]

INP_COLOR_SPAC

E[0]

ALT_GAMMA

OP_656_RANGE

RGB_OUT

ALT_DATA_SAT

0x03

0x00

IO_REG_03

rw

OP_FORMAT_SEL[

7]

OP_FORMAT_SEL[

6]

OP_FORMAT_SEL[

5]

OP_FORMAT_SEL[

4]

OP_FORMAT_SEL[

3]

OP_FORMAT_SEL[

2]

OP_FORMAT_SEL[

1]

OP_FORMAT_SEL[

0]

0x04

0x62

rw

OP_CH_SEL[2]

OP_CH_SEL[1]

OP_CH_SEL[0]

-

-

-

-

-

0x05

0x2C

IO_REG_05

rw

-

-

-

F_OUT_SEL

DATA_BLANK_EN

AVCODE_INSERT_

EN

REPL_AV_CODE

OP_SWAP_CB_CR

0x06

0xA0

IO_REG_06

rw

VS_OUT_SEL

HS_OUT_SEL[1]

HS_OUT_SEL[0]

INV_SYNC_OUT_P

OL

INV_F_POL

INV_VS_POL

INV_HS_POL

INV_LLC_POL

0x07

0x40

IO_REG_07

rw

SYNC_CH_AUTO_

MODE

SYNC_CH1_PRIORI

TY

SYNC_CH1_HS_SE

L[1]

SYNC_CH1_HS_SE

L[0]

SYNC_CH1_VS_SE

L[1]

SYNC_CH1_VS_SE

L[0]

SYNC_CH1_EMB_

SYNC_SEL[1]

SYNC_CH1_EMB_

SYNC_SEL[0]

0x08

0x14

IO_REG_08

rw

-

-

SYNC_CH2_HS_SE

L[1]

SYNC_CH2_HS_SE

L[0]

SYNC_CH2_VS_SE

L[1]

SYNC_CH2_VS_SE

L[0]

SYNC_CH2_EMB_

SYNC_SEL[1]

SYNC_CH2_EMB_

SYNC_SEL[0]

0x0B

0x44

IO_REG_0B

rw

-

SEL_RAW_CS

-

-

-

-

CORE_PDN

XTAL_PDN

0x0C

0x62

IO_REG_0C

rw

-

-

POWER_DOWN

-

-

CP_PWRDN

VDP_PDN

PADS_PDN

0x12

0x00

IO_REG_12

r

SEL_SYNC_CHAN

NEL

-

-

CP_STDI_INTERLA

CED

CP_INTERLACED

CP_PROG_PARM_

FOR_INT

CP_FORCE_INTERL

ACED

CP_NON_STD_VID

EO

0x13

0x00

IO_REG_13

r

-

-

-

-

-

-

CP_CURRENT_SYN

C_SRC[1]

CP_CURRENT_SYN

C_SRC[0]

0x14

0x6A

IO_REG_14

rw

-

-

DR_STR[1]

DR_STR[0]

DR_STR_CLK[1]

DR_STR_CLK[0]

DR_STR_SYNC[1]

DR_STR_SYNC[0]

0x15

0xBE

IO_REG_15

rw

-

-

TRI_SYNC_OUT

TRI_AUDIO

TRI_SYNCS

TRI_LLC

TRI_PIX

-

0x16

0x43

IO_REG_16

rw

PLL_DIV_MAN_EN

-

-

PLL_DIV_RATIO[12

]

PLL_DIV_RATIO[11

]

PLL_DIV_RATIO[10

]

PLL_DIV_RATIO[9]

PLL_DIV_RATIO[8]

0x17

0x5A

rw

PLL_DIV_RATIO[7]

PLL_DIV_RATIO[6]

PLL_DIV_RATIO[5]

PLL_DIV_RATIO[4]

PLL_DIV_RATIO[3]

PLL_DIV_RATIO[2]

PLL_DIV_RATIO[1]

PLL_DIV_RATIO[0]

0x19

0x00

LLC_DLL

rw

LLC_DLL_EN

LLC_DLL_DOUBLE

-

LLC_DLL_PHASE[4

]

LLC_DLL_PHASE[3

]

LLC_DLL_PHASE[2

]

LLC_DLL_PHASE[1

]

LLC_DLL_PHASE[0

]

0x1A

0x02

SUB_I2C_CONTRO

L

rw

-

-

-

-

-

-

SUBI2C_EN

VDP_ON_SUB_I2C

0x20

0xF0

HPA_REG1

rw

-

-

HPA_MAN_VALUE

_A

HPA_MAN_VALUE

_B

-

-

HPA_TRISTATE_A

HPA_TRISTATE_B

0x21

0x00

HPA_REG2

r

-

-

-

-

-

-

HPA_STATUS_POR

T_A

HPA_STATUS_POR

T_B

0x30

0x88

IO_REG_30

rw

-

-

-

PIXBUS_MSB_TO_

LSB_REORDER

-

-

-

-

0x33

0x00

IO_REG_33

rw

-

LLC_DLL_MUX

-

-

-

-

-

-

0x3F

0x00

INT STATUS

r

-

-

-

-

-

-

INTRQ_RAW

INTRQ2_RAW

0x40

0x20

INT1_CONFIGURA

TION

rw

INTRQ_DUR_SEL[1

]

INTRQ_DUR_SEL[0

]

-

STORE_UNMASKE

D_IRQS

EN_MUTE_OUT_I

NTRQ

MPU_STIM_INTRQ

INTRQ_OP_SEL[1]

INTRQ_OP_SEL[0]

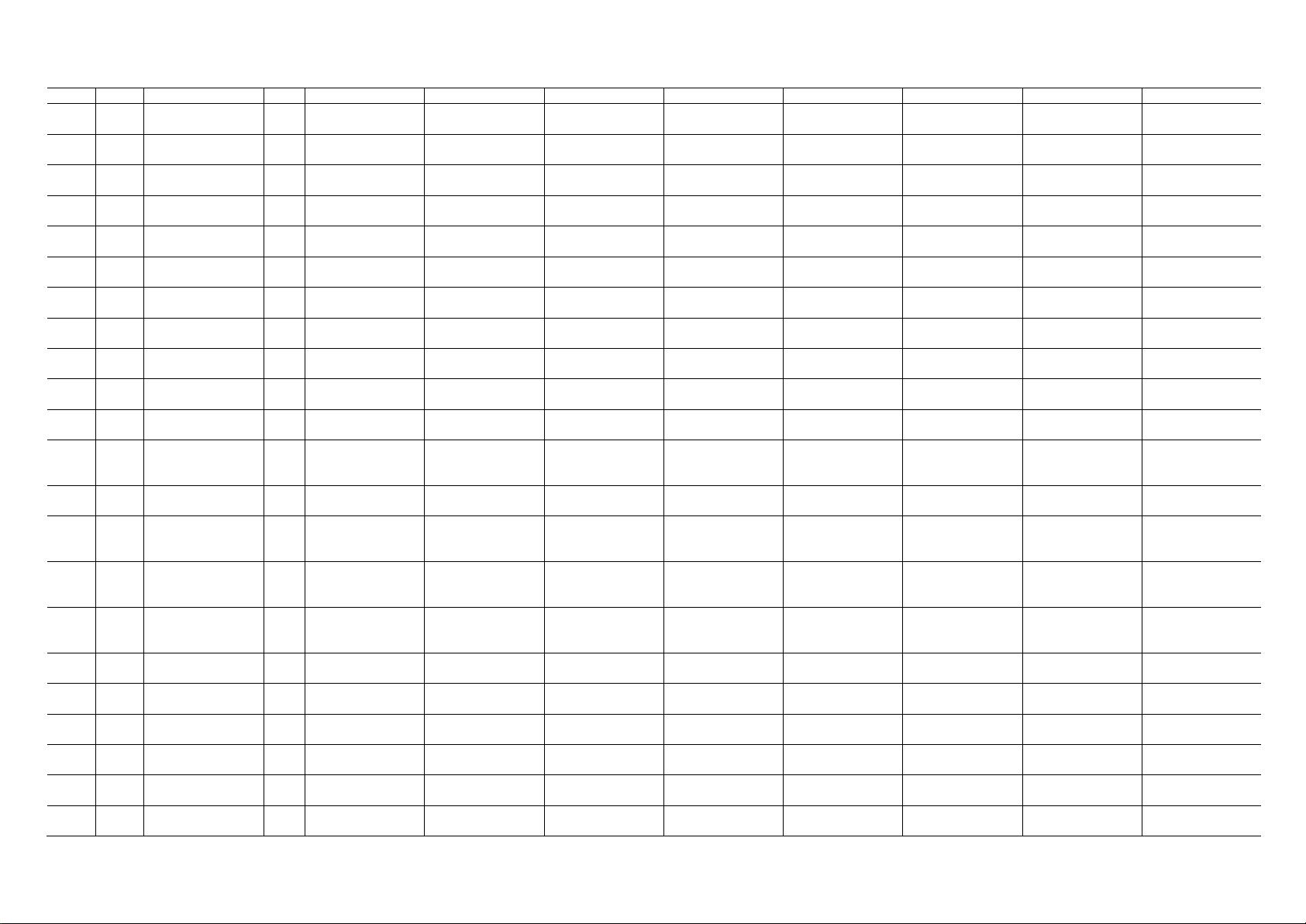

ADV7842 Software User Guide Rev. 0

4

ADD

DEF

REGISTER NAME

ACC

7

6

5

4

3

2

1

0

0x41

0x30

INT2_CONFIGURA

TION

rw

INTRQ2_DUR_SEL[

1]

INTRQ2_DUR_SEL[

0]

CP_LOCK_UNLOC

K_EDGE_SEL

STDI_DATA_VALID

_EDGE_SEL

EN_MUTE_OUT_I

NTRQ2

INT2_EN

INTRQ2_OP_SEL[1

]

INTRQ2_OP_SEL[0

]

0x42

0x00

RAW_STATUS_1

r

SSPD_RSLT_CHNG

D_RAW

MV_PS_DET_RAW

-

STDI_DATA_VALID

_RAW

CP_UNLOCK_RAW

CP_LOCK_RAW

-

AFE_INTERRUPT_R

AW

0x43

0x00

INTERRUPT_STATU

S_1

r

SSPD_RSLT_CHNG

D_ST

MV_PS_DET_ST

-

STDI_DATA_VALID

_ST

CP_UNLOCK_ST

CP_LOCK_ST

-

AFE_INTERRUPT_S

T

0x44

0x00

INTERRUPT_CLEAR

_1

sc

SSPD_RSLT_CHNG

D_CLR

MV_PS_DET_CLR

-

STDI_DATA_VALID

_CLR

CP_UNLOCK_CLR

CP_LOCK_CLR

-

AFE_INTERRUPT_

CLR

0x45

0x00

INTERRUPT2_MAS

KB_1

rw

SSPD_RSLT_CHNG

D_MB2

MV_PS_DET_MB2

-

STDI_DATA_VALID

_MB2

CP_UNLOCK_MB2

CP_LOCK_MB2

-

AFE_INTERRUPT_

MB2

0x46

0x00

INTERRUPT_MASK

B_1

rw

SSPD_RSLT_CHNG

D_MB1

MV_PS_DET_MB1

-

STDI_DATA_VALID

_MB1

CP_UNLOCK_MB1

CP_LOCK_MB1

-

AFE_INTERRUPT_

MB1

0x47

0x00

RAW_STATUS_2

r

MPU_STIM_INTRQ

_RAW

MV_AGC_DET_RA

W

MV_CS_DET_RAW

-

-

CP_CGMS_CHNG

D_RAW

-

-

0x48

0x00

INTERRUPT_STATU

S_2

r

MPU_STIM_INTRQ

_ST

MV_AGC_DET_ST

MV_CS_DET_ST

-

-

CP_CGMS_CHNG

D_ST

-

-

0x49

0x00

INTERRUPT_CLEAR

_2

sc

MPU_STIM_INTRQ

_CLR

MV_AGC_DET_CL

R

MV_CS_DET_CLR

-

-

CP_CGMS_CHNG

D_CLR

-

-

0x4A

0x00

INTERRUPT2_MAS

KB_2

rw

MPU_STIM_INTRQ

_MB2

MV_AGC_DET_MB

2

MV_CS_DET_MB2

-

-

CP_CGMS_CHNG

D_MB2

-

-

0x4B

0x00

INTERRUPT_MASK

B_2

rw

MPU_STIM_INTRQ

_MB1

MV_AGC_DET_MB

1

MV_CS_DET_MB1

-

-

CP_CGMS_CHNG

D_MB1

-

-

0x4C

0x00

AVLINK_RAW_STA

TUS

r

-

-

-

-

AVLINK_RX_READ

Y_RAW

AVLINK_TX_RETRY

_TIMEOUT_RAW

AVLINK_TX_ARBIT

RATION_LOST_RA

W

AVLINK_TX_READ

Y_RAW

0x4D

0x00

INTERRUPT_STATU

S_3

r

-

-

-

-

AVLINK_RX_READ

Y_ST

AVLINK_TX_RETRY

_TIMEOUT_ST

AVLINK_TX_ARBIT

RATION_LOST_ST

AVLINK_TX_READ

Y_ST

0x4E

0x00

INTERRUPT_CLEAR

_3

sc

-

-

-

-

AVLINK_RX_READ

Y_CLR

AVLINK_TX_RETRY

_TIMEOUT_CLR

AVLINK_TX_ARBIT

RATION_LOST_CL

R

AVLINK_TX_READ

Y_CLR

0x4F

0x00

INTERRUPT2_MAS

KB_3

rw

-

-

-

-

AVLINK_RX_READ

Y_MB2

AVLINK_TX_RETRY

_TIMEOUT_MB2

AVLINK_TX_ARBIT

RATION_LOST_MB

2

AVLINK_TX_READ

Y_MB2

0x50

0x00

INTERRUPT_MASK

B_3

rw

-

-

-

-

AVLINK_RX_READ

Y_MB1

AVLINK_TX_RETRY

_TIMEOUT_MB1

AVLINK_TX_ARBIT

RATION_LOST_MB

1

AVLINK_TX_READ

Y_MB1

0x51

0x00

RAW_STATUS_4

r

TTXT_AVL_RAW

VITC_AVL_RAW

GS_DATA_TYPE_R

AW

GS_PDC_VPS_UTC

_AVL_RAW

FASTI2C_DATA_RD

Y_RAW

CGMS_WSS_AVL_

RAW

CCAP_EVEN_FIEL

D_RAW

CCAP_AVL_RAW

0x52

0x00

INTERRUPT_STATU

S_4

r

TTXT_AVL_ST

VITC_AVL_ST

GS_DATA_TYPE_S

T

GS_PDC_VPS_UTC

_AVL_ST

FASTI2C_DATA_RD

Y_ST

CGMS_WSS_AVL_

ST

CCAP_EVEN_FIEL

D_ST

CCAP_AVL_ST

0x53

0x00

INTERRUPT_CLEAR

_4

sc

TTXT_AVL_CLR

VITC_AVL_CLR

GS_DATA_TYPE_C

LR

GS_PDC_VPS_UTC

_AVL_CLR

FASTI2C_DATA_RD

Y_CLR

CGMS_WSS_AVL_

CLR

CCAP_EVEN_FIEL

D_CLR

CCAP_AVL_CLR

0x54

0x00

INTERRUPT2_MAS

KB_4

rw

TTXT_AVL_MB2

VITC_AVL_MB2

GS_DATA_TYPE_M

B2

GS_PDC_VPS_UTC

_AVL_MB2

FASTI2C_DATA_RD

Y_MB2

CGMS_WSS_AVL_

MB2

CCAP_EVEN_FIEL

D_MB2

CCAP_AVL_MB2

0x55

0x00

INTERRUPT_MASK

B_4

rw

TTXT_AVL_MB1

VITC_AVL_MB1

GS_DATA_TYPE_M

B1

GS_PDC_VPS_UTC

_AVL_MB1

FASTI2C_DATA_RD

Y_MB1

CGMS_WSS_AVL_

MB1

CCAP_EVEN_FIEL

D_MB1

CCAP_AVL_MB1

0x56

0x00

RAW_STATUS_5

r

SDP_PROGRESSIV

E_RAW

SDP_PR_DET_RA

W

SDP_SD_DET_RA

W

SDP_50HZ_DET_R

AW

-

-

-

-

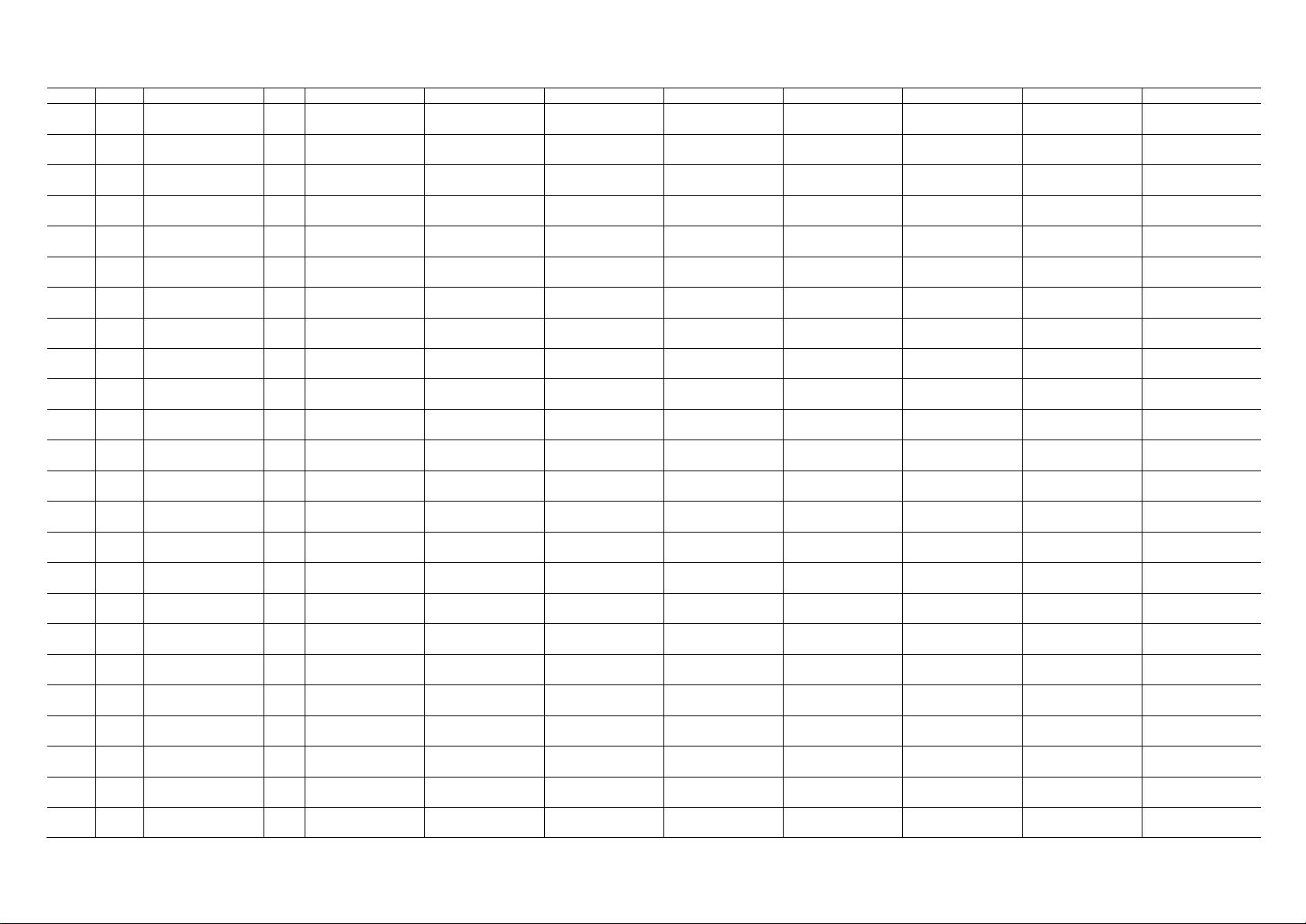

ADV7842 Software User Guide Rev. 0

5

ADD

DEF

REGISTER NAME

ACC

7

6

5

4

3

2

1

0

0x57

0x00

INTERRUPT_STATU

S_5

r

SDP_PROGRESSIV

E_ST

SDP_PR_DET_ST

SDP_SD_DET_ST

SDP_50HZ_DET_S

T

-

-

-

-

0x58

0x00

INTERRUPT_CLEAR

_5

sc

SDP_PROGRESSIV

E_CLR

SDP_PR_DET_CLR

SDP_SD_DET_CLR

SDP_50HZ_DET_C

LR

-

-

-

-

0x59

0x00

INTERRUPT2_MAS

KB_5

rw

SDP_PROGRESSIV

E_MB2

SDP_PR_DET_MB2

SDP_SD_DET_MB

2

SDP_50HZ_DET_

MB2

-

-

-

-

0x5A

0x00

INTERRUPT_MASK

B_5

rw

SDP_PROGRESSIV

E_MB1

SDP_PR_DET_MB1

SDP_SD_DET_MB

1

SDP_50HZ_DET_

MB1

-

-

-

-

0x5B

0x00

RAW_STATUS_6

r

CP_LOCK_CH2_RA

W

CP_UNLOCK_CH2

_RAW

STDI_DVALID_CH2

_RAW

SSPD_RSLT_CHNG

D_CH2_RAW

CP_LOCK_CH1_RA

W

CP_UNLOCK_CH1

_RAW

STDI_DVALID_CH1

_RAW

SSPD_RSLT_CHNG

D_CH1_RAW

0x5C

0x00

INTERRUPT_STATU

S_6

r

CP_LOCK_CH2_ST

CP_UNLOCK_CH2

_ST

STDI_DVALID_CH2

_ST

SSPD_RSLT_CHNG

D_CH2_ST

CP_LOCK_CH1_ST

CP_UNLOCK_CH1

_ST

STDI_DVALID_CH1

_ST

SSPD_RSLT_CHNG

D_CH1_ST

0x5D

0x00

INTERRUPT_CLEAR

_6

sc

CP_LOCK_CH2_CL

R

CP_UNLOCK_CH2

_CLR

STDI_DVALID_CH2

_CLR

SSPD_RSLT_CHNG

D_CH2_CLR

CP_LOCK_CH1_CL

R

CP_UNLOCK_CH1

_CLR

STDI_DVALID_CH1

_CLR

SSPD_RSLT_CHNG

D_CH1_CLR

0x5E

0x00

INTERRUPT2_MAS

KB_6

rw

CP_LOCK_CH2_M

B2

CP_UNLOCK_CH2

_MB2

STDI_DVALID_CH2

_MB2

SSPD_RSLT_CHNG

D_CH2_MB2

CP_LOCK_CH1_M

B2

CP_UNLOCK_CH1

_MB2

STDI_DVALID_CH1

_MB2

SSPD_RSLT_CHNG

D_CH1_MB2

0x5F

0x00

INTERRUPT_MASK

B_6

rw

CP_LOCK_CH2_M

B1

CP_UNLOCK_CH2

_MB1

STDI_DVALID_CH2

_MB1

SSPD_RSLT_CHNG

D_CH2_MB1

CP_LOCK_CH1_M

B1

CP_UNLOCK_CH1

_MB1

STDI_DVALID_CH1

_MB1

SSPD_RSLT_CHNG

D_CH1_MB1

0x60

0x00

HDMI LVL RAW

STATUS 1

r

ISRC2_PCKT_RAW

ISRC1_PCKT_RAW

ACP_PCKT_RAW

VS_INFO_RAW

MS_INFO_RAW

SPD_INFO_RAW

AUDIO_INFO_RA

W

AVI_INFO_RAW

0x61

0x00

HDMI LVL INT

STATUS 1

r

ISRC2_PCKT_ST

ISRC1_PCKT_ST

ACP_PCKT_ST

VS_INFO_ST

MS_INFO_ST

SPD_INFO_ST

AUDIO_INFO_ST

AVI_INFO_ST

0x62

0x00

HDMI LVL INT CLR

1

sc

ISRC2_PCKT_CLR

ISRC1_PCKT_CLR

ACP_PCKT_CLR

VS_INFO_CLR

MS_INFO_CLR

SPD_INFO_CLR

AUDIO_INFO_CLR

AVI_INFO_CLR

0x63

0x00

HDMI LVL INT2

MASKB 1

rw

ISRC2_PCKT_MB2

ISRC1_PCKT_MB2

ACP_PCKT_MB2

VS_INFO_MB2

MS_INFO_MB2

SPD_INFO_MB2

AUDIO_INFO_MB2

AVI_INFO_MB2

0x64

0x00

HDMI LVL INT

MASKB 1

rw

ISRC2_PCKT_MB1

ISRC1_PCKT_MB1

ACP_PCKT_MB1

VS_INFO_MB1

MS_INFO_MB1

SPD_INFO_MB1

AUDIO_INFO_MB1

AVI_INFO_MB1

0x65

0x00

HDMI LVL RAW

STATUS 2

r

CS_DATA_VALID_

RAW

INTERNAL_MUTE_

RAW

AV_MUTE_RAW

AUDIO_CH_MD_R

AW

HDMI_MODE_RA

W

GEN_CTL_PCKT_R

AW

AUDIO_C_PCKT_R

AW

GAMUT_MDATA_R

AW

0x66

0x00

HDMI LVL INT

STATUS 2

r

CS_DATA_VALID_S

T

INTERNAL_MUTE_

ST

AV_MUTE_ST

AUDIO_CH_MD_S

T

HDMI_MODE_ST

GEN_CTL_PCKT_S

T

AUDIO_C_PCKT_S

T

GAMUT_MDATA_S

T

0x67

0x00

HDMI LVL INT CLR

2

sc

CS_DATA_VALID_

CLR

INTERNAL_MUTE_

CLR

AV_MUTE_CLR

AUDIO_CH_MD_C

LR

HDMI_MODE_CLR

GEN_CTL_PCKT_C

LR

AUDIO_C_PCKT_C

LR

GAMUT_MDATA_

CLR

0x68

0x00

HDMI LVL INT2

MASKB 2

rw

CS_DATA_VALID_

MB2

INTERNAL_MUTE_

MB2

AV_MUTE_MB2

AUDIO_CH_MD_

MB2

HDMI_MODE_MB

2

GEN_CTL_PCKT_

MB2

AUDIO_C_PCKT_

MB2

GAMUT_MDATA_

MB2

0x69

0x00

HDMI LVL INT

MASKB 2

rw

CS_DATA_VALID_

MB1

INTERNAL_MUTE_

MB1

AV_MUTE_MB1

AUDIO_CH_MD_

MB1

HDMI_MODE_MB

1

GEN_CTL_PCKT_

MB1

AUDIO_C_PCKT_

MB1

GAMUT_MDATA_

MB1

0x6A

0x00

HDMI LVL RAW

STATUS 3

r

-

-

TMDSPLL_LCK_A_

RAW

TMDSPLL_LCK_B_

RAW

-

-

TMDS_CLK_A_RA

W

TMDS_CLK_B_RA

W

0x6B

0x00

HDMI LVL INT

STATUS 3

r

-

-

TMDSPLL_LCK_A_

ST

TMDSPLL_LCK_B_

ST

-

-

TMDS_CLK_A_ST

TMDS_CLK_B_ST

0x6C

0x00

HDMI LVL INT CLR

3

sc

-

-

TMDSPLL_LCK_A_

CLR

TMDSPLL_LCK_B_

CLR

-

-

TMDS_CLK_A_CLR

TMDS_CLK_B_CLR

0x6D

0x00

HDMI LVL INT2

MASKB 3

rw

-

-

TMDSPLL_LCK_A_

MB2

TMDSPLL_LCK_B_

MB2

-

-

TMDS_CLK_A_MB

2

TMDS_CLK_B_MB

2

0x6E

0x00

HDMI LVL INT

MASKB 3

rw

-

-

TMDSPLL_LCK_A_

MB1

TMDSPLL_LCK_B_

MB1

-

-

TMDS_CLK_A_MB

1

TMDS_CLK_B_MB

1

ADV7842 Software User Guide Rev. 0

剩余231页未读,继续阅读

锦壹

- 粉丝: 0

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1