没有合适的资源?快使用搜索试试~ 我知道了~

首页BCM5389 data sheet

BCM5389 data sheet

BCM 5389 data sheet,关于BCM 5389 Switch 芯片的手册

资源详情

资源评论

资源推荐

2/28/2007 Y4XMF

Preliminary Data Sheet

BCM5387

5389-DS06-R

16215 Alton Parkway • P.O. Box 57013 • Irvine, CA 92619-7013 • Phone: 949-450-8700 • Fax: 949-450-8710 2/28/07

Single-Chip 8-Port SerDes Gigabit Switch

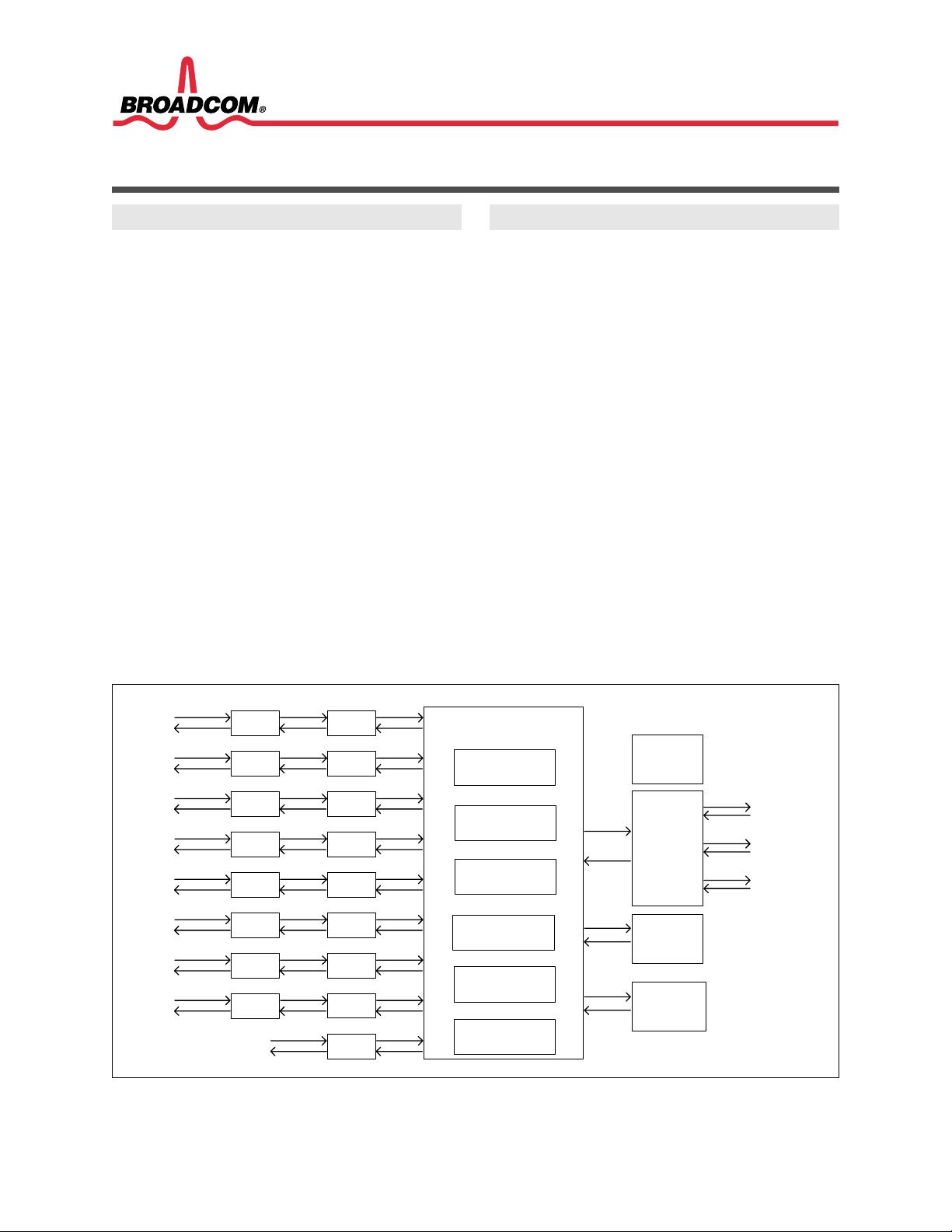

Figure 1: BCM5389 Functional Block Diagram

GENERAL DESCRIPTION FEATURES

The BCM5389 is an 8-port gigabit switch integrated with

eight 1.25 Gbps SerDes/SGMII port interfaces for

connecting to external gigabit PHYs or fiber modules. The

BCM5389 provides the lowest-cost Gigabit Ethernet-to-

the-desktop switching solution or WebSmart™

application.

The BCM5389 is a highly integrated solution, combining

all the functions of a high-speed switch system, including

packet buffer, media access controllers (MACs), address

management, and a non-blocking switch controller into a

single monolithic 0.13 µm CMOS device. The BCM5389

complies with the IEEE IEEE 802.3™, IEEE 802.3u,

IEEE 802.3ab, and IEEE 802.3x specifications, including

the MAC control PAUSE frame and auto-negotiation

subsections, providing compatibility with all industry-

standard Ethernet, fast Ethernet, and Gigabit Ethernet

devices.

The BCM5389 provides integrated 1.25 Gbps SerDes,

reducing board footprint requirements. The eight ports

have SGMII interfaces for connecting with external

Gigabit transceivers.

• 8-port 10/100/1000 Mbps integrated switch controller

via 1.25 Gbps SerDes/SGMII/Fiber

• Embedded 128 KB on-chip packet buffer

• One 1000/100/10 Mbps inband management port

(IMP) with a GMII/RGMII/RvMII interface for PHY-

less connection to a CPU/management entity

• Integrated address management

• Supports up to 4000 unicast addresses

• Supports jumbo frame up to 9728 bytes

• Supports EEPROM for low-cost chip configuration

• Integrated Motorola

®

SPI-compatible interface

• Port-mirroring support

• Port-based VLAN and 4K IEEE 802.1Q tag VLAN

• Port, DiffServ, weighted/strict priority, and IEEE

802.1p-based QoS for four queues

• Spanning tree support

• MAC-based trunking with link failover

• Low-power (1.0W [total], 1.2V [core], and 2.5V

[RGMII], or 3.3V [GMII/MII]) with 3.3V I/O tolerance

• 256-FBGA

Quality of Service

(QoS)

Switch Controller

Port Mirroring

Jumbo Frames

Port Trunking

Rate Control

VLAN

SerDes

Interface

Port 0

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 1

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 2

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 3

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 4

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 5

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 6

Deserializer

Serializer

Gigabit

MAC

SerDes

Interface

Port 7

Deserializer

Serializer

Gigabit

MAC

Gigabit

MAC

GMII,

RvMII, or

RGMII

Management

Register

Space

Address

Management

Memory

Internal

Regulators

Configuration

Pins

SPI Interface or

EEPROM Interface

MDIO/MDC

Interface

2/28/2007 Y4XMF

Broadcom

®

, the pulse logo, Connecting everything

®

, and the Connecting everything logo are among the trademarks of

Broadcom Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks

or trade names mentioned are the property of their respective owners.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed, intended, or

certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control, hazardous

substances management, or other high risk application. BROADCOM PROVIDES THIS DATA SHEET "AS-IS", WITHOUT

WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING,

WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR

PURPOSE, AND NON-INFRINGEMENT.

Broadcom Corporation

P.O. Box 57013

16215 Alton Parkway

Irvine, CA 92619-7013

© 2007 by Broadcom Corporation

All rights reserved

Printed in the U.S.A.

REVISION HISTORY

Revision Date Description

5389-DS06-R 2/28/07 “Programming the VLAN Table” on page 8

Table 13 on page 28

Table 124 on page 135

5389-DS05-R 10/18/06 Updated:

• Low-power voltage value in cover page Features bullet.

5389-DS04-R 10/09/06 Updated:

• ”Transmit Output Port Queues” on page 37

• Table 101, ”MII Status Register (Page 010h-017h: Address 02h-03h),” on page 117

• Table 106, ”SerDes/SGMII Control 1 Register (Page 010h-017h: Address 020h-021h),”

on page 121

• Table 107, ”Analog Transmit Register (Page 010h-017h: Address 020h-021h, Block 1),”

on page 123

• Table 108, ”SerDes/SGMII Control 2 Register (Page 010h-017h: Address 022h-023h),”

on page 123

• Table 167, ”Electrical Characteristics,” on page 165

5389-DS03-R 03/23/06 Updated:

• Table 99, ”Internal Serial Port Registers (Page 010h–017h),” on page 115.

• Table 160, ”External PHY Registers (Serial Ports) (Page 080h–087h),” on page 162

Added:

• ”Master Mode” on page 50.

• ”Slave Mode” on page 51.

• Table 107, ”Analog Transmit Register (Page 010h-017h: Address 020h-021h, Block 1),”

on page 123.

• ”Serial Interface Timing” on page 167.

5389-DS02-R 09/15/05 Updated:

• Table 167, ”Electrical Characteristics,” on page 165.

• Table 172, ”RGMII Output Timing (Normal Mode),” on page 170.

5389-DS01-R 05/27/05 • Minor updates.

• Modified GMII and MDS/MDIO timing.

• Updated internal SerDes registers.

5389-DS00-R 03/09/05 Initial release.

2/28/2007 Y4XMF

Preliminary Data Sheet BCM5389

2/28/07

Broadcom Corporation

Document 5389-DS06-R Page iii

Table of Contents

Section 1: Introduction........................................................................................................1

Overview ....................................................................................................................................................... 1

Audience ....................................................................................................................................................... 1

Data Sheet Information ................................................................................................................................1

Section 2: Features and Operation ....................................................................................2

Overview ....................................................................................................................................................... 2

Quality of Service......................................................................................................................................... 2

Egress Transmit Queues ........................................................................................................................ 3

Port-Based QoS...................................................................................................................................... 3

IEEE 802.1p QoS.................................................................................................................................... 4

MAC-Based QoS .................................................................................................................................... 4

DiffServ QoS ........................................................................................................................................... 4

Frame Priority Decision Tree .................................................................................................................. 5

Port-Based VLAN ......................................................................................................................................... 5

IEEE 802.1Q VLAN ....................................................................................................................................... 5

IEEE 802.1Q VLAN Table Organization ................................................................................................. 6

Programming the VLAN Table ................................................................................................................ 6

Jumbo Frame Support ................................................................................................................................. 7

Port Trunking/Aggregation.......................................................................................................................... 7

Rate Control.................................................................................................................................................. 8

The Two-Bucket System ......................................................................................................................... 9

The Bucket Bit Rate ................................................................................................................................ 9

Protected Ports .......................................................................................................................................... 10

Port Mirroring ............................................................................................................................................. 10

Enabling Port Mirroring ......................................................................................................................... 10

Capture Port.......................................................................................................................................... 11

Mirror Filtering Rules............................................................................................................................. 11

Port Mask Filter.............................................................................................................................. 11

Packet Address Filter..................................................................................................................... 11

Packet Divider Filter....................................................................................................................... 12

IGMP Snooping .......................................................................................................................................... 12

Address Management................................................................................................................................13

2/28/2007 Y4XMF

BCM5389 Preliminary Data Sheet

2/28/07

Broadcom Corporation

Page iv Document 5389-DS06-R

Address Table Organization ..................................................................................................................13

Address Learning ..................................................................................................................................14

Address Resolution and Frame Forwarding..........................................................................................14

Unicast Addresses .........................................................................................................................15

Multicast Addresses .......................................................................................................................16

Reserved Multicast Addresses.......................................................................................................18

Static Address Entries ...........................................................................................................................19

Accessing the ARL Table Entries ..........................................................................................................19

Reading an ARL Entry....................................................................................................................19

Writing an ARL Entry......................................................................................................................19

Searching the ARL Table ...............................................................................................................20

Address Aging .......................................................................................................................................20

Fast Aging .............................................................................................................................................21

Using the Multiport Addresses...............................................................................................................21

Section 3: System Functional Blocks ............................................................................. 22

Overview......................................................................................................................................................22

Media Access Controller............................................................................................................................22

Receive Function...................................................................................................................................22

Transmit Function..................................................................................................................................23

Flow Control ..........................................................................................................................................23

10/100 Mbps Half-Duplex............................................................................................................... 23

10/100/1000 Mbps Full-Duplex ......................................................................................................23

Frame Management Block .........................................................................................................................24

Frame Forwarding .................................................................................................................................24

Broadcom Management Tag .................................................................................................................25

Additional Frame Management Port Configuration ...............................................................................26

MIB Engine ..................................................................................................................................................27

MIB Counters Per Port .......................................................................................................................... 27

Integrated High-Performance Memory .....................................................................................................34

Switch Controller ........................................................................................................................................34

Buffer Management ...............................................................................................................................34

Memory Arbitration ................................................................................................................................35

Transmit Output Port Queues................................................................................................................35

2/28/2007 Y4XMF

Preliminary Data Sheet BCM5389

2/28/07

Broadcom Corporation

Document 5389-DS06-R Page v

Section 4: System Interfaces ............................................................................................36

Overview ..................................................................................................................................................... 36

Serial Interface ........................................................................................................................................... 36

SGMII Mode.......................................................................................................................................... 36

SerDes Mode ........................................................................................................................................ 37

SerDes/SGMII Auto-Negotiation ........................................................................................................... 37

Frame Management Port Interface ........................................................................................................... 37

Reverse MII Port (RvMII) ...................................................................................................................... 37

GMII Port............................................................................................................................................... 38

RGMII Port ............................................................................................................................................ 38

Configuration Pins ..................................................................................................................................... 38

Programming Interfaces............................................................................................................................ 39

SPI Interface ......................................................................................................................................... 39

Normal SPI Mode .......................................................................................................................... 41

Fast SPI Mode ............................................................................................................................... 45

EEPROM Interface ............................................................................................................................... 46

EEPROM Format........................................................................................................................... 47

MDC/MDIO Interface................................................................................................................................... 48

MDC/MDIO Interface Register Programming........................................................................................ 48

Master Mode ......................................................................................................................................... 48

Slave Mode ........................................................................................................................................... 48

Pseudo-PHY .................................................................................................................................. 49

LED Interfaces ............................................................................................................................................ 55

Parallel LED Interface ........................................................................................................................... 55

Serial LED Interface.............................................................................................................................. 57

Section 5: Hardware Signal Definition Table...................................................................61

I/O Signal Types ......................................................................................................................................... 61

Signal Descriptions.................................................................................................................................... 62

Section 6: Pin Assignment................................................................................................67

Pin Assignment by Pin Number................................................................................................................ 67

Pin Assignment by Signal Name .............................................................................................................. 69

Section 7: Register Definitions.........................................................................................71

Register Definition ..................................................................................................................................... 71

剩余187页未读,继续阅读

v111v111

- 粉丝: 4

- 资源: 8

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论9