DDR3控制器设计:Spartan-6 FPGA内存控制器用户指南

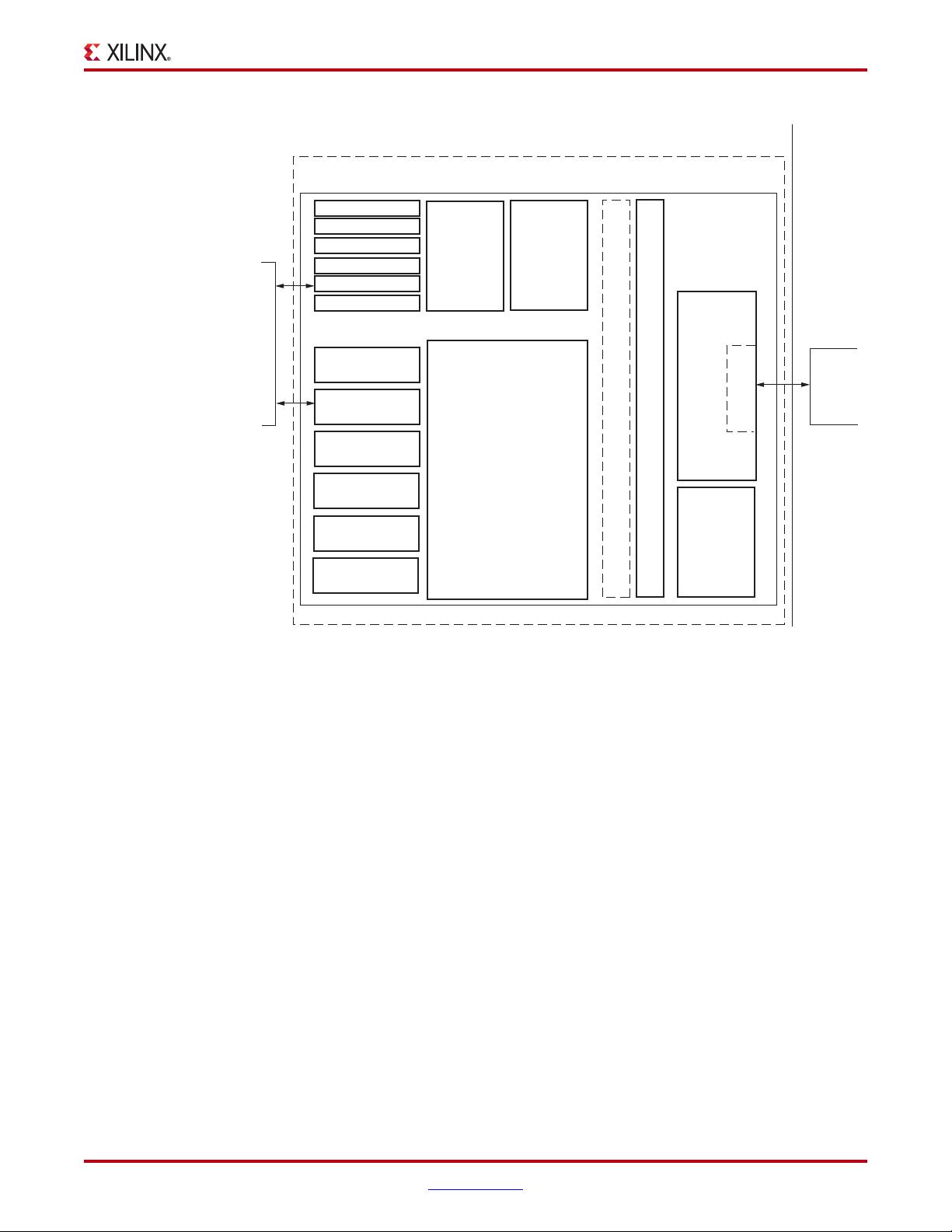

DDR3 (Double Data Rate Three) 控制器是现代计算机系统中的一种关键组件,它负责管理和协调内存模块(如DRAM)的高速数据传输。这些控制器在设计时需要考虑多种因素,以确保内存与处理器之间高效、稳定的通信。Spartan-6 FPGA(Field-Programmable Gate Array)是一种广泛应用的可编程逻辑器件,其内部集成有专门的内存控制器,用于实现DDR3内存的支持。 Xilinx的UG388版本2.3(日期:2010年8月9日)是一份用户指南文档,详细介绍了如何利用Spartan-6 FPGA的内存控制器设计针对DDR3的系统。这份文档的版权仅限于在开发过程中与Xilinx硬件设备配合使用的用途,用户在复制、分发或以任何形式(如电子、机械、影印、录音等)使用文档前,必须获得Xilinx的书面许可。 文档中强调了几个关键点: 1. **知识产权保护**:用户不得在未经Xilinx事先书面同意的情况下,擅自复制、分发或公开文档。这体现了Xilinx对其技术知识产权的尊重和保护。 2. **免责声明**:Xilinx对文档内容的准确性、完整性不作任何保证,也不承担因使用文档产生的任何责任。这意味着用户在依赖文档进行设计时应自行评估风险。 3. **更新性**:Xilinx保留在无通知情况下修改文档的权利,且不对文档中的错误进行纠正或通知用户更新。这意味着用户应持续关注最新的技术支持信息。 4. **产品状态**:文档提供的信息是“按现状”提供,没有附带任何保修或支持服务。用户在使用时可能需要自行解决可能遇到的技术问题。 通过Spartan-6 FPGA的DDR3控制器,开发者可以利用Xilinx的工具和技术构建出具有高性能内存系统的嵌入式或定制化设计。然而,在实际应用中,理解并遵循文档中的指导原则,正确配置和优化控制器参数,以及处理潜在的兼容性和性能问题,是至关重要的。

剩余65页未读,继续阅读

- 粉丝: 2

- 资源: 6

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- VMP技术解析:Handle块优化与壳模板初始化

- C++ Primer 第四版更新:现代编程风格与标准库

- 计算机系统基础实验:缓冲区溢出攻击(Lab3)

- 中国结算网上业务平台:证券登记操作详解与常见问题

- FPGA驱动的五子棋博弈系统:加速与创新娱乐体验

- 多旋翼飞行器定点位置控制器设计实验

- 基于流量预测与潮汐效应的动态载频优化策略

- SQL练习:查询分析与高级操作

- 海底数据中心散热优化:从MATLAB到动态模拟

- 移动应用作业:MyDiaryBook - Google Material Design 日记APP

- Linux提权技术详解:从内核漏洞到Sudo配置错误

- 93分钟快速入门 LaTeX:从入门到实践

- 5G测试新挑战与罗德与施瓦茨解决方案

- EAS系统性能优化与故障诊断指南

- Java并发编程:JUC核心概念解析与应用

- 数据结构实验报告:基于不同存储结构的线性表和树实现

信息提交成功

信息提交成功