Cadence版图设计教程:从基础到实践

"Cadence版图设计讲稿,主要讲解如何使用Cadence进行版图设计,适合初学者,内容包括集成电路的制造与设计流程、CMOS集成电路元件、版图设计规则和设计准则,以及标准单元库版图分析。教程中还涉及课堂测试与作业,旨在帮助学习者掌握Cadence软件的实际操作技能。"

Cadence是一款广泛应用于集成电路设计的专业工具,特别是在版图设计领域。版图设计是集成电路设计的关键环节,它决定了芯片的物理实现和性能表现。在清华大学的这份讲稿中,版图设计被深入浅出地讲解,适合新手入门。

首先,讲稿介绍了集成电路的基本概念,它是由有源元件(如二极管、晶体管)和无源元件(电阻、电容)集成在半导体衬底上形成的完整电路,通过集成电路的引出端实现输入、输出、电源和地的连接。接着,详细阐述了集成电路的制作过程,包括设计、版图绘制、制版、流水加工、掩膜、硅圆片处理、划片、封装等步骤,这些步骤对于理解版图设计的重要性至关重要。

在设计流程方面,讲稿涵盖了电路输入、电路仿真、逻辑综合、布局布线、版图编辑、设计规则检查(DRC)、光刻对准检查(LVS)、寄生参数提取、以及最终的GDSII数据输出。这一系列流程确保了设计的正确性和可制造性。

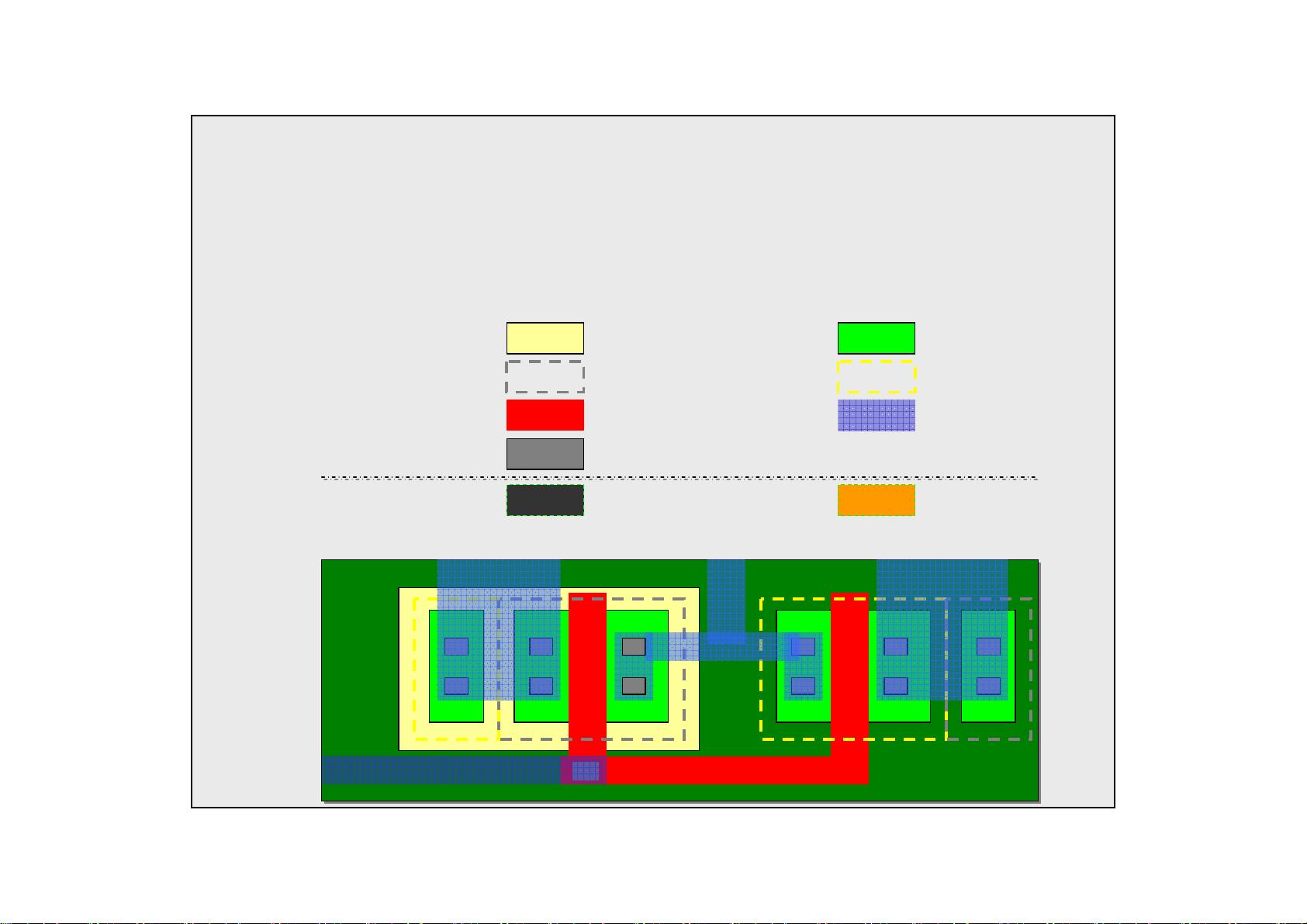

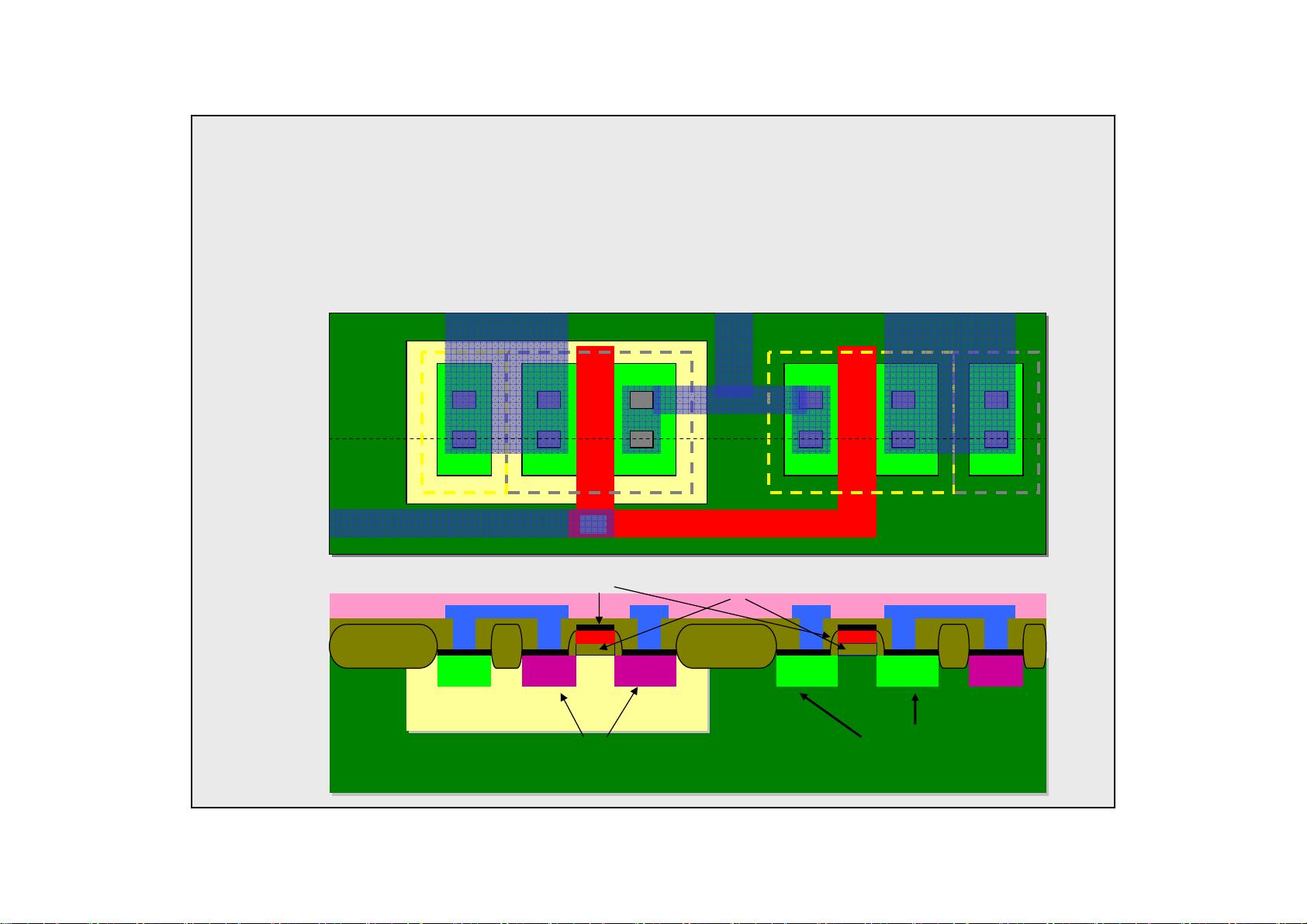

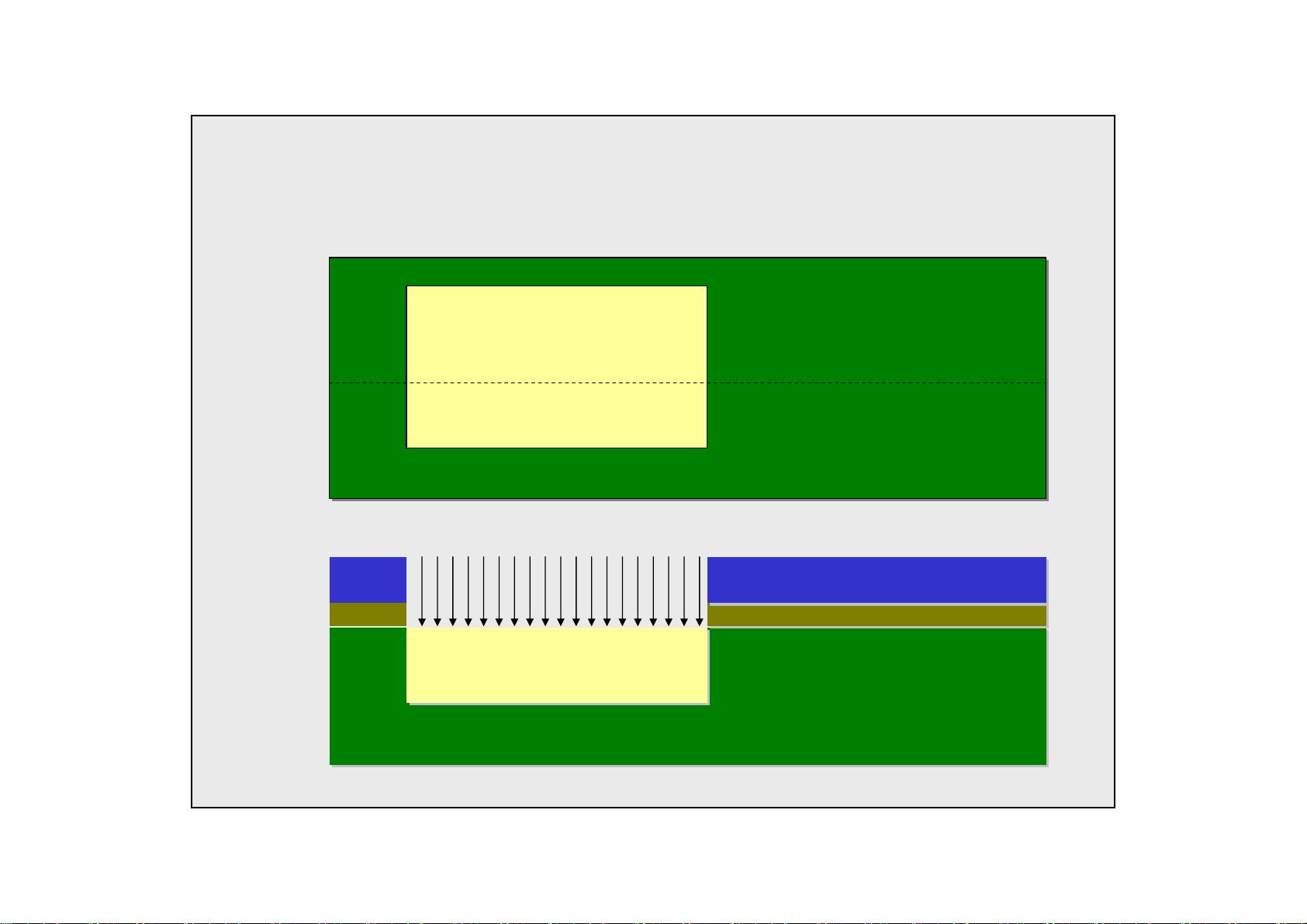

在CMOS集成电路中,版图设计规则(Topological Design Rule)和设计准则('Rule' for performance)是非常关键的。这些规则规定了元件之间的最小间距、接触尺寸、线宽限制等,以防止短路、串扰等问题,同时确保电路性能。标准单元库版图分析则让学习者了解如何分析和利用预定义的电路模块,以快速高效地构建复杂电路。

课堂测试与作业部分则是为了让学习者通过实践巩固理论知识,提升实际操作能力。Cadence的标准单元库版图分析以1.2um CMOS工艺为例,帮助学习者理解不同工艺节点下的版图设计特点。

这份讲稿为Cadence版图设计提供了全面的基础知识,通过学习,初学者可以系统地掌握版图设计的基本技能,为后续的集成电路设计打下坚实基础。

2009-04-21 上传

2009-08-31 上传

2014-05-18 上传

2011-09-08 上传

2021-10-07 上传

2011-03-12 上传

2010-02-03 上传

lierbencyhqq

- 粉丝: 2

- 资源: 6