Verilog HDL逻辑综合入门指南

需积分: 9 62 浏览量

更新于2024-07-31

收藏 2.3MB PDF 举报

《逻辑合成入门:使用Verilog HDL》是一本由Robert B. Reese和Mitchell A. Thornton合著的专业参考书籍,版权归Morgan & Claypool所有。该书针对逻辑合成领域的新手和专业人士,详细介绍了如何利用Verilog Hardware Description Language (HDL)进行电路设计和逻辑实现。Verilog是电子设计自动化(EDA)中常用的高级硬件描述语言,它提供了强大的抽象和模块化能力,使得设计者能够描述数字电路的行为和结构。

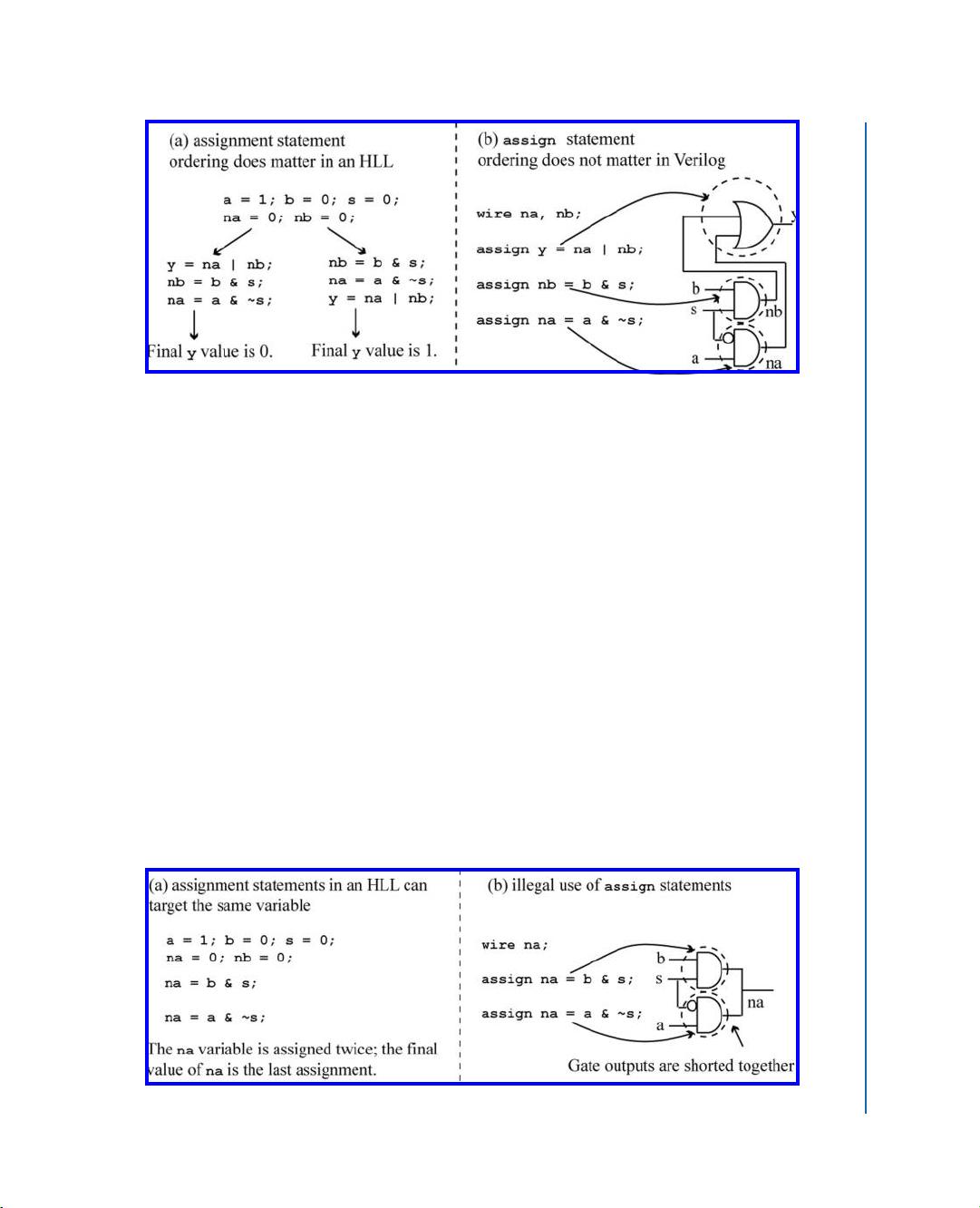

本书的主要内容涵盖了逻辑合成的基本概念、Verilog语法规则、设计流程、以及如何使用Verilog进行门级、行为级和系统级的设计。作者在书中强调了Verilog的结构化编程方法,包括组合逻辑、时序逻辑、模块化设计和接口描述。读者可以从中学习到如何编写有效的Verilog代码,包括数据类型、赋值语句、条件语句、循环、并行和同步结构等。

章节可能包括:

1. **Verilog概述**:介绍Verilog语言的历史、特点和与传统电路设计语言的区别,以及其在现代电子设计中的重要性。

2. **Verilog基本语法**:讲解Verilog的关键组成部分,如声明、定义、程序块和信号声明,让读者熟悉语言的构造。

3. **逻辑设计基础**:涉及基本逻辑门、触发器、组合逻辑和时序逻辑的实现,以及布尔代数和逻辑优化的基础知识。

4. **模块设计**:教授如何创建独立的、可重用的模块,包括模块参数、端口、包和接口,以及模块间的连接。

5. **设计流程与工具**:讨论逻辑综合的过程,包括逻辑描述、仿真、验证和优化,以及使用Verilog工具(如Quartus II, ISE, or Vivado)的技巧。

6. **高级设计技术**:探讨复杂逻辑结构的实现,如状态机、时序分析、以及高级功能单元的设计如寄存器、计数器和移位寄存器。

7. **案例研究与实践项目**:通过实际案例演示如何将理论知识应用到实际设计中,帮助读者加深理解并提升设计能力。

《逻辑合成入门:使用Verilog HDL》作为SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS系列的一部分,旨在提供一个全面而深入的学习平台,适合电子工程专业学生、工程师和研究人员作为教材,或者作为自学的参考资料。无论你是希望进入硬件设计行业,还是想提高现有设计技能,这本书都能提供关键的指导和支持。

2010-01-10 上传

2019-02-17 上传

2012-11-06 上传

2024-04-04 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

humbleRF

- 粉丝: 12

- 资源: 2

最新资源

- not-so-simple

- hostFolder

- hackernews-clone:Hackernews使用React,GraphQL,Prisma和Postgres进行克隆

- fastapi-celery-example

- 虚幻4自由视角镜头 Camera.7z

- usersList

- Social-iNet:具有boostrap 4和javascript的简单SPA

- Java垃圾收集必备手册.rar

- CareerPath:个人研究的此回购角色有关开发职业或其他任何问题的提示

- TotalControl:一款带手控的安卓游戏

- JavaAssessments

- Proyecto-Hotel:Proyecto#1(酒店)

- collection_exercises

- 【WordPress插件】2022年最新版完整功能demo+插件14 Mar.zip

- sequelize-search-builder:极简库,用于解析搜索请求以序列化查询

- Actions:作证行动