绕过D盾IIS防火墙:SQL注入攻防策略与技巧

需积分: 0 187 浏览量

更新于2024-08-05

收藏 521KB PDF 举报

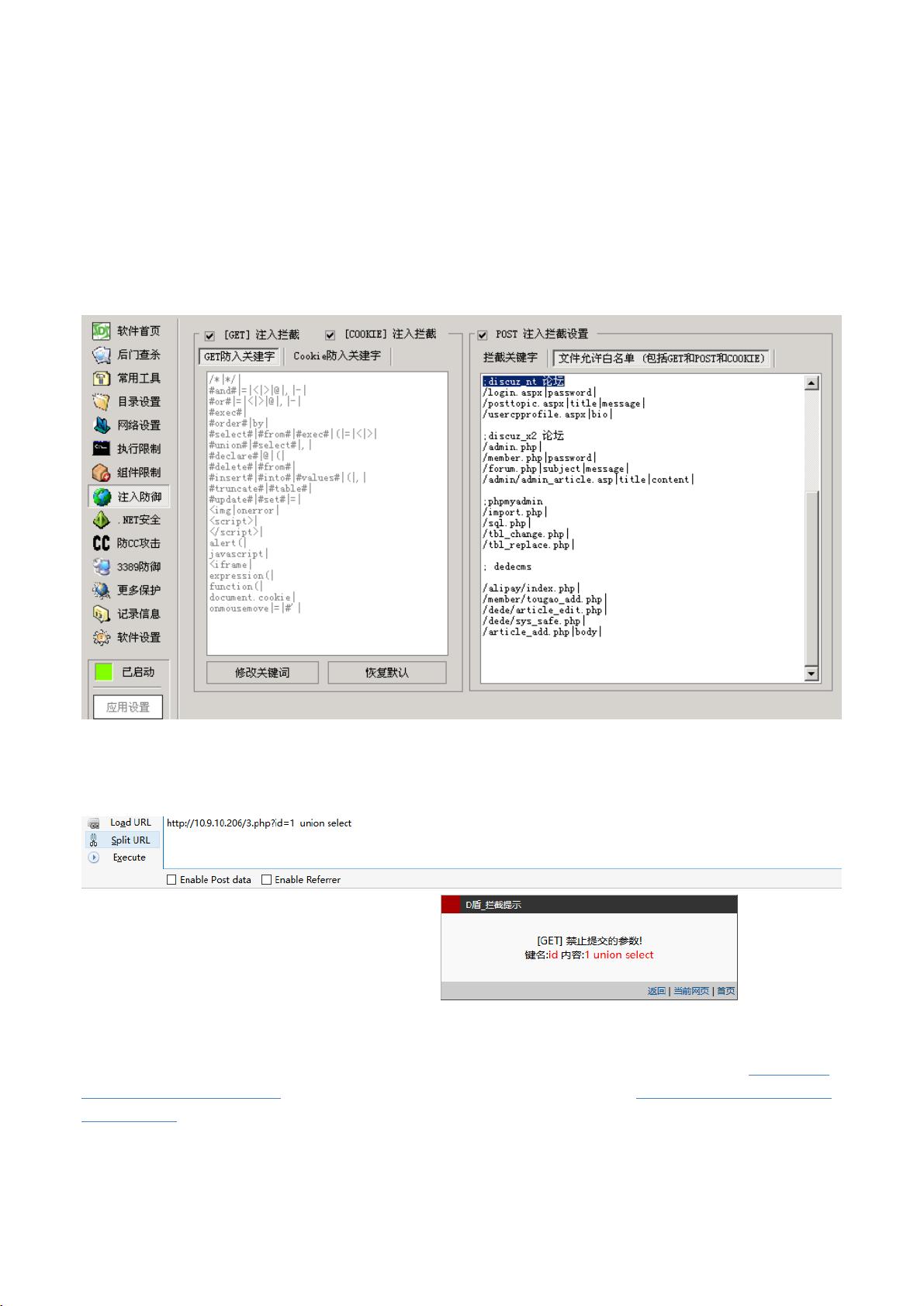

本文档主要探讨了如何绕过D盾IIS防火墙在Windows 2003服务器上的SQL注入防御策略。D盾IIS防火墙针对GET、POST、COOKIE等请求类型进行限制,并采用了白名单机制,仅允许预设的特定URL访问。作者通过搭建IIS与PHP、MySQL的环境,展示了三种主要的SQL注入绕过方法:

1. 白名单漏洞利用:在PHP环境中,利用`PATH_INFO`特性,通过在请求路径后附加未被白名单包含的地址,如`/3.php/admin.php?id=1unionselect1,2,schema_namefrominformation_schema.SCHEMATA`,成功绕过了防火墙。

2. 空白字符利用:在MySQL中,空格字符 `%a0` 被发现能够与`SELECT`语句结合,使得防火墙无法识别,从而实现注入。示例为`id=1union%a0select1,2,3fromadmin`。

3. 特殊字符\N:通过在SQL语句开头插入`\N`,作者发现这种特殊转义序列可以避开`UNION SELECT`和`SELECT FROM`检测。例如,`id=\Nunion(select1,schema_name,\Nfrom information_schema.schemata)`。

在IIS与ASP/ASPX和MSSQL的组合中,尽管D盾IIS防火墙具有一定的防护能力,但这些绕过技巧表明攻击者可以通过深入理解系统细节找到漏洞。随着D盾新版的即将发布,预计会有更多的防御措施,但同时,这也提醒开发者和安全专家持续关注并改进Web应用程序的安全性,以应对不断演变的威胁。测试和防御策略的更新对于保障网络环境的安全至关重要。

2022-08-03 上传

2022-08-03 上传

2023-06-01 上传

2023-06-02 上传

2023-06-03 上传

2023-09-17 上传

2023-06-07 上传

2023-07-27 上传

2023-06-01 上传

西西里的小裁缝

- 粉丝: 32

- 资源: 292

最新资源

- C++ Qt影院票务系统源码发布,代码稳定,高分毕业设计首选

- 纯CSS3实现逼真火焰手提灯动画效果

- Java编程基础课后练习答案解析

- typescript-atomizer: Atom 插件实现 TypeScript 语言与工具支持

- 51单片机项目源码分享:课程设计与毕设实践

- Qt画图程序实战:多文档与单文档示例解析

- 全屏H5圆圈缩放矩阵动画背景特效实现

- C#实现的手机触摸板服务端应用

- 数据结构与算法学习资源压缩包介绍

- stream-notifier: 简化Node.js流错误与成功通知方案

- 网页表格选择导出Excel的jQuery实例教程

- Prj19购物车系统项目压缩包解析

- 数据结构与算法学习实践指南

- Qt5实现A*寻路算法:结合C++和GUI

- terser-brunch:现代JavaScript文件压缩工具

- 掌握Power BI导出明细数据的操作指南