TimeQuest时序分析模型与应用指南

需积分: 9 71 浏览量

更新于2024-07-22

收藏 4.7MB PDF 举报

TimeQuest 时序分析模型

TimeQuest 是 Altera 公司开发的一款时序分析工具,主要用于 FPGA 设计中的时序分析。以下是对该工具的详细介绍和知识点总结:

**第一章:TimeQuest 静态时序分析模型**

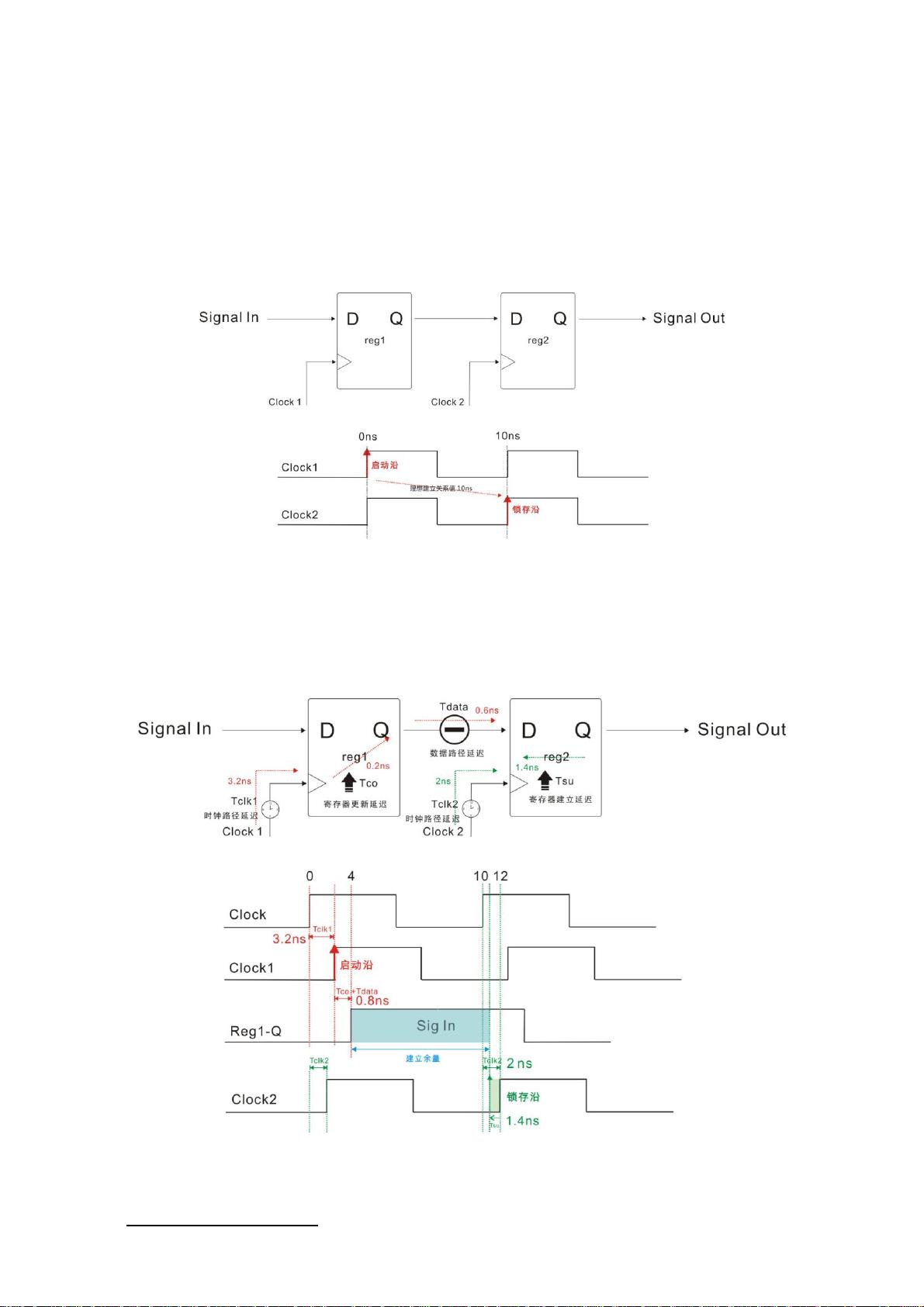

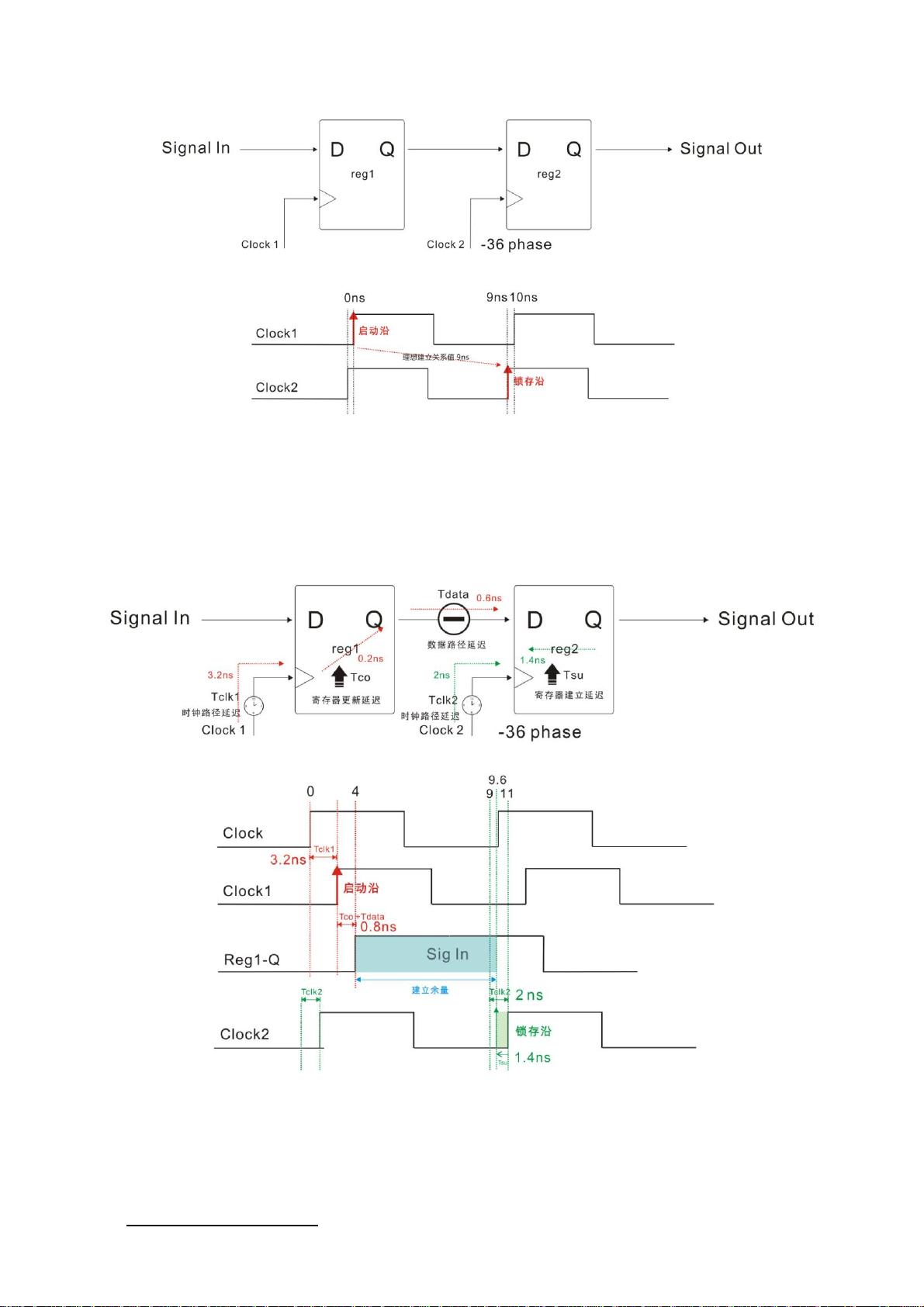

* 模型的基础单位:TimeQuest 模型的基础单位是时序分析模型,包括理想时序和物理时序两部分。

* 理想时序和物理时序的区别:理想时序是指在设计阶段的时序分析,而物理时序是指在实际实现阶段的时序分析。

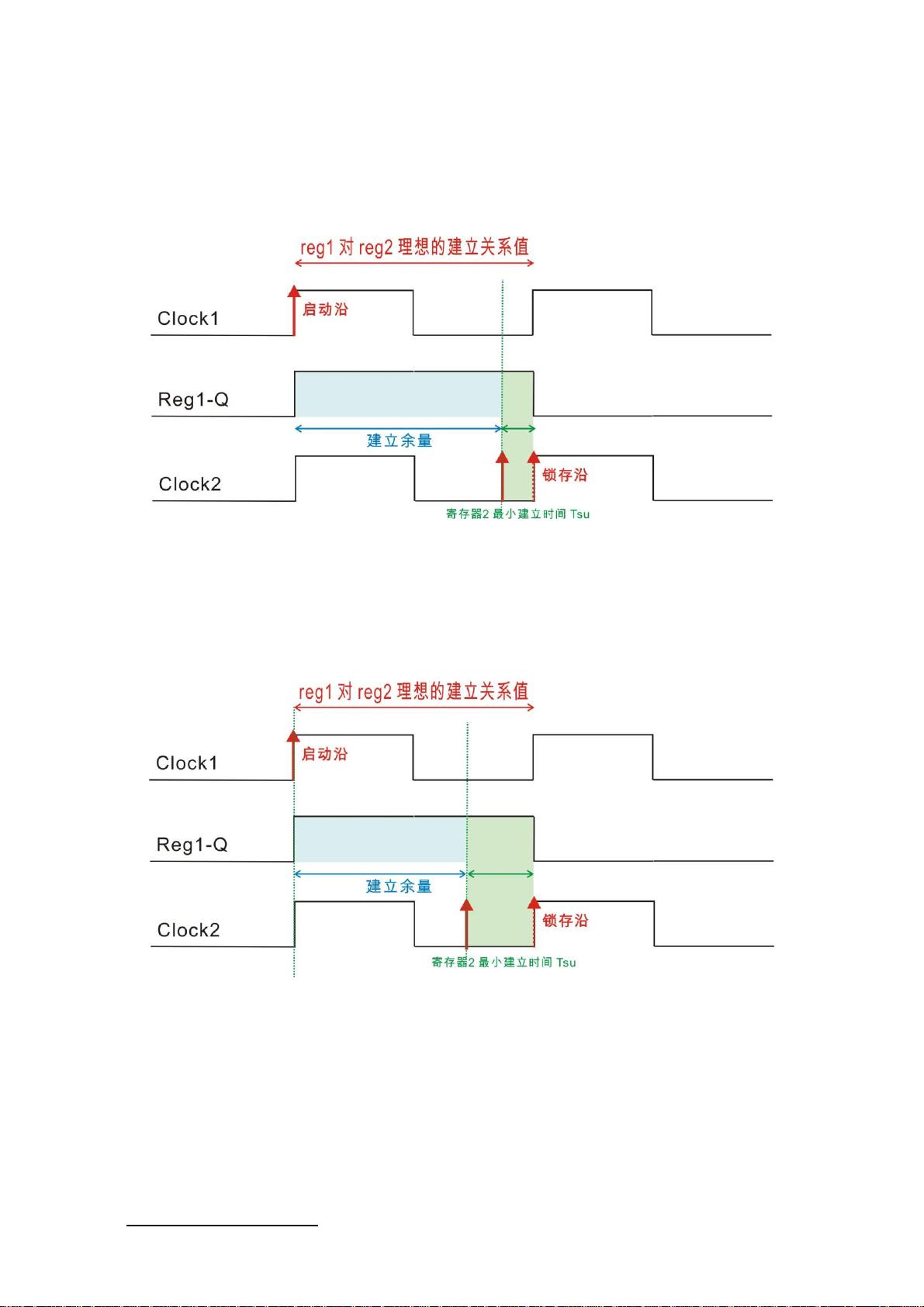

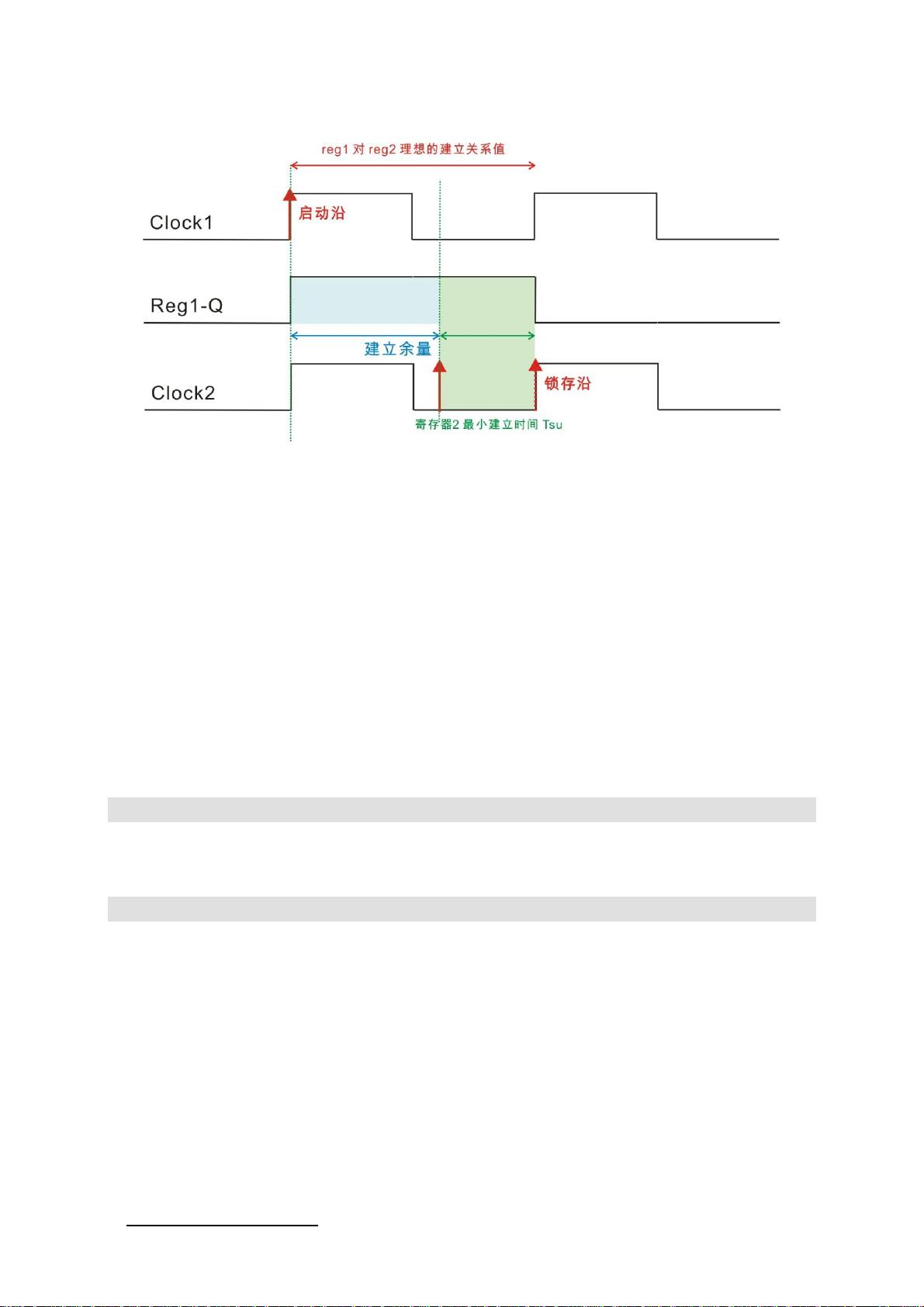

* 建立关系值和保持关系值:TimeQuest 模型中,建立关系值是指时序分析的基础单位,而保持关系值是指时序分析的结果。

* 物理中的建立关系过程和建立余量:TimeQuest 模型中,物理中的建立关系过程是指时序分析的过程,而建立余量是指时序分析的结果。

* 令人误会的建立关系和建立余量:TimeQuest 模型中,建立关系和建立余量是两个不同的概念,但是它们之间存在着紧密的联系。

**第二章:模型角色,网表概念,时序报告**

* TimeQuest 模型的努力:TimeQuest 模型的努力是指时序分析的过程。

* SDC 的网表(NetLists)基本单位:SDC 是指 Synopsys Design Constraints 的缩写,网表是指时序分析的结果。

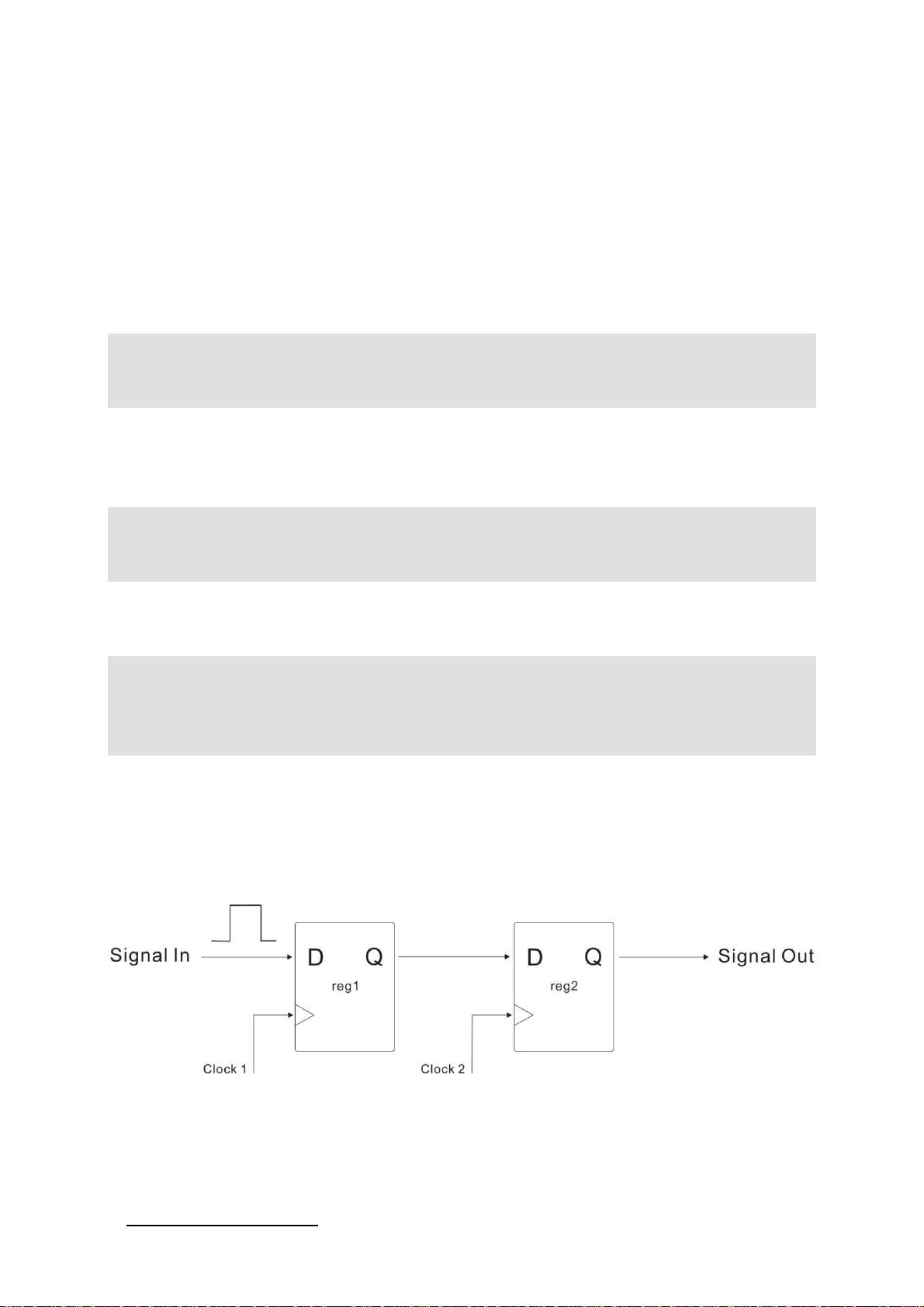

* TimeQuest 模型的简单实例:TimeQuest 模型的简单实例是指时序分析的示例。

* 实验一:入门实验:实验一是指时序分析的入门实验。

* 进一步看看 TimeQuest 模型如何分析时序:TimeQuest 模型可以对时序进行分析。

* 建立 sdc 文件与网表:TimeQuest 模型可以建立 sdc 文件和网表。

* 约束时钟:TimeQuest 模型可以对时钟进行约束。

* 时序报告:TimeQuest 模型可以生成时序报告。

**第三章:TimeQuest 扫盲文**

* 余量的概念:余量是指时序分析的结果。

* 延迟因数:内部延迟因数和外部延迟因数是指时序分析的两个方面。

* 第一层与第二层时间要求:TimeQuest 模型可以对时序进行分析。

* 山寨 TimeQuest 模型:山寨 TimeQuest 模型是指对 TimeQuest 模型的改进和扩展。

* 约束命令和约束行为:TimeQuest 模型可以对时序进行约束。

TimeQuest 是一款功能强大且灵活的时序分析工具,能够对 FPGA 设计中的时序进行分析和优化。通过本章节的学习,读者可以对 TimeQuest 模型有一个深入的了解,并且能够应用于实际的 FPGA 设计中。

144 浏览量

2010-11-01 上传

2018-06-18 上传

2015-06-03 上传

2014-04-14 上传

2009-07-09 上传

2023-06-25 上传

2015-06-25 上传

点击了解资源详情