Quartus II TimeQuest时序分析教程

需积分: 10 56 浏览量

更新于2024-09-14

1

收藏 666KB DOC 举报

"这篇文档是关于时序分析的快速入门指南,主要针对使用Quartus II TimeQuest Timing Analyzer工具进行时序分析的流程和方法进行了详细介绍。内容包括如何设定时序约束、执行时序分析以及如何处理时序违例。此外,还提供了一个基于Altera公司的timequest快速入门教程示例,以FIR滤波器工程为背景,演示了实际操作过程。"

在集成电路设计中,时序分析是确保数字系统正确运行的关键步骤。时序分析主要是评估电路中的信号传输延迟,确保所有信号能够在正确的时间到达目的地,避免时序违例。Quartus II TimeQuest Timing Analyzer是Altera(现Intel FPGA)开发的一款强大的静态时序分析工具,它可以分析整个设计的时序性能,无需实际硬件支持。

1. **TimeQuest工具的使用**

TimeQuest Timing Analyzer允许用户通过Synopsys Design Constraints (SDC)文件定义时序要求,如时钟路径、时序例外和信号传输时间。在编译过程中,Fitter会根据这些约束优化逻辑布局,以满足指定的时序目标。在时序分析阶段,工具会检查每个时序路径的延迟,报告任何时序违例,并提供详细信息以便于问题定位和修复。

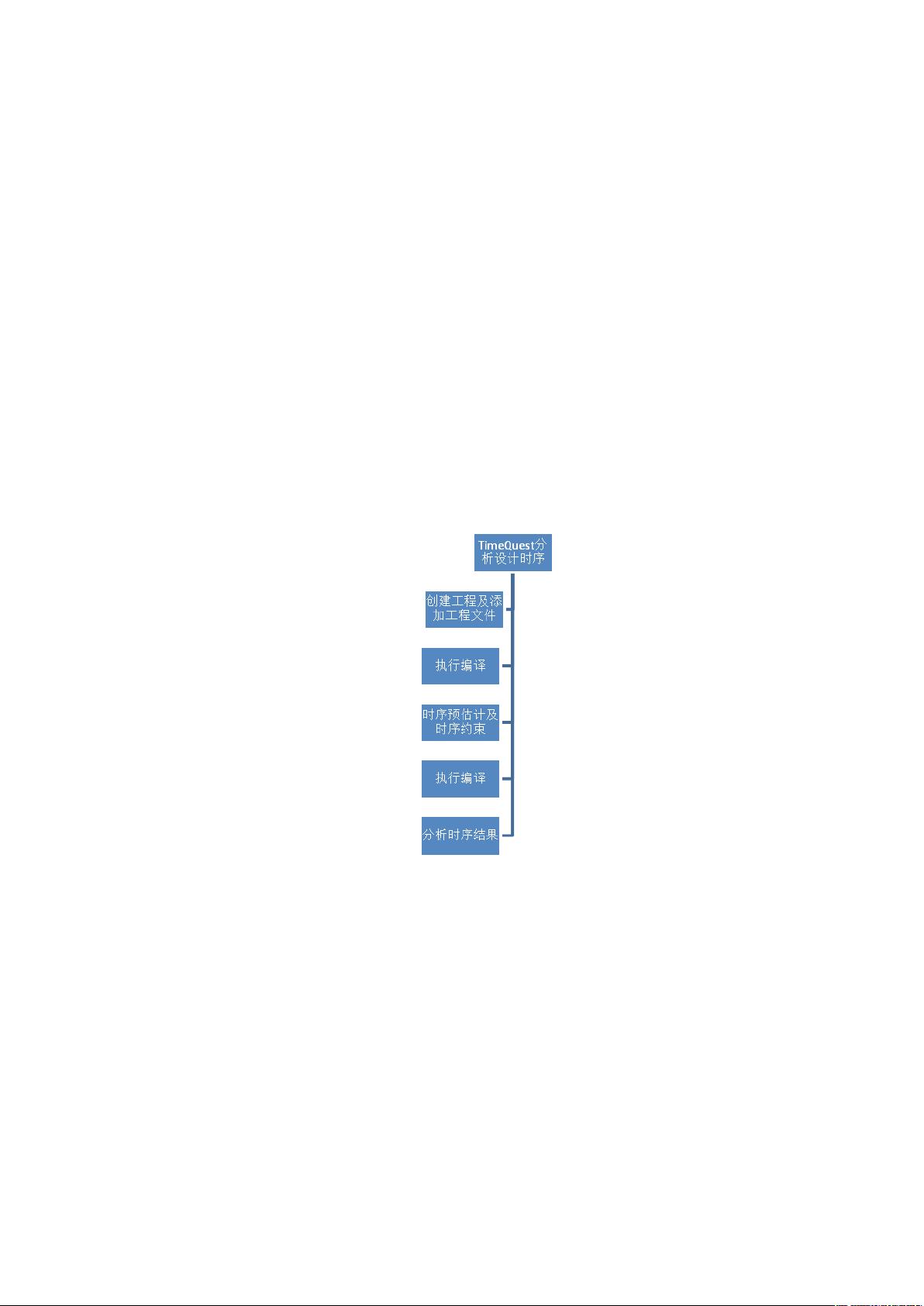

2. **时序分析步骤**

- **第一步**:无约束编译,获取基础时序信息,这有助于了解设计的自然延迟,为设置约束提供参考。

- **第二步**:添加包含时序约束的SDC文件并重新编译。这使得工具能按预设要求进行映射,从而分析设计是否满足时序目标。

3. **timequest快速入门示例**

在Altera的quartusII9.1版本中,通过打开FIR_filter工程进行实践。这个工程包含一个FIR滤波器模块,有输入clk、clkx2、reset、newt和d[7:0],以及输出follow和y。通过这个例子,学习者可以了解到如何在具体的设计中应用TimeQuest工具进行时序分析。

时序分析对于FPGA和ASIC设计至关重要,因为它直接影响着设计的性能和可靠性。理解并熟练掌握TimeQuest Timing Analyzer的使用,能够帮助工程师有效地优化设计,确保设计满足速度和时序要求,从而提高系统的整体性能。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-03-15 上传

2013-10-31 上传

2008-12-26 上传

zcl_33

- 粉丝: 16

- 资源: 61

最新资源

- MATLAB实现小波阈值去噪:Visushrink硬软算法对比

- 易语言实现画板图像缩放功能教程

- 大模型推荐系统: 优化算法与模型压缩技术

- Stancy: 静态文件驱动的简单RESTful API与前端框架集成

- 掌握Java全文搜索:深入Apache Lucene开源系统

- 19计应19田超的Python7-1试题整理

- 易语言实现多线程网络时间同步源码解析

- 人工智能大模型学习与实践指南

- 掌握Markdown:从基础到高级技巧解析

- JS-PizzaStore: JS应用程序模拟披萨递送服务

- CAMV开源XML编辑器:编辑、验证、设计及架构工具集

- 医学免疫学情景化自动生成考题系统

- 易语言实现多语言界面编程教程

- MATLAB实现16种回归算法在数据挖掘中的应用

- ***内容构建指南:深入HTML与LaTeX

- Python实现维基百科“历史上的今天”数据抓取教程