SystemVerilog实现分秒数字钟:时序逻辑与计数器应用

需积分: 0 84 浏览量

更新于2024-08-05

收藏 781KB PDF 举报

"实验三——分秒数字钟的设计与实现1"

在本次实验“实验三——分秒数字钟的设计与实现1”中,主要目标是学习和应用基于SystemVerilog HDL的时序逻辑电路建模技术,以及通过计数器和移位寄存器来实现特定的功能。实验涉及的操作系统包括Windows 10和Ubuntu 16.04,开发环境为Xilinx Vivado 2018.2,硬件平台为Nexys4 DDR FPGA开发板。

实验的第一个关键知识点是基于SystemVerilog HDL的时序逻辑电路建模。SystemVerilog是一种高级的硬件描述语言,它不仅支持行为描述,还支持结构描述,能够方便地构建复杂的数字系统。时序逻辑电路是具有记忆特性的电路,状态的变化不仅取决于当前的输入,还依赖于之前的状态。在SystemVerilog中,可以使用always @(posedge clk)等语句来描述时序逻辑。

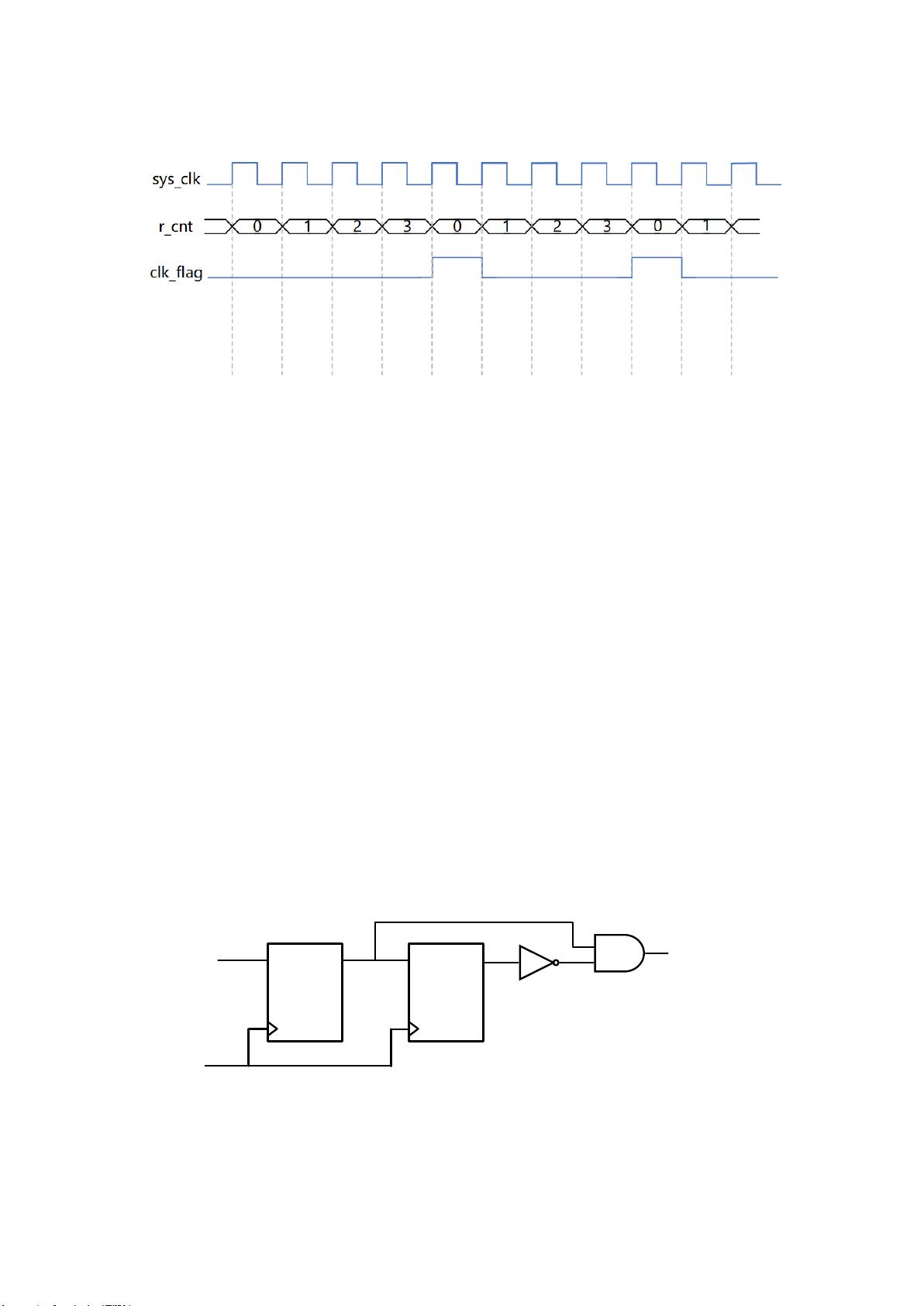

第二个知识点是计数器设计和时钟分频。计数器是数字系统中的基本元件,用于计数或产生周期性脉冲。时钟分频是数字系统设计中常见的操作,目的是将较高频率的时钟信号转换为较低频率的信号。例如,通过计数器,可以将100MHz的时钟信号分频为25MHz。N分频器的工作原理是计数器在每个时钟周期内增加,每计数到N时,输出时钟翻转一次,形成低频时钟。在实验中,如果输入时钟为25MHz,要得到2.5MHz的输出,计数值N应设为10。

第三个知识点是移位寄存器的设计和应用。移位寄存器可以将数据在多个存储位置之间移动,常用于串行到并行或并行到串行的数据转换,以及边沿检测电路。边沿检测电路可以检测信号的上升沿或下降沿,这对于触发某些事件或同步系统至关重要。

实验还介绍了使能时钟的概念,这是解决高频率分频时钟问题的一种策略。传统的分频时钟可能会导致“时钟漫天飞”的问题,不符合同步设计原则。使能时钟是一种解决办法,它会在固定时间间隔产生一个短暂的高电平信号,而不是连续的时钟脉冲。这样,即使有多个不同的分频时钟,系统也能保持同步,提高时序分析的准确性,增强系统性能和稳定性。

这个实验旨在通过实践让学生掌握数字系统设计的基本元素,包括SystemVerilog的使用、计数器和移位寄存器的设计,以及如何利用这些基础元件实现时钟分频和使能时钟功能,这对于FPGA开发和毕业设计是至关重要的技能。

2022-08-08 上传

2021-08-30 上传

2021-09-28 上传

2011-12-18 上传

2022-09-17 上传

2022-05-14 上传

2009-06-08 上传

2019-11-07 上传

点击了解资源详情

网络小精灵

- 粉丝: 36

- 资源: 334

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目