同步时序电路设计:从状态表到逻辑实现

版权申诉

48 浏览量

更新于2024-07-03

收藏 1.16MB PPT 举报

"该资源是关于数字电路与逻辑设计的课件,重点讲解了同步时序电路的设计,包括状态表的建立和通过触发器及 MSI 时序模块来实现同步时序电路的方法。课程涵盖了数制与编码、逻辑函数化简、组合逻辑电路、时序电路分析、同步时序电路设计、数/模和模/数转换器以及可编程逻辑器件的应用等多个知识单元。"

在数字系统设计中,同步时序电路扮演着至关重要的角色,它们作为控制单元负责系统的运行顺序。同步时序电路的设计通常分为几个关键步骤。首先,我们需要理解设计要求,确定输入和输出变量,这些变量将决定电路的行为。接着,选择状态,这些状态用来记录电路输入的历史,帮助电路记住之前的操作。

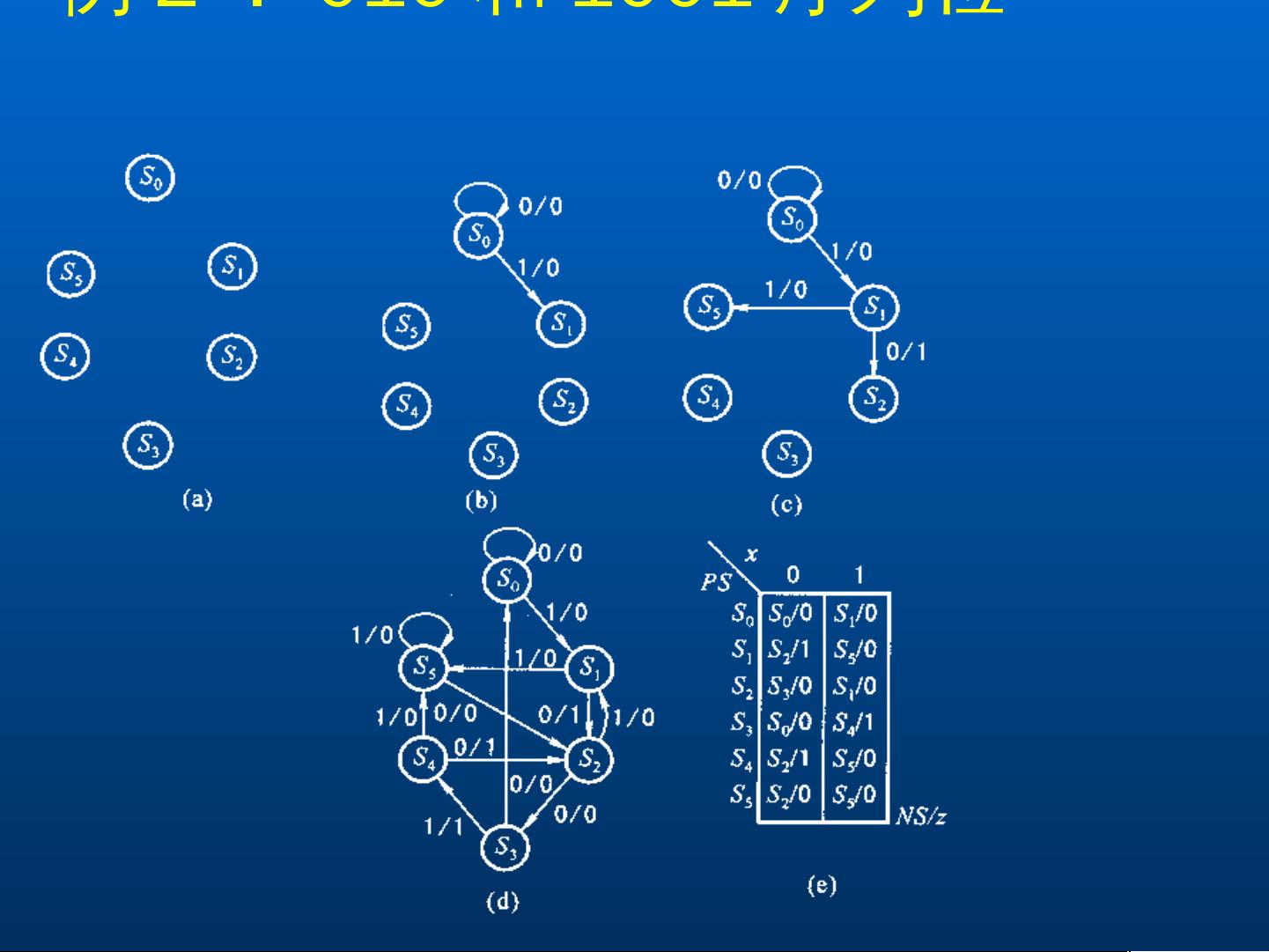

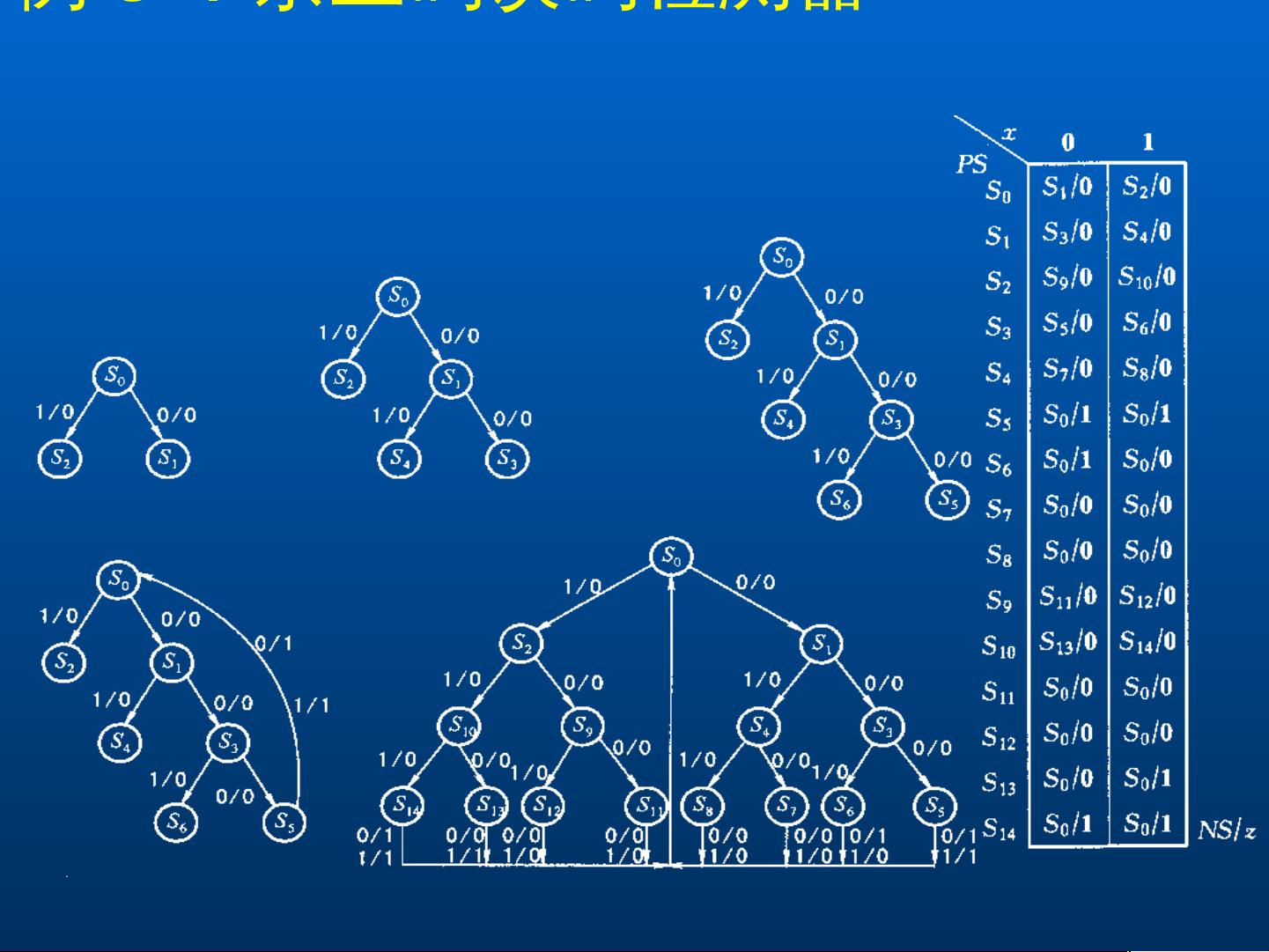

建立原始状态表是设计同步时序电路的基础。这个阶段可能会包含一些冗余状态,需要进一步优化。状态表的构建是通过对每个状态在所有可能的输入组合下转移到下一个状态的分析来完成的。例如,设计一个111序列检测器,状态会根据接收到的1的数量来变化;010和1001序列检测器则需要跟踪更复杂的输入模式;余三码误码检测器用于检测传输错误,而串行加法器则根据进位情况更新状态。

同步时序电路的设计方法通常包括将文字功能描述转化为状态表或状态图,然后推导出逻辑方程,最终形成逻辑图。对于简单的电路,我们可以直接从状态图或状态表开始设计,例如在加1/加2同步计数器的例子中,电路会根据X信号的不同值进行加1或加2的计数,并在达到特定状态后重置。

在实际设计过程中,有时会利用现成的 MSI (Medium Scale Integration) 时序模块来简化设计,例如使用触发器来实现状态存储,或者用其他预封装的时序逻辑组件来构建更复杂的电路。

同步时序电路设计是一个结合理论知识和实践经验的过程,涉及状态的定义、状态转移逻辑的确定以及逻辑实现的选择。通过学习这部分内容,学生可以掌握设计数字系统核心部分的能力,为构建更复杂的数字系统打下坚实基础。

2022-06-17 上传

2022-06-17 上传

2021-09-21 上传

2022-06-17 上传

点击了解资源详情

2009-02-22 上传

点击了解资源详情

2024-12-27 上传

智慧安全方案

- 粉丝: 3837

- 资源: 59万+

最新资源

- small-calculator.zip_Windows编程_Visual_C++_

- book-js

- machine-learning:Java机器学习算法库

- 街机游戏项目

- CodePlayer:使用Html,Css和jQuery制作的项目。 CodePlayer是一种工具,可让您实时使用网络技术进行学习,实验和教学

- 人工智能深度学习flask服务框架.zip

- flume-http-handler:该项目适用于flume http源处理程序

- matlab人脸检测框脸代码-face-detected-opencv-nodejs:与libopencv4nodejs

- flutter-curves

- chap7.zip_VHDL/FPGA/Verilog_VHDL_

- news-extractor

- Export for Trello-crx插件

- cody:Weavora代码约定

- 项目:Primeiros passo com o projeto

- 人工智能大作业-Fashion数据集 分类.zip

- laravel_testoviy_zadaniye