VHDL实现分频器设计详解

"本文主要介绍了如何使用VHDL设计各种类型的分频器,包括偶数分频器、奇数分频器、半整数分频器、小数分频器、分数分频器和积分分频器。这些设计可以在FPGA/CPLD上实现,并通过SynplifyPro或相应FPGA厂商的综合器综合,再在ModelSim上进行验证。文章还提及了计数器在分频器设计中的基础作用,包括普通计数器和约翰逊计数器的VHDL实现。"

分频器是数字系统中不可或缺的组成部分,用于降低输入时钟频率。在FPGA设计中,分频器的实现方式通常包括使用内置的锁相环(PLL)或延迟锁定环(DLL),或者利用硬件描述语言如VHDL、VerilogHDL自定义设计。虽然锁相环电路具备多种功能,但因其数量有限,自定义分频器更常被采用,因为它们更加灵活且资源利用率高。

计数器是构建分频器的基础。文章提到了两种常见的计数器类型:

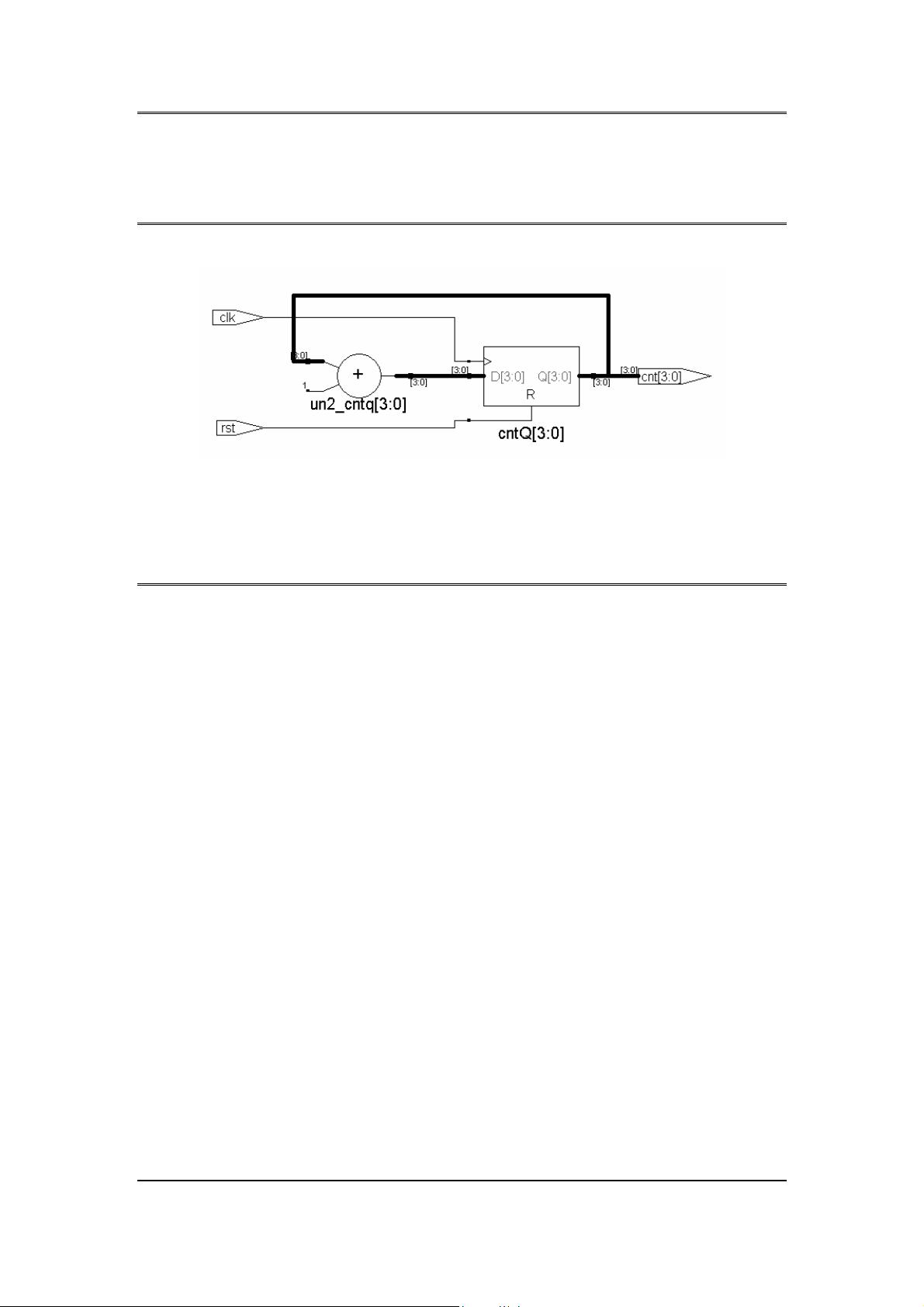

1. 普通计数器,也称为加法计数器,可以通过VHDL实现,如示例代码所示,它接受时钟输入(clk)、复位信号(rst)并输出计数结果(cnt)。计数器的宽度可以通过通用参数(width)进行配置。

```vhdl

entity ripple is

generic(width: integer := 4);

port(clk, rst: in std_logic;

cnt: out std_logic_vector(width - 1 downto 0));

end ripple;

```

2. 约翰逊计数器,又称为环形计数器,其计数方式与普通计数器不同,具有循环特点,适用于特定的分频需求。

在分频器的设计中,具体类型的选择取决于应用需求:

- **偶数分频器**简单地在每个周期的固定次数后产生一个输出脉冲。

- **奇数分频器**则在不均匀的周期内产生输出,例如,对于奇数分频,输出脉冲在最后一个时钟周期产生。

- **半整数分频器**(N+0.5分频)会生成占空比为50%的输出,即使分频比不是整数。

- **小数分频器**涉及到连续多个周期的累加,以达到精确的小数比例分频。

- **分数分频器**通过结合整数和小数部分的分频实现更复杂的频率变换。

- **积分分频器**通常用于动态调整分频比,以适应变化的系统需求。

所有这些设计都可以通过综合工具转化为硬件电路,并在仿真环境中如ModelSim进行验证,确保设计的正确性。

VHDL的优势在于它允许逻辑描述的抽象,使得复杂的设计变得更加清晰和易于管理。对于FPGA/CPLD开发者来说,掌握VHDL进行分频器设计的知识至关重要,因为这不仅可以实现定制化的频率控制,而且可以有效地利用硬件资源。

2012-01-09 上传

2010-03-31 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情