Pre-

divider

MULT

Post-

divider

OSCin Phase detector

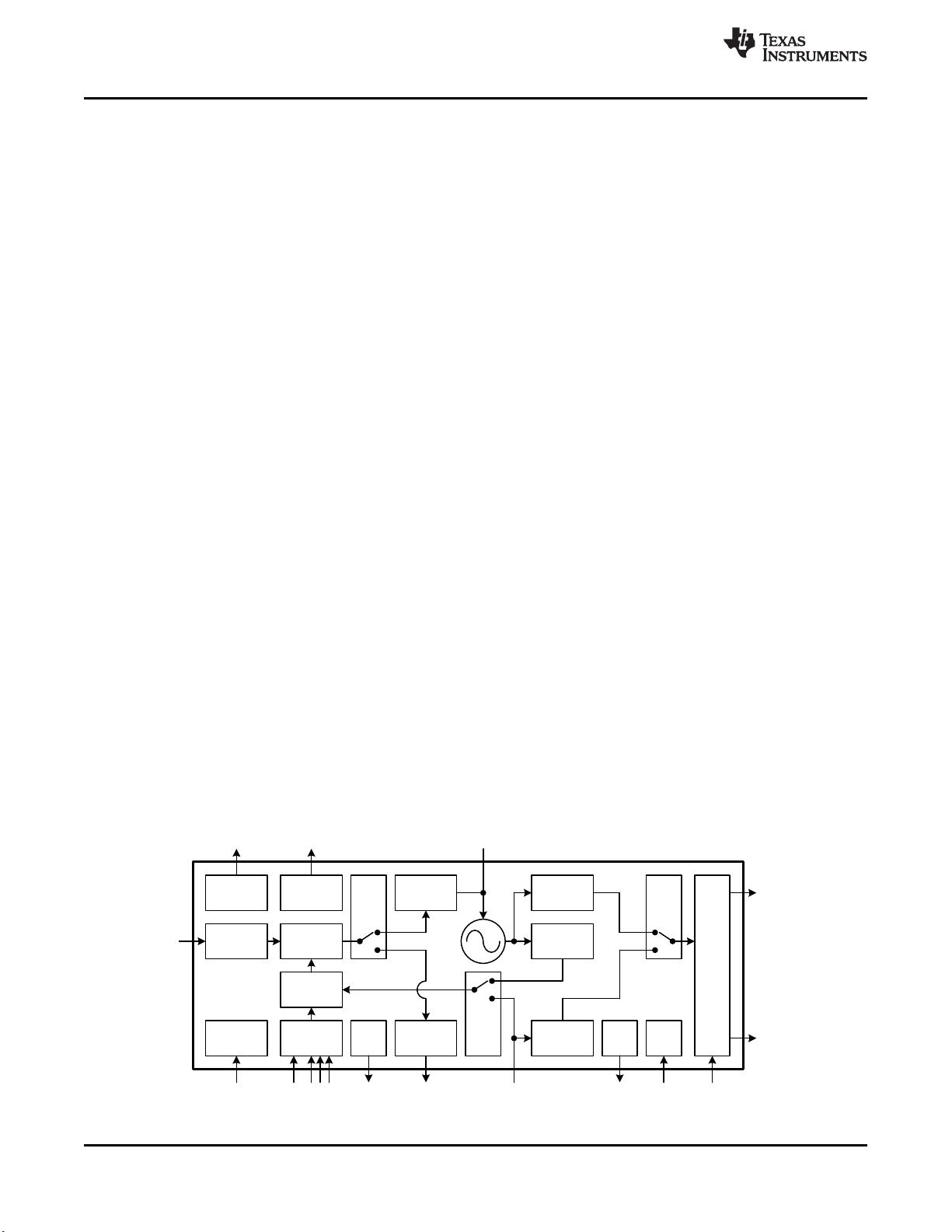

LMX2571

www.ti.com.cn

ZHCSDH8 –MARCH 2015

7.3 Feature Description

7.3.1 Reference Oscillator Input

The OSCin and OSCin* pins are used as frequency reference inputs to the device. The OSCin pin can be driven

single-ended with a CMOS clock or a crystal oscillator. The on-chip crystal oscillator can also be used with an

external crystal as the reference clock. Differential clock input is also supported, making it easily to interface with

high performance system clock devices such as TI’s LMK series clock devices.

Because the OSCin or OSCin* signal is used as a clock for VCO calibration, a proper signal needs to be applied

at the OSCin and/or OSCin* pin at the time of programming the R0 register. A higher slew rate tends to yield the

best fractional spurs and phase noise, so a square wave signal is best for the OSCin and/or OSCin*pins. If using

a sine wave, higher frequencies tend to yield better phase noise and fractional spurs due to their higher slew

rates.

7.3.2 R-Dividers and Multiplier

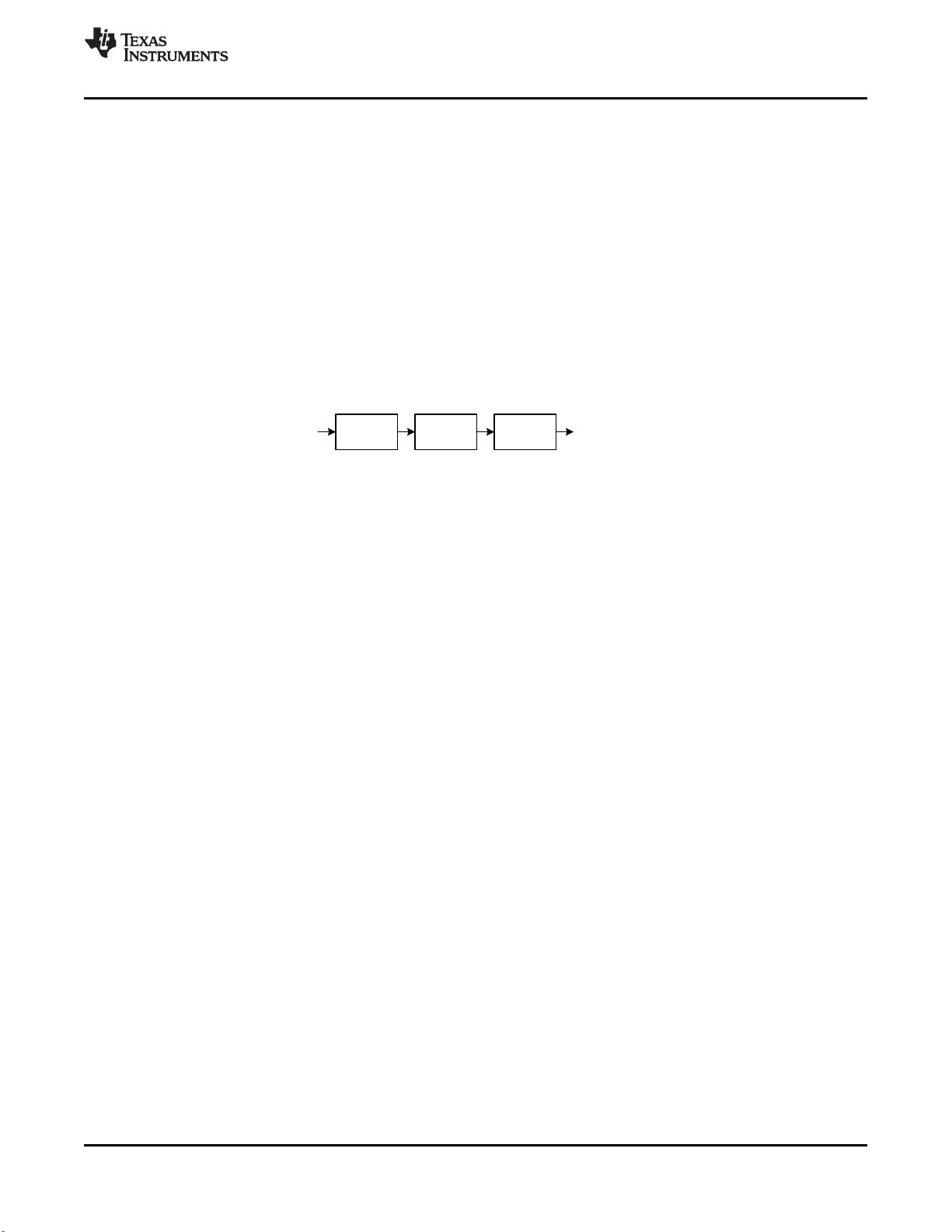

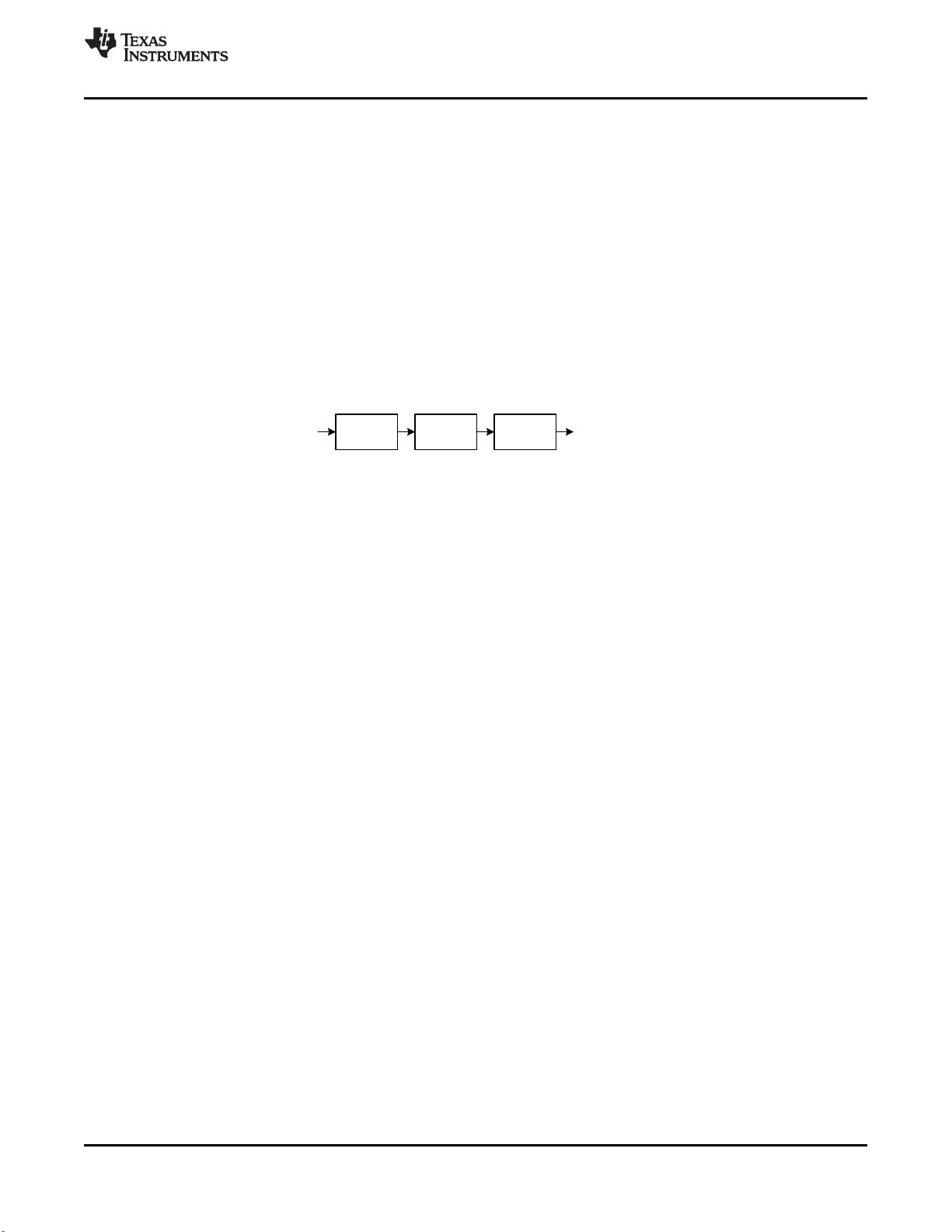

The R-divider consists of a Pre-divider, a Multiplier (MULT), and a Post-divider.

Figure 14. R-Divider

Both the Pre- and Post-dividers divide frequency down while the MULT multiplies frequency up. The purpose of

adding a multiplier is to avoid and reduce integer boundary spurs or to increase the phase-detector frequency for

higher performance. See MULT Multiplier for details. The phase detector frequency, f

PD

, is therefore equal to

f

PD

= (f

OSCin

/ Pre-divider) * (MULT / Post-divider) (1)

When using the Multiplier (MULT > 1), there are some points to remember:

• The Multiplier must be greater than the Pre-divider.

• Crystal mode must be disabled (XTAL_EN=0).

• Using the multiplier may add noise, especially for multiplier values greater than 6.

7.3.3 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the Post-divider and N-divider and generates a correction current

corresponding to the phase error. This charge pump current is programmable to different strengths.

7.3.4 PLL N-Divider and Fractional Circuitry

The total N-divider value is determined by N

integer

+ NUM / DEN. The N-divider includes fractional compensation

and can achieve any fractional denominator (DEN) from 1 to 16,777,215 (2

24

– 1). The integer portion, N

integer

, is

the whole part of the N-divider value and the fractional portion, N

frac

= NUM / DEN, is the remaining fraction.

N

integer

, NUM and DEN are programmable.

The order of the delta sigma modulator is also programmable from integer mode to fourth order. There are

several dithering modes that are also programmable. Dithering is used to reduce fractional spurs. In order to

make the fractional spurs consistent, the modulator is reset any time that the R0 register is programmed.

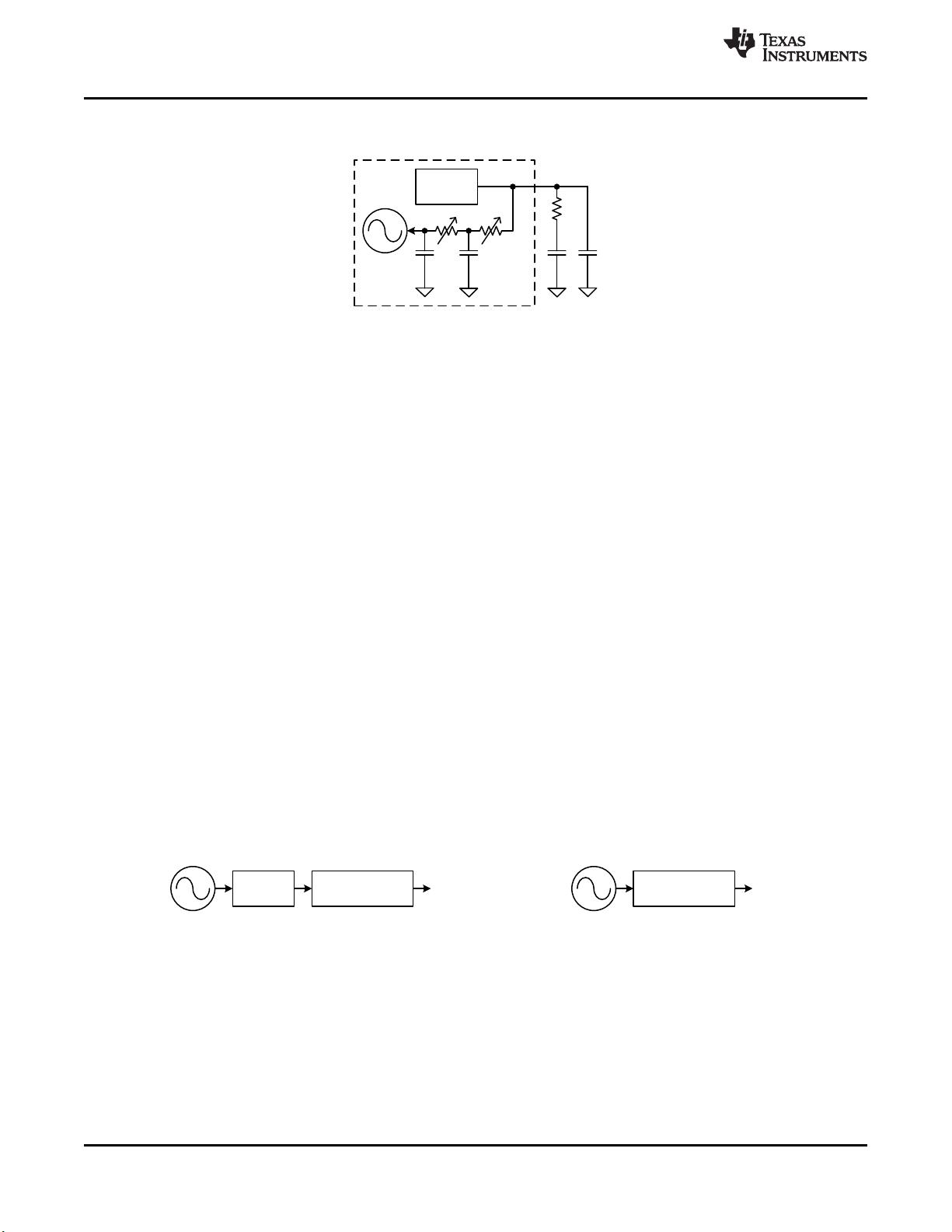

7.3.5 Partially Integrated Loop Filter

The LMX2571 integrates the third and fourth pole of the loop filter. The values for the resistors can be

programmed independently through the MICROWIRE interface. The larger the values of the resistors, the

stronger the attenuation of the internal loop filter. This partially integrated loop filter can only be used in

synthesizer mode.

Copyright © 2015, Texas Instruments Incorporated 11