FPGA/CPLD数字电路设计:时序优化与避免冒险现象

需积分: 10 139 浏览量

更新于2024-08-01

收藏 1021KB PDF 举报

"FPGA/CPLD数字电路设计经验分享,关注时序、延时和毛刺问题"

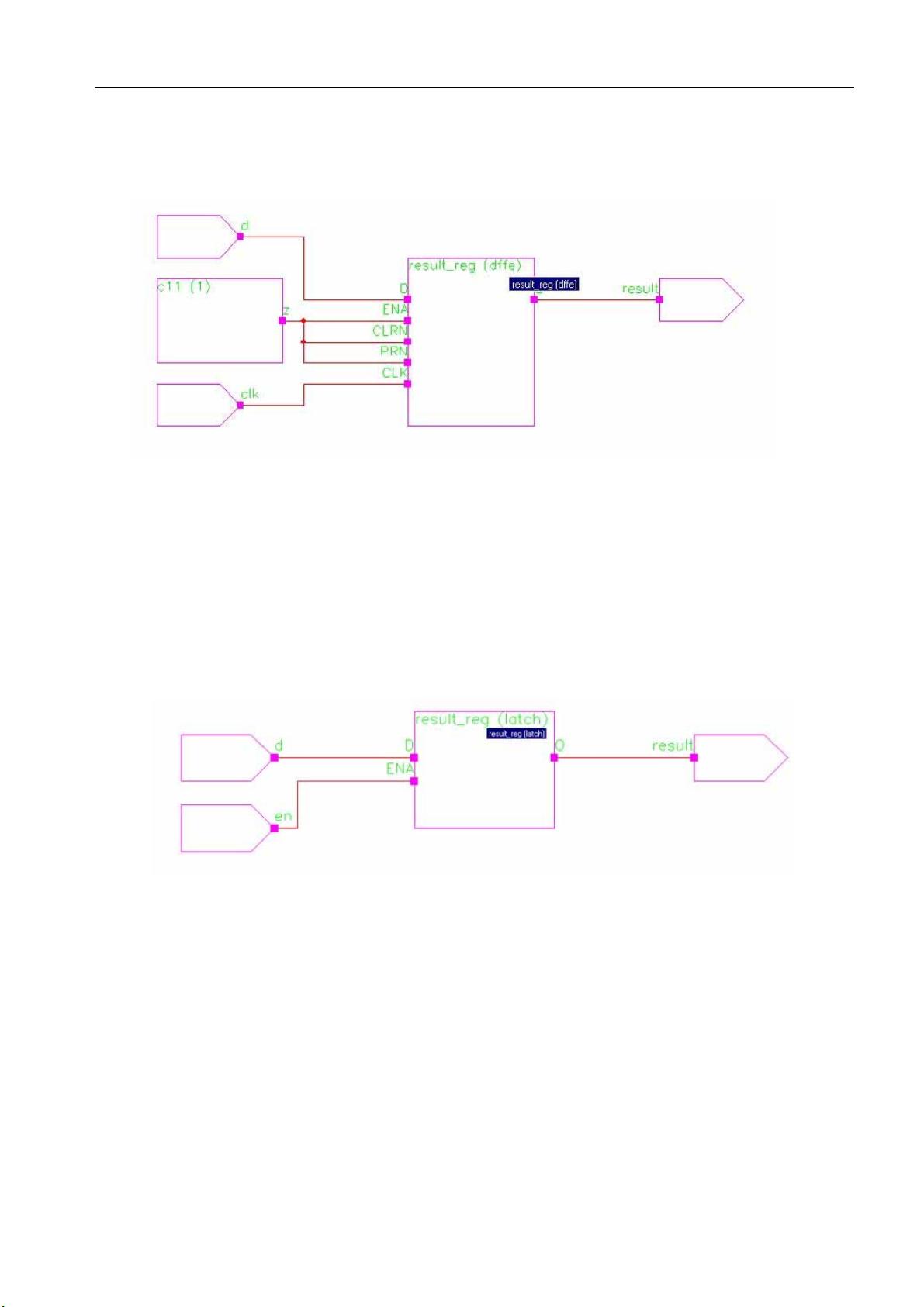

在FPGA和CPLD数字电路设计中,掌握关键概念和技术是至关重要的。时序设计是确保系统正确运行的核心,因为它涉及到数据在时钟边沿被正确捕获的时机。建立时间和保持时间是时序设计的两个基本要素。

建立时间(setuptime)是指数据必须在时钟脉冲上升沿之前稳定多长时间,以确保在时钟触发时数据能被正确地加载到触发器中。如果建立时间不足,数据可能无法正确地被打入触发器,导致错误。相反,保持时间(holdtime)是指时钟上升沿之后数据需要保持稳定的时间,以避免数据在触发器内部被破坏。如果保持时间不够,同样可能导致数据错误。

在设计过程中,PLD/FPGA开发工具会计算输入之间的建立时间和保持时间,帮助设计师确保设计满足这些要求。值得注意的是,建立时间与时钟周期紧密相关,可以通过减慢时钟频率来解决建立时间问题。然而,保持时间并不依赖于时钟周期,一旦设计不合理,即使改变时钟频率也无法解决问题,可能需要对设计进行大幅度修改。

FPGA中的竞争和冒险现象是另一个需要关注的问题。由于内部信号传播的延迟和电平转换的过渡时间,多个信号同时变化时可能会导致组合逻辑输出的尖峰或毛刺。这些不期望的信号波动可能会引发系统不稳定,需要通过适当的设计和布线策略来避免。

为了解决这些问题,设计师需要在RTL级进行时序分析,理解逻辑路径的延迟,并使用综合和布局布线工具来优化设计。此外,使用适当的时钟管理技术,如分频器和时钟缓冲器,可以帮助控制时钟树的偏斜,从而改善时序性能。

在FPGA/CPLD设计中,模拟和验证也是关键步骤。预仿真和后仿真能够检查设计是否满足时序约束,而静态时序分析则能提供更深入的理解,帮助确定潜在的时序问题。通过这些工具和方法,设计师可以优化设计,确保其在各种条件下都能稳定工作。

理解和处理好时序、延时和毛刺问题是FPGA/CPLD数字电路设计成功的关键。这需要对基本概念有深入理解,以及熟练运用设计工具和最佳实践。通过不断的学习和实践,设计师可以提高设计效率和系统的可靠性。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

511 浏览量

2025-01-01 上传

2025-01-01 上传

2025-01-01 上传

dianke05101

- 粉丝: 8

- 资源: 19