FPGA实现的位同步时钟DPLL设计与自同步法探讨

23 浏览量

更新于2024-08-30

收藏 942KB PDF 举报

"基于FPGA的位同步时钟DPLL设计主要关注数字通信系统中的同步技术,特别是位同步,这是通信系统中的基础。位同步时钟的作用在于保证接收端与发送端的码元信号同步,同时为系统提供一个基准时钟,以确保数据正确解调和判决。位同步有两种方法:外同步法和自同步法。外同步法需要额外的同步信息传输,而自同步法则直接从信号码元中提取位同步信息,更常见且更实用。

自同步法进一步分为开环和闭环两种策略。开环同步不涉及反馈机制,通过变换输入码元来提取位同步信息;闭环同步,也就是本文采用的方法,它利用比较本地时钟和输入信号的相位差异,通过反馈调整本地时钟,使其锁定在输入信号上,从而实现更精确的同步,但实现起来也更复杂。

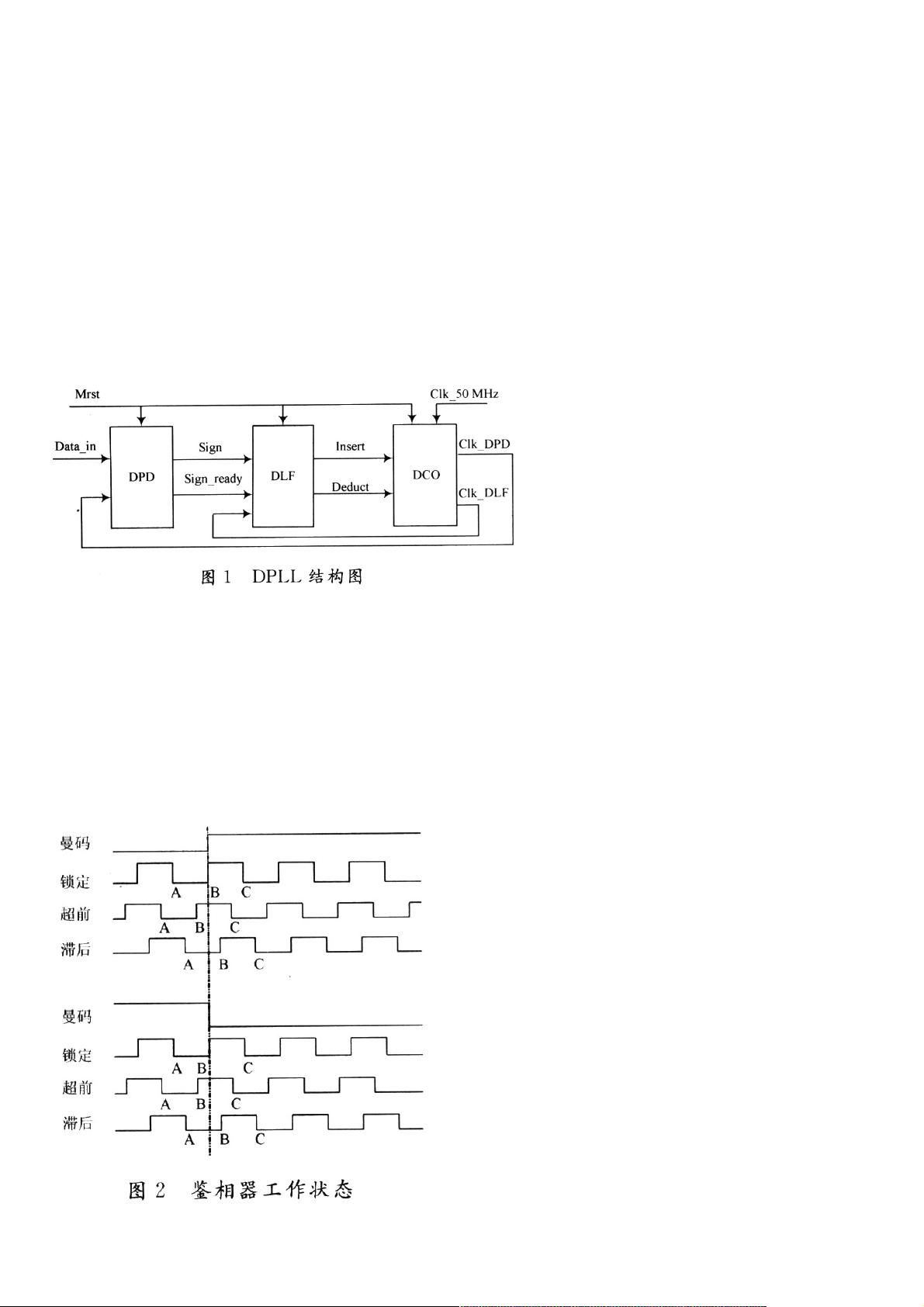

在DPLL(数字相位锁定环)系统中,鉴相器是核心组件。超前-滞后型鉴相器能检测到本地估算信号相对于输入信号的超前或滞后,并产生相应的控制信号。微分型鉴相器因其简洁的结构和实现方式被选用,尽管其抗干扰能力相对较弱,但可以通过后续的数字滤波器环节来弥补这一不足。鉴相器的输出Sign表示本地时钟与输入信号的相位关系,Sign_ready信号则指示鉴相器何时能够提供有效的相位比较结果。

整个DPLL环路还包括其他关键组件,如低通滤波器(LPF)和电压控制振荡器(VCO)。LPF负责平滑鉴相器的输出,减少噪声影响,而VCO根据LPF的输出调整其频率,从而改变本地时钟的相位,达到与输入信号同步的目的。这样的设计使得DPLL能够动态适应输入信号的变化,保持系统的稳定同步。

基于FPGA的位同步时钟DPLL设计是数字通信系统中解决同步问题的关键技术,通过自同步法和闭环控制实现高精度的位同步,确保数据的准确传输。这种设计利用FPGA的灵活性和高速处理能力,实现了实时、高效的时钟同步功能。"

389 浏览量

302 浏览量

426 浏览量

477 浏览量

2021-02-03 上传

157 浏览量

509 浏览量

938 浏览量

520 浏览量

weixin_38706951

- 粉丝: 4

- 资源: 930