VHDL在EDA/PLD中的应用:多功能可变模计数器设计

63 浏览量

更新于2024-08-30

2

收藏 350KB PDF 举报

"EDA/PLD中的基于VHDL的多功能可变模计数器设计"

本文探讨了在EDA(电子设计自动化)/PLD(可编程逻辑器件)领域中,如何利用VHDL(Very High Speed Integrated Circuit Hardware Description Language)设计一种多功能可变模计数器。随着电子技术、计算机技术以及EDA技术的持续进步,FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)在通信、航天、医疗电子和工业控制等多个领域得到了广泛应用。

FPGA和CPLD相较于传统的电路设计方法,具有显著优势,如功能强大、开发周期短、成本较低、适应市场变化的灵活性高以及开发工具的智能化。近年来,随着集成电路制造工艺的不断提升,高性能且价格合理的FPGA/CPLD器件不断涌现,它们已经成为现代硬件设计的关键技术。

VHDL作为主流的硬件描述语言,其强大的电路描述和建模能力使得设计者可以从多个层次对数字系统进行建模和描述,简化了硬件设计流程,提升了设计效率和可靠性。VHDL的易读性、层次化和结构化设计特性使其在复杂系统设计中具有广阔的应用前景。

QuartusⅡ是Altera公司推出的一款先进的FPGA/CPLD集成开发环境,它继承并超越了前代产品Max+PlusⅡ,提供了友好的用户界面和高效的设计流程。通过QuartusⅡ,设计者可以方便地进行设计输入、快速仿真和设备编程,不受特定硬件结构限制,极大地促进了设计的灵活性。

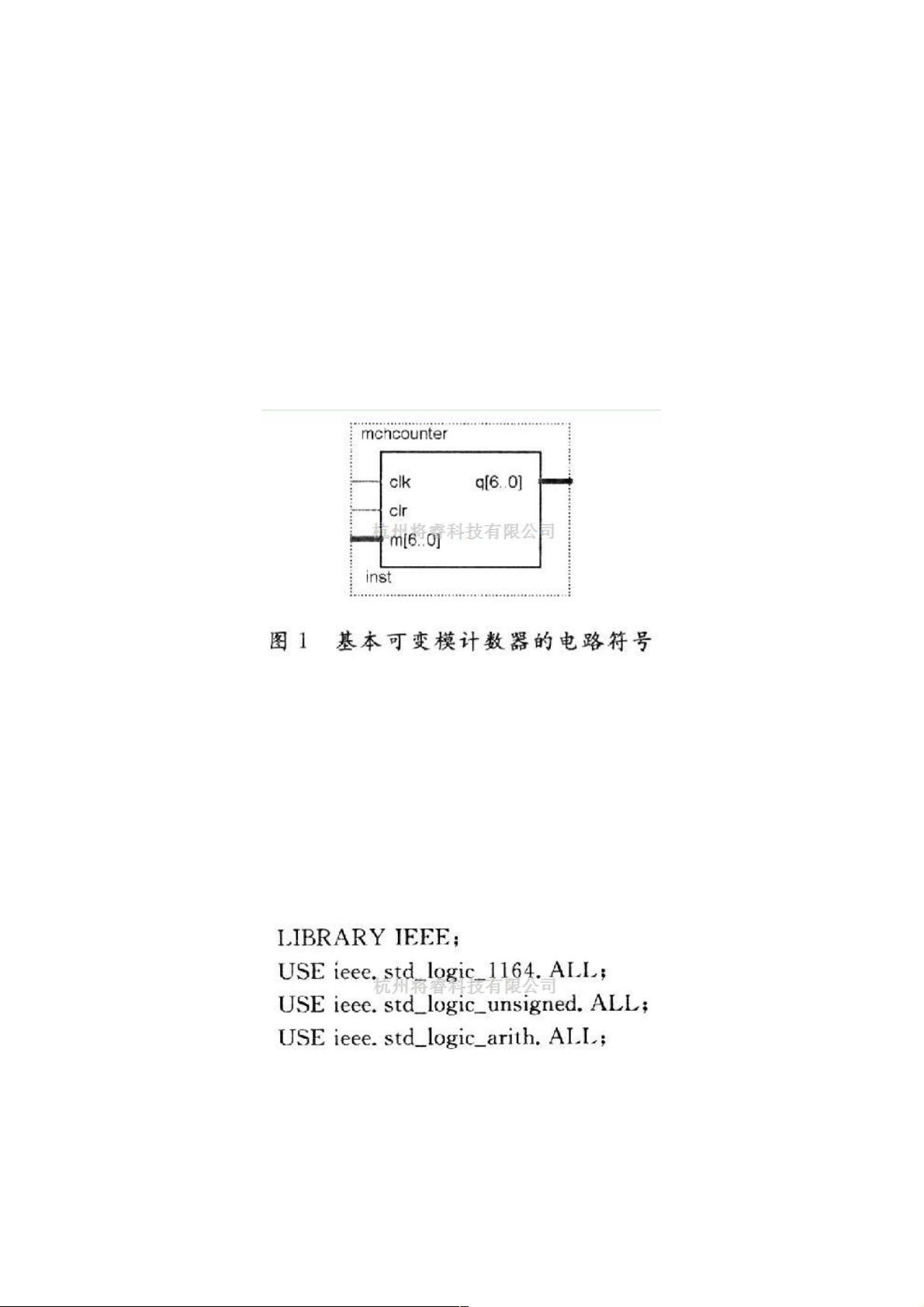

计数器是数字系统的基础组件,通常用于计数时钟脉冲、分频、定时、产生脉冲序列以及参与数字运算。可变模计数器因其计数范围的可调性而具有广泛的应用价值。本文在QuartusⅡ环境中,使用VHDL设计了一款具备清零、置数、使能控制、可逆计数以及可变模功能的高级计数器,这样的计数器能够根据需求灵活配置,满足不同应用场景的需求。

该设计不仅展示了VHDL在FPGA/CPLD设计中的强大功能,也突显了EDA工具在现代电子设计中的核心地位。通过这种设计方法,工程师可以更加高效地开发出适应性强、功能丰富的数字系统,进一步推动了电子技术的发展。

2009-11-09 上传

2020-11-09 上传

2020-12-10 上传

2020-12-08 上传

2020-11-09 上传

2020-11-07 上传

2020-11-10 上传

2020-12-10 上传

weixin_38660295

- 粉丝: 6

- 资源: 910

最新资源

- MCP C#试用试题

- nutch初学入门 非常好的入门教程

- c#面试题 网络转载 不错 经典

- C#设计模式大全 好书

- Struts+Spring+Hibernate整合教程.pdf

- BP神经网络原理及仿真实例

- 使用简介POWERPLAY

- Oracle 9i10g编程艺术

- scm手把手开发文档

- Cognos Impromptu

- LoadRunner安装手册.pdf

- cognos 部署 文档

- 用C语言进行单片机程序设计与应用

- Direct3D.ShaderX.-.Vertex.and.Pixel.Shader.Tips.and.Tricks.pdf

- 《uVision2入门教程》.pdf

- spring1.2申明式事务.txt