FPGA跨时钟域信号处理:亚稳态现象与解决方案

165 浏览量

更新于2024-09-04

收藏 245KB PDF 举报

本文主要讨论的是基于FPGA的跨时钟域信号处理中的一个重要概念——亚稳态。在FPGA设计中,尤其是在实现异步通信时,信号的传输往往跨越不同的时钟周期,这就涉及到时序约束的问题。文章首先提到了上一篇博客中关于专用握手信号的使用,通过req、data和ack等信号来确保数据在不同时钟域间的可靠传输。然而,当这些直接的跨时钟域信号(如req和ack)被目标时钟域的寄存器同步时,可能会出现亚稳态现象。

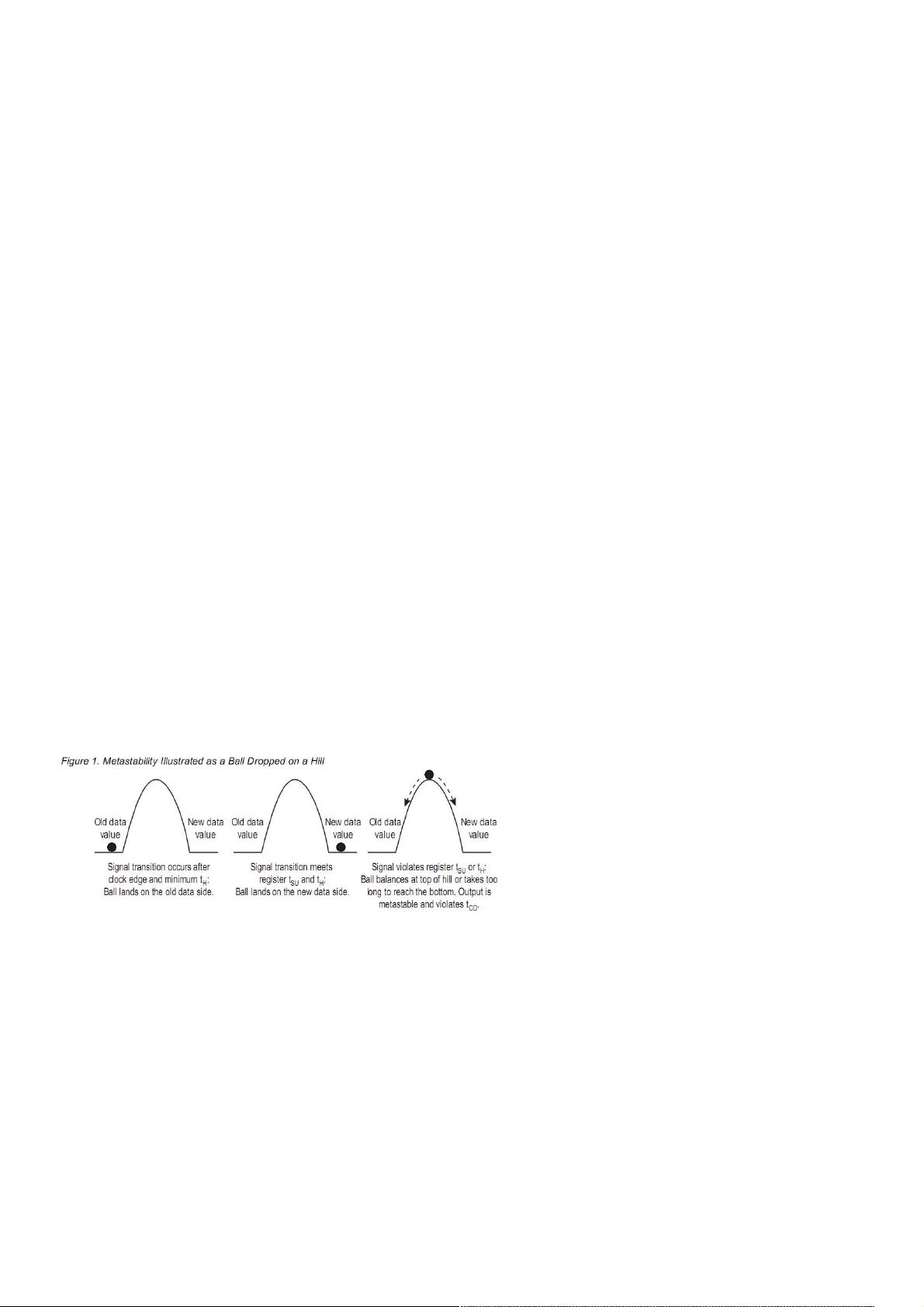

亚稳态是指寄存器在接收输入信号时,由于输入信号变化未能满足建立时间和保持时间的要求,导致其输出在高电平和低电平之间徘徊的不稳定状态。这种现象对系统的稳定性和可靠性构成威胁,因为在亚稳态期间,寄存器的输出状态无法确定,可能导致错误的逻辑结果。

《ApplicationNote42: Metastability in Altera Devices》这篇官方文档对亚稳态问题进行了详尽的阐述,作者通过阅读该文档解决了自己之前的疑惑。文中提到,虽然Altera公司在文章中强调了自己的产品优势,但读者可以通过原文或特权同学的翻译理解这一复杂概念。

设计者在处理跨时钟域信号时,必须考虑到亚稳态的可能性,并采取适当的措施,如增加适当的延时、使用锁存器(latch)来缓冲数据、或者使用特殊的亚稳态检测和恢复机制,以减少亚稳态的发生概率。此外,寄存器进入亚稳态后恢复到稳定状态的时间取决于器件的制造工艺和工作环境,这在实际设计中也是需要考虑的因素。

总结来说,亚稳态是FPGA跨时钟域信号处理中的关键问题,它涉及到信号的时序控制和可靠性,设计者需要充分理解并采取有效的策略来避免或减小亚稳态的影响,以确保系统的稳定运行。

2016-12-19 上传

2020-08-12 上传

2020-01-05 上传

2023-05-19 上传

2023-07-27 上传

2023-03-28 上传

2023-10-14 上传

2023-03-22 上传

2023-06-06 上传

weixin_38528459

- 粉丝: 4

- 资源: 974

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构