数字电路与逻辑设计:CH4 集成触发器详解

版权申诉

113 浏览量

更新于2024-07-02

收藏 3.63MB PDF 举报

"数字电路与逻辑设计:CH4 集成触发器.pdf"

本文档主要讲解了数字电路中的集成触发器,特别是时钟RS触发器的相关知识。集成触发器是数字逻辑系统中一种重要的存储元件,它能够保持其状态,直到接收到新的输入指令。在数字电路与逻辑设计中,触发器的运用至关重要,因为它们是构建时序逻辑电路的基础。

首先,文档介绍了由门电路构成的记忆单元,这种单元电路通过输出反馈到输入来保持状态,并且可以有稳定的不同输出。基本的RS触发器是一种简单类型的记忆单元,它由两个输入(R和S)和两个互补输出(Q和Q')组成。RS触发器的工作原理是,当R=1且S=0时,输出Q清零;当R=0且S=1时,输出Q置位;如果R和S都为0,则输出状态保持不变;而当R和S同时为1时,由于没有定义明确的输出状态,所以这种情况是不允许的,称为“不确定”状态。

接下来,文档展示了基于与非门和或非门构建的RS触发器的逻辑图。这两种门电路的使用使得RS触发器可以实现所需的功能。为了提高RS触发器的稳定性,防止外部干扰影响其状态,引入了时钟RS触发器的概念。时钟RS触发器通过在输入端增加门控电路,只有在时钟脉冲(CP)为高电平时,输入信号才会对触发器状态产生影响,这样可以确保在时钟无效期间触发器的状态保持不变,增强了其抗干扰能力。

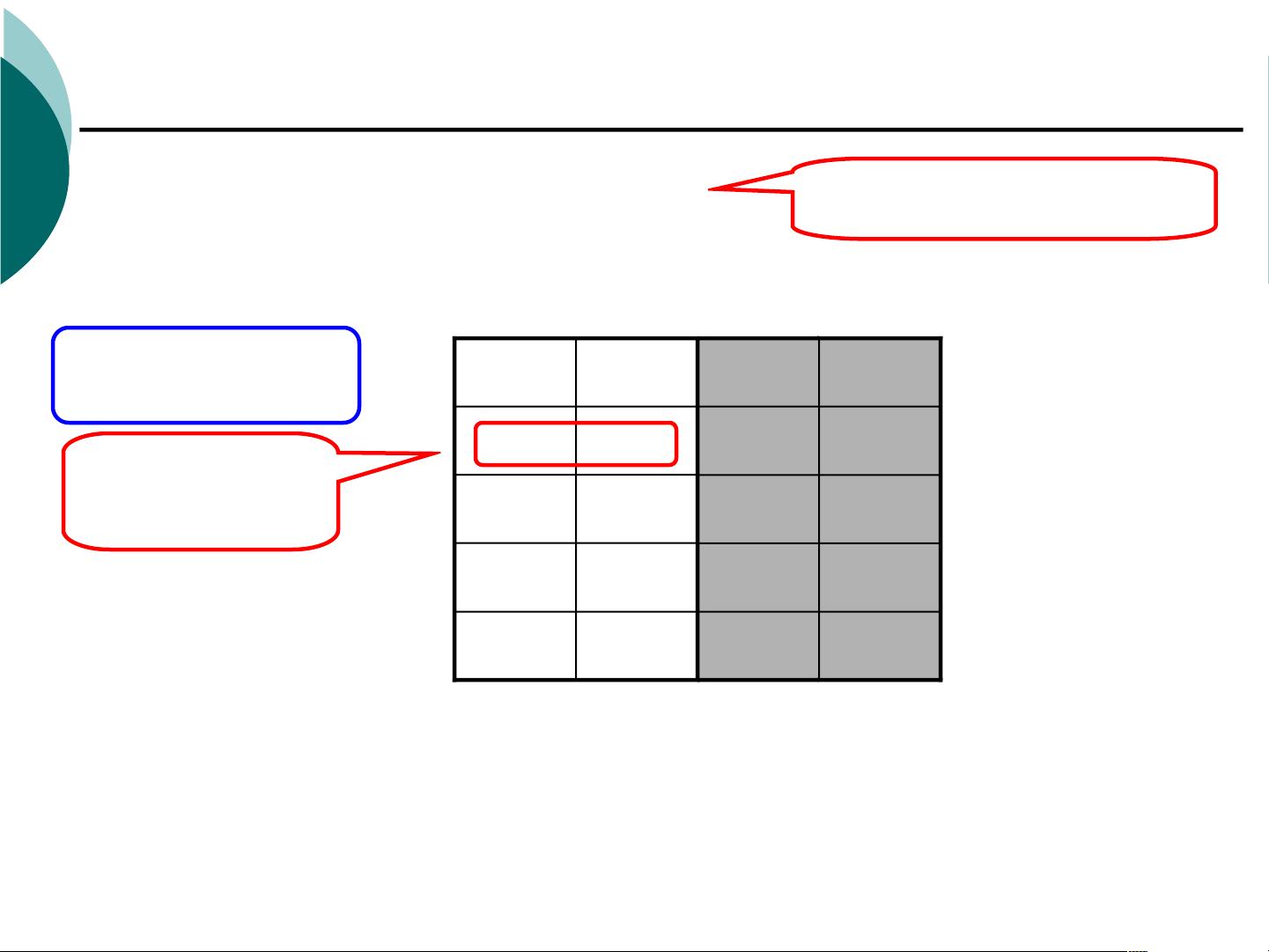

时钟RS触发器引入的结果是建立了一个基于时钟脉冲的时序体系,输出信号的变化会按照时钟节拍进行,即输出状态Qn+1依赖于当前状态Qn和时钟脉冲。根据是否受时钟影响,输入信号被分为同步控制信号(如时钟有效时的RS信号)和异步控制信号(不受时钟影响)。文档中提供了时钟RS触发器的真值表、状态转换真值表、特征方程和激励表,这些工具可以帮助理解触发器的工作行为。

时钟RS触发器的特征方程为Qn+1 = R'Qn + SQn,其中限制条件是RS ≠ 0,这意味着在任何时刻R和S不能同时为1。激励表则展示了不同输入组合下触发器的输出变化,例如R=1,S=0表示清零操作,R=0,S=1表示置位操作,而R=0,S=0表示维持当前状态。

最后,文档通过状态图和工作波形进一步阐述了时钟RS触发器的动态行为,如RS=01、RS=10和RS=0Φ(时钟未激活)时的工作情况。这些图形化的表示有助于直观理解触发器在不同输入条件下的响应。

该文档深入浅出地讲解了数字电路中集成触发器的原理,特别是时钟RS触发器的构造、功能和操作特性,为学习数字逻辑设计提供了基础理论知识。

108 浏览量

510 浏览量

183 浏览量

170 浏览量

391 浏览量

151 浏览量

103 浏览量

101 浏览量

2023-07-13 上传

wxg520cxl

- 粉丝: 25

- 资源: 3万+

最新资源

- rsync配置与使用(v2.0)

- SUSE Linux Enterprise Server操作系统安装手册

- matlab课件matlab绘图Matlab计算与仿真技术

- NET and C#外文翻译(下载前请看“软件说明”)

- 数字电子技术基础 阎石第四版课后习题答案

- java实现工作流以及工作流的处理

- 用 Apache 和 Subversion 搭建安全的版本控制环境

- matlab应用大全

- WCF安全指南 WCF Security Guide

- unix下的vi入门命令集锦

- C++_tutorial.pdf

- 计算机三级C语言91-100

- 电子行业的英语词汇大全

- informix 常用命令

- 《信号与系统》实验讲义 matlab

- EM78811数据手册