FPGA实现的实时视频图像缩放系统

版权申诉

88 浏览量

更新于2024-06-19

1

收藏 8.92MB PDF 举报

"这篇毕业论文主要探讨了实时视频图像缩放系统的FPGA硬件实现,针对摄像头采集的固定分辨率源视频在不同显示器上显示时分辨率不一致的问题,利用FPGA构建了一个能够满足各种分辨率需求的实时视频图像缩放系统。文章研究了三种图像缩放算法,包括最近邻域算法和双线性插值算法,并通过MATLAB进行仿真,最终选择了这两种算法进行硬件实现。系统设计遵循模块化思路,包含图像采集、跨时钟FIFO、图像缩放、图像缓存、HDMI显示和串口解析等模块。在图像缩放模块中,提出了RFIFO缓存策略,并详细阐述了读写控制、坐标系数生成和插值运算的过程。论文使用Verilog语言和IP核完成了各模块设计,并通过仿真、综合和实现验证,最终在硬件板级验证中,系统能输出清晰无失真的24位及以上色彩的视频图像。关键词包括FPGA、最近邻域插值、双线性插值、图像缩放和仿真验证。"

这篇论文深入研究了如何利用FPGA技术解决实时视频图像缩放的问题。FPGA(现场可编程门阵列)因其高速处理能力和硬件级别的实时性,成为处理视频图像的理想平台。论文首先介绍了数字视频图像的特点,指出传统软件处理方法在实时性方面的不足,然后转向FPGA硬件实现的优势。

作者探讨了三种图像缩放算法,分别是最近邻域算法、双线性插值算法以及其他未明确指定的一种算法。通过MATLAB进行仿真实验,比较了各种算法的性能和实现复杂度,最后选择了最近邻域和双线性插值算法。这两种算法在保持图像质量和简化硬件实现之间找到了平衡。

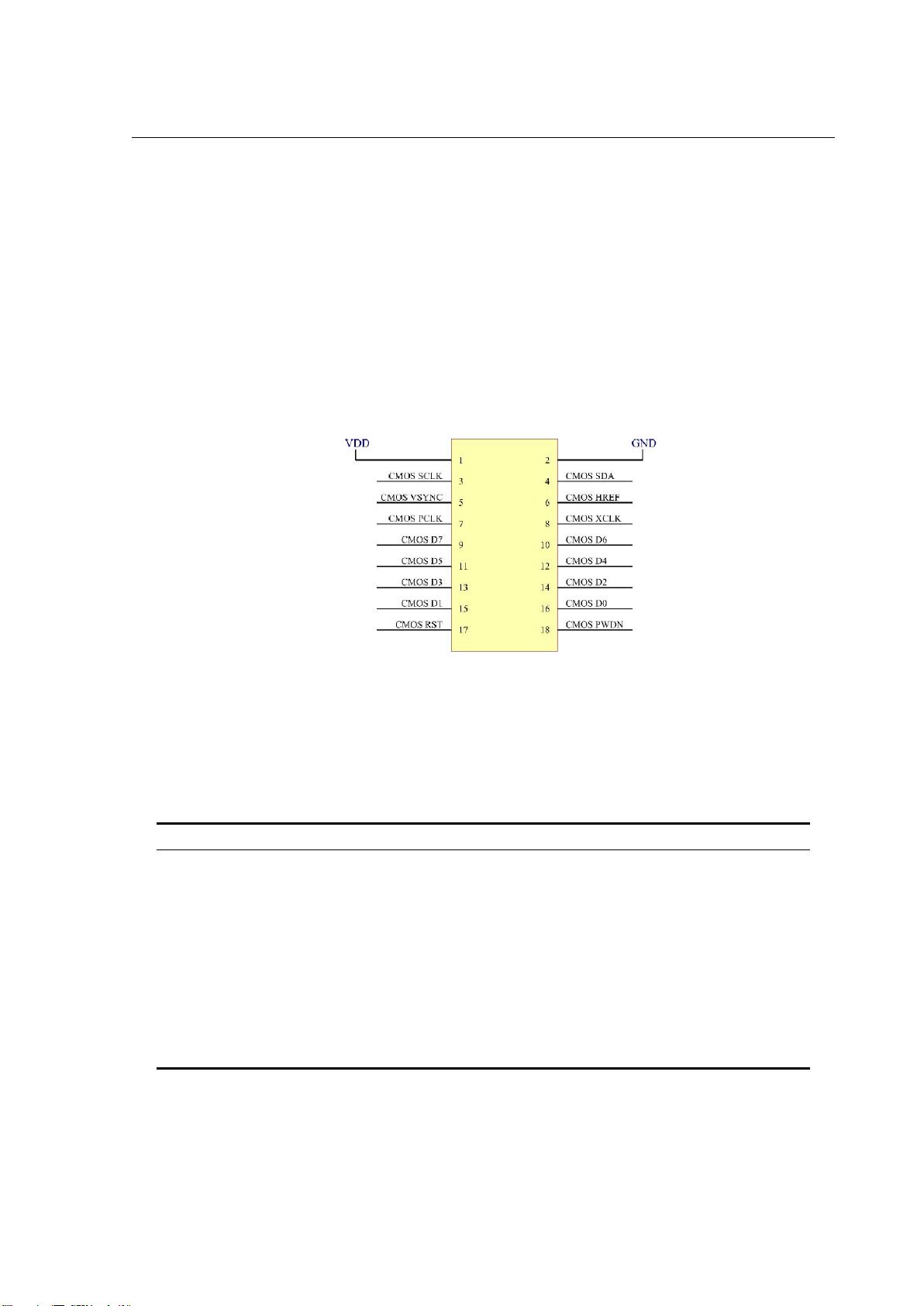

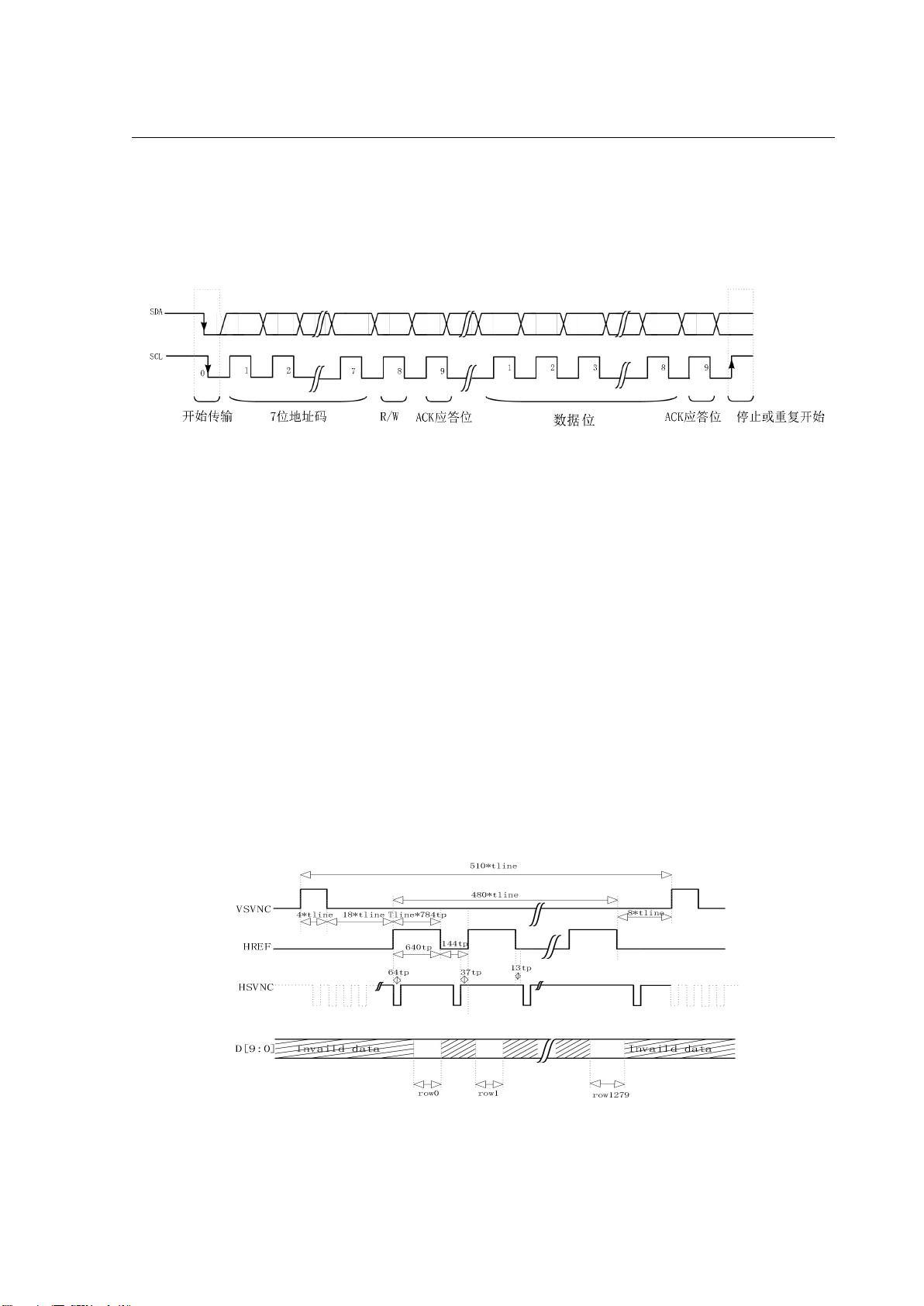

系统设计上,论文采用了模块化的思路,包括图像采集模块负责获取原始视频数据,跨时钟FIFO模块用于不同时钟域的数据传输,图像缩放模块执行图像尺寸变换,图像缓存模块确保数据流的连续性,HDMI显示模块用于将处理后的图像呈现在显示器上,而串口解析模块则接收和处理上位机的指令,以控制输出图像的分辨率。

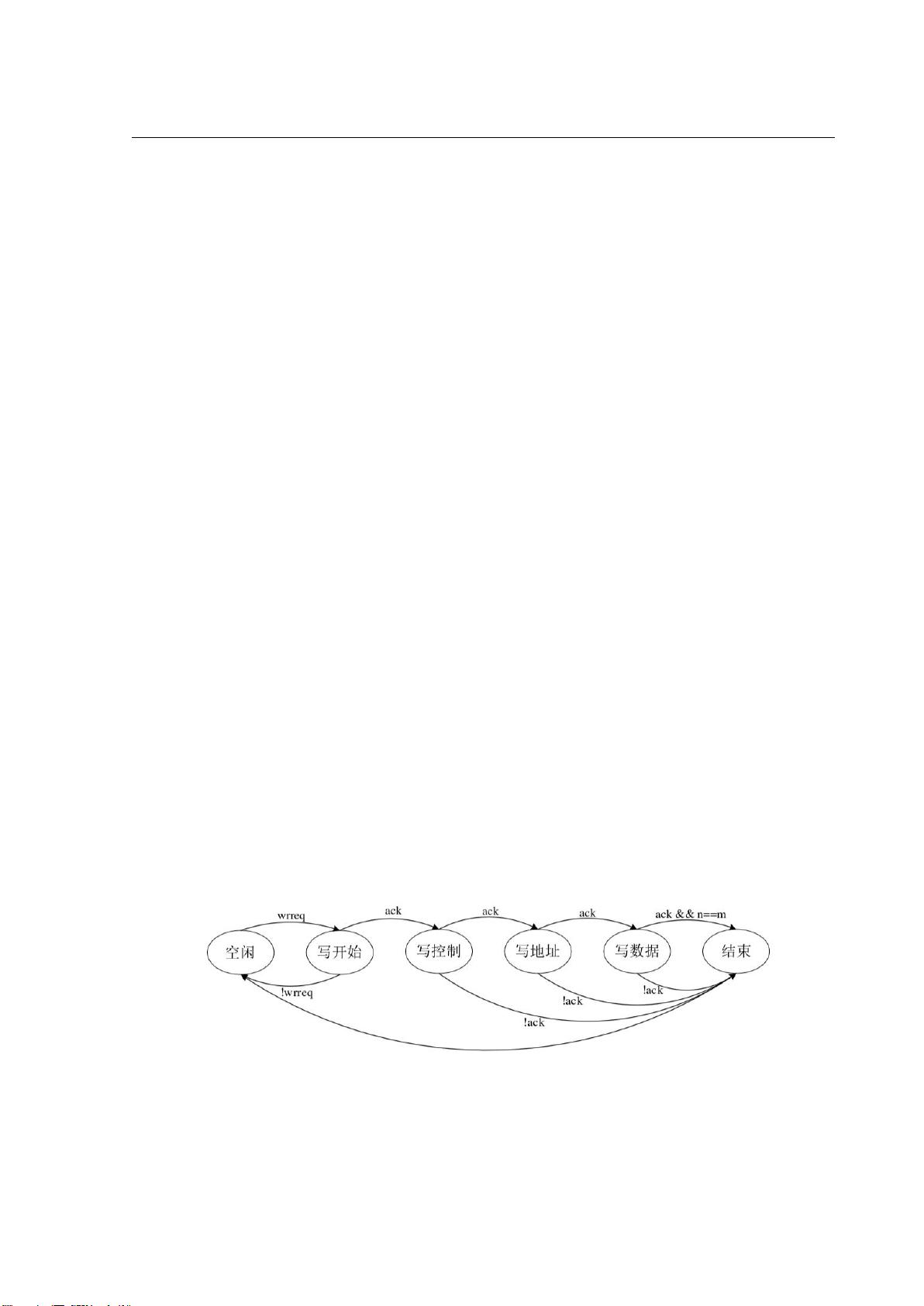

在图像缩放模块的核心——RFIFO缓存方案中,论文详细阐述了读写控制策略,以及如何生成坐标和系数,最后执行插值运算以实现图像的平滑缩放。所有的模块设计都使用Verilog语言实现,并进行了功能仿真验证。经过综合和实现,生成的比特流文件被烧录到FPGA芯片中,通过ILA逻辑分析仪进行板级验证,证明了该设计能够有效工作,输出高质量的视频图像。

这篇论文为实时视频图像缩放提供了一种基于FPGA的高效解决方案,对于需要实时处理大量视频数据的应用场景,如监控、直播或多媒体系统,具有重要的实践意义。

2023-10-30 上传

2023-10-30 上传

2023-10-30 上传

2023-07-22 上传

2023-07-11 上传

2024-06-13 上传

2023-07-27 上传

2023-06-06 上传

2023-07-31 上传

xox_761617

- 粉丝: 25

- 资源: 7802

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析