AX88772BLF / AX88772BLI

Low-power

USB 2.0 to 10/100M Fast Ethernet Controller

Copyright © 2010-2015 ASIX Electronics Corporation. All rights reserved.

3.4 Checksum Offload Engine (COE)

The Checksum Offload Engine (COE) supports IPv4, IPv6, layer 4 (TCP, UDP, ICMP, ICMPv6 and IGMP) header

processing functions and real time checksum calculation in hardware

The COE supports the following features in layer 3:

IP header parsing, including IPv4 and IPv6

IPv6 routing header type 0 supported

IPv6 in IPv4 tunnel supported

IPv4 header checksum check and generation (There is no checksum field in IPv6 header)

Version error detecting on RX direction for IP packets with version != 4 or 6

Detecting on RX direction for IP packets with error header checksum

The COE supports the following features in layer 4:

TCP and UDP checksum check and generation for non-fragmented packet

ICMP, ICMPv6 and IGMP message checksum check and generation for non-fragmented packet

Packet filtering or checksum error indication on RX direction for TCP/UDP/ICMP/ICMPv6/IGMP packets

with error checksum

3.5 Operation Mode

For simple USB 2.0 to Ethernet applications, user can use the AX88772B, which operates with internal Ethernet PHY.

AX88772B supports following three operation modes: (Ref. 2.2 Hardware Setting For Operation Mode And

Multi-Function Pins)

1. MAC mode

2. PHY mode

Below provides a detailed description for the three operation modes:

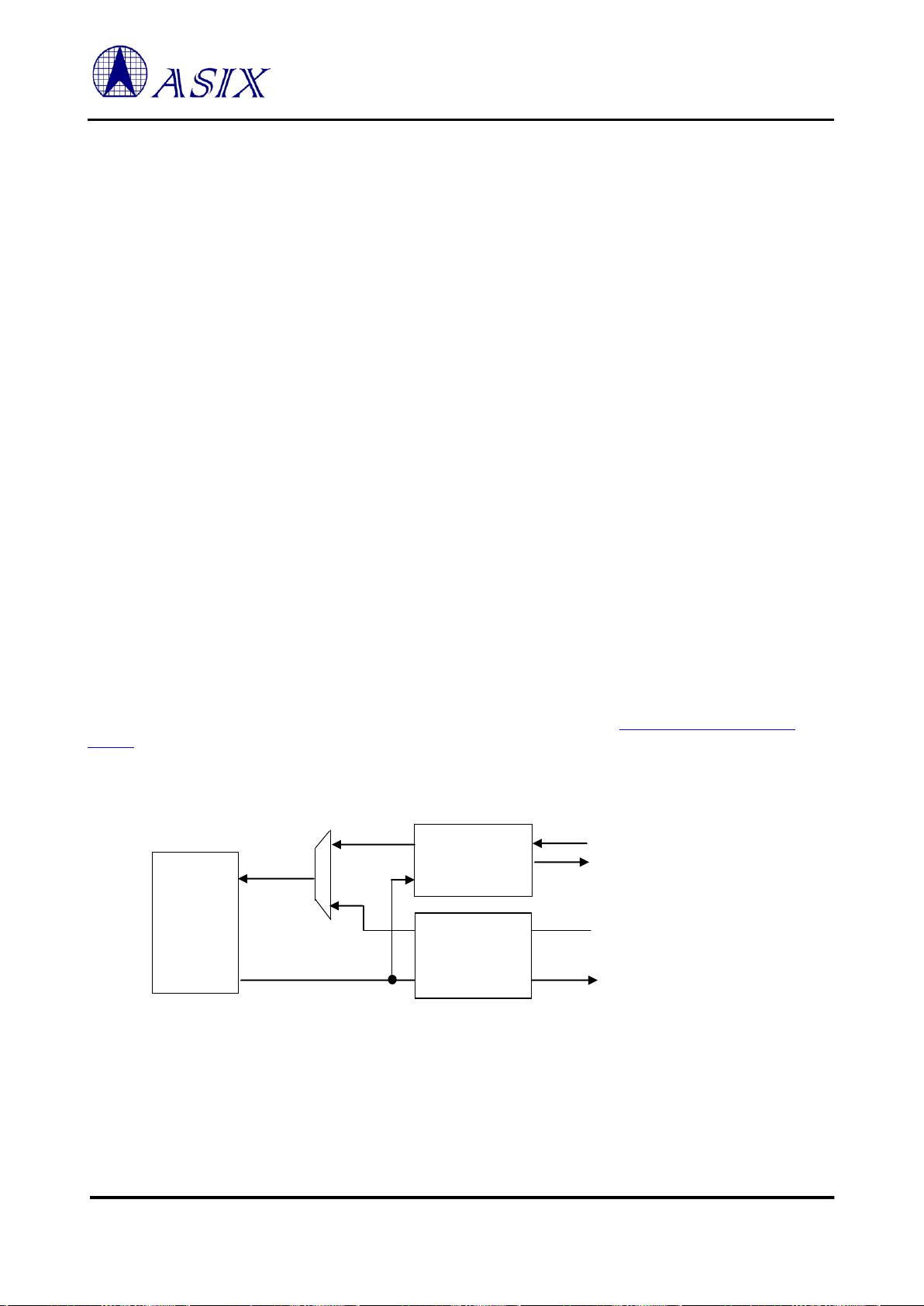

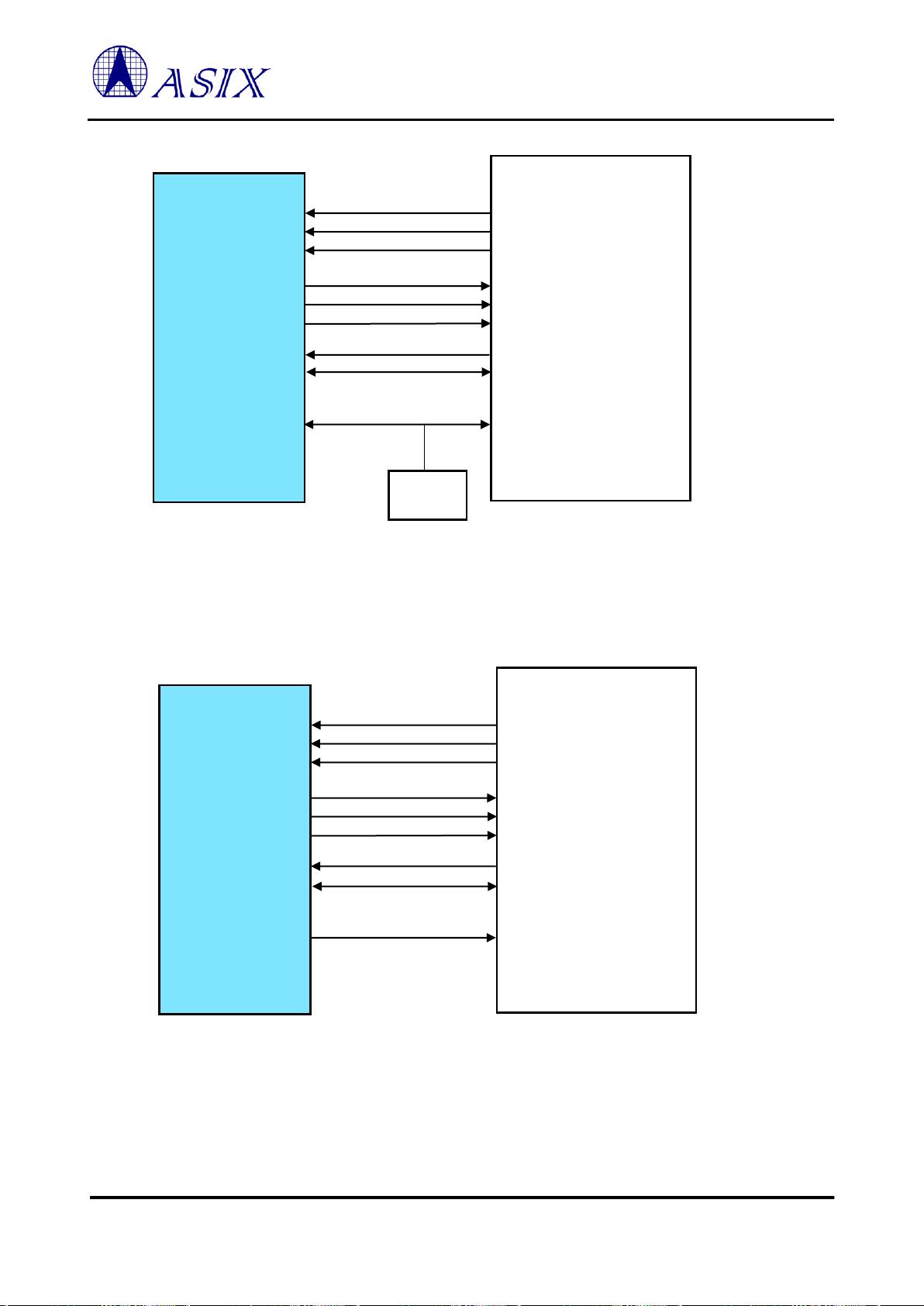

In MAC mode, the AX88772B Ethernet block is configured as an Ethernet MAC. From a system application

standpoint, AX88772B can be used as a USB 2.0 to LAN Adaptor (see Figure 2) or a USB 2.0 to Fast Ethernet and

HomePNA Combo (see Figure 3).

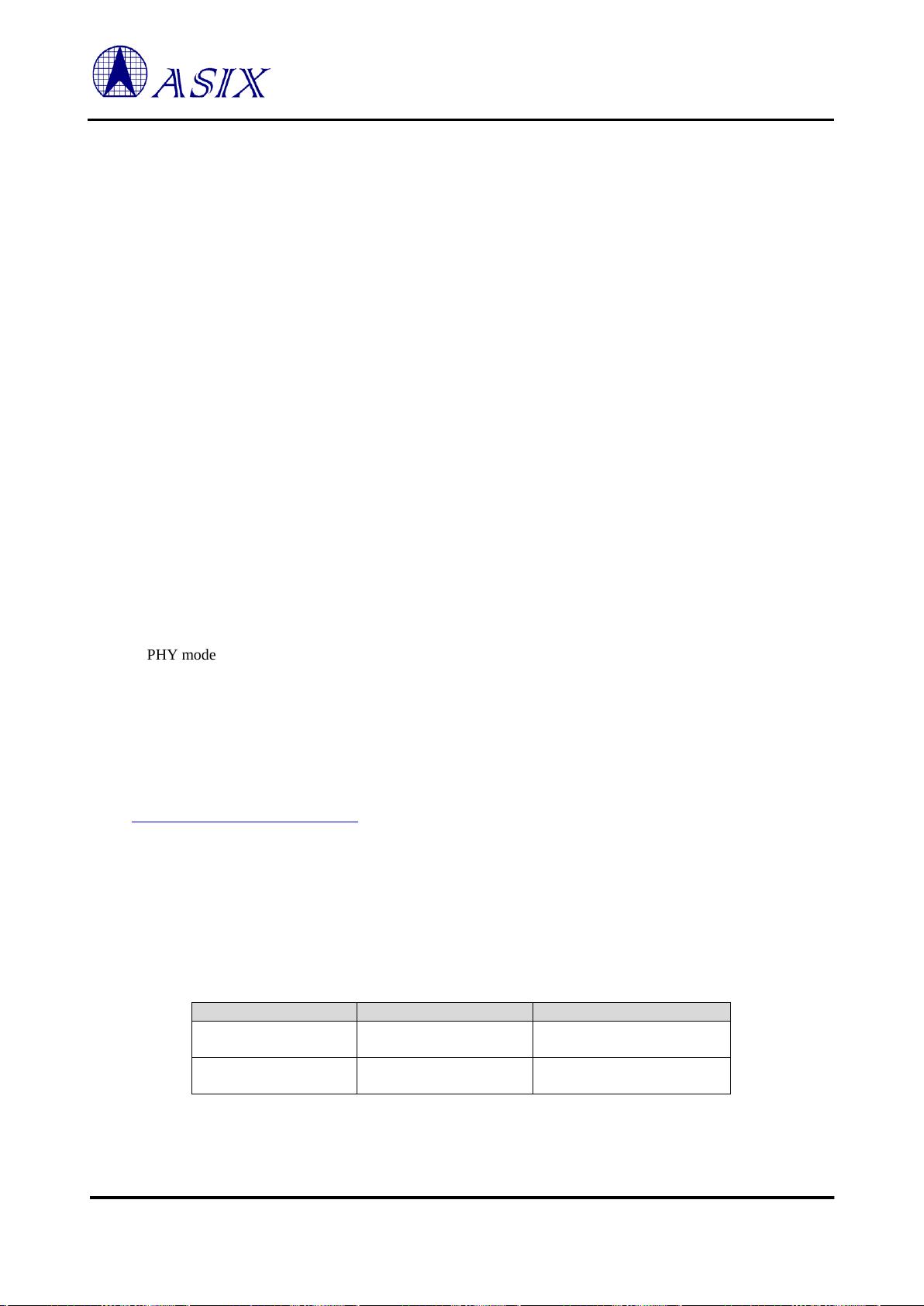

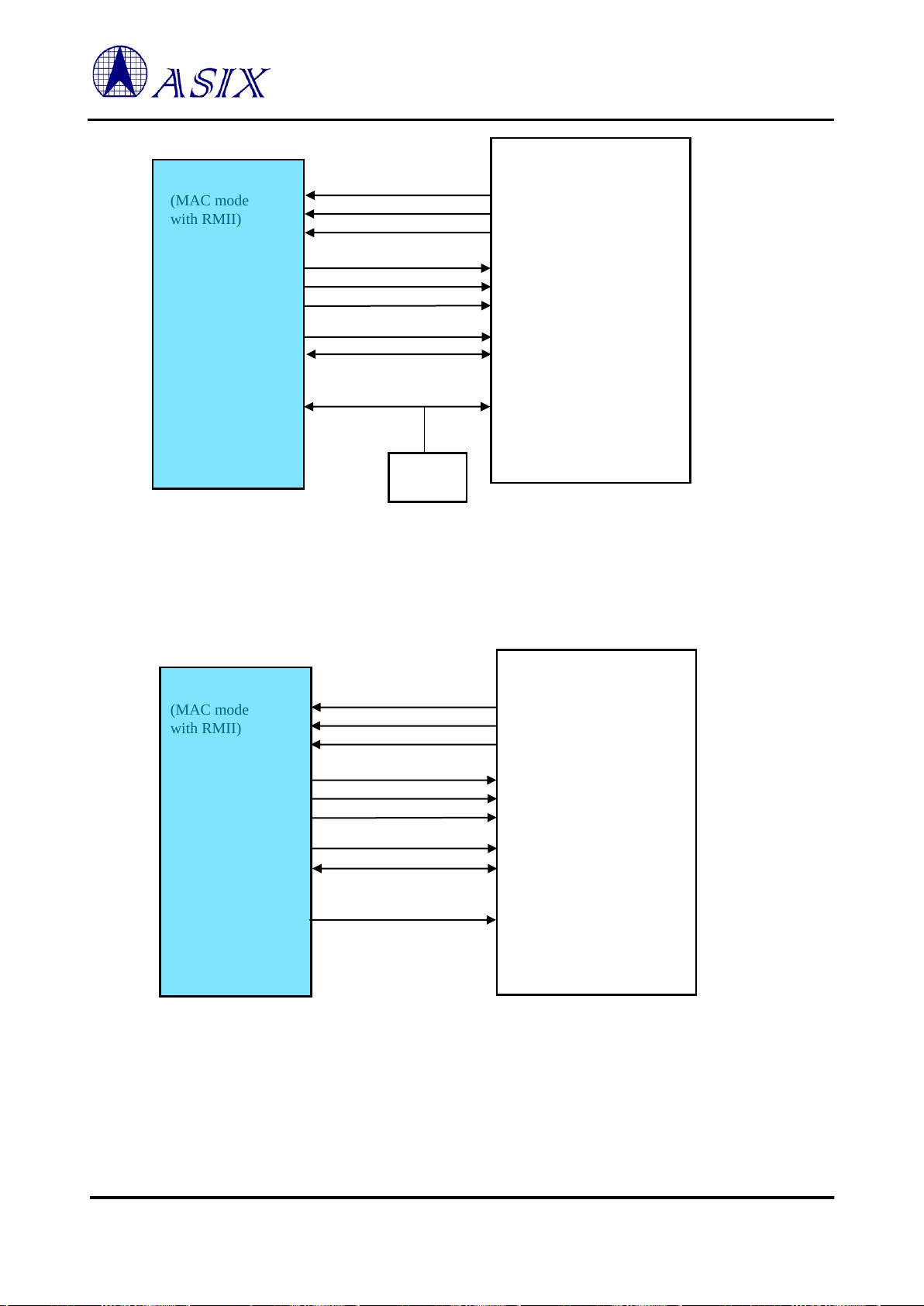

In MAC mode, the AX88772B internal datapath can work with internal Ethernet PHY or RMII interface by setting

Software Interface Selection register. Note that the PHY_ID for the internal Ethernet PHY and external one are

defined in below Table 3. Please refer to below Figure 9, Figure 10 for RMII example.

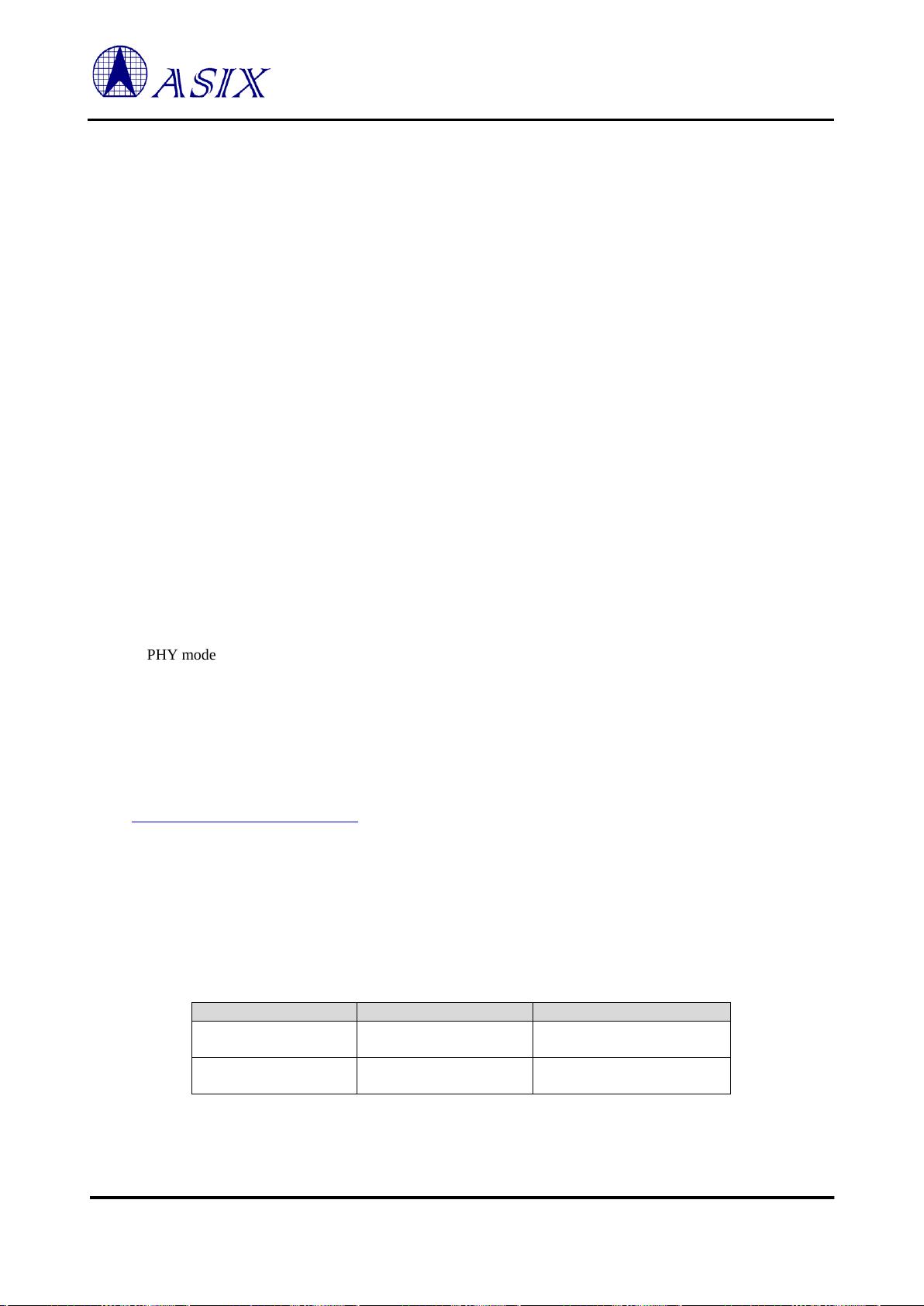

In PHY mode, the AX88772B Ethernet block is configured as an Ethernet PHY interface. In this case, an external

microcontroller with Ethernet MAC can interface with AX88772B as if it were to interface with an Ethernet PHY

chip, and AX88772B can act as a USB to Reverse-RMII bridge chip for the microcontroller to provide USB 2.0

device interface for some system applications (see Figure 4).

Please refer to below Figure 11, Figure 12 for Reverse-RMII example.

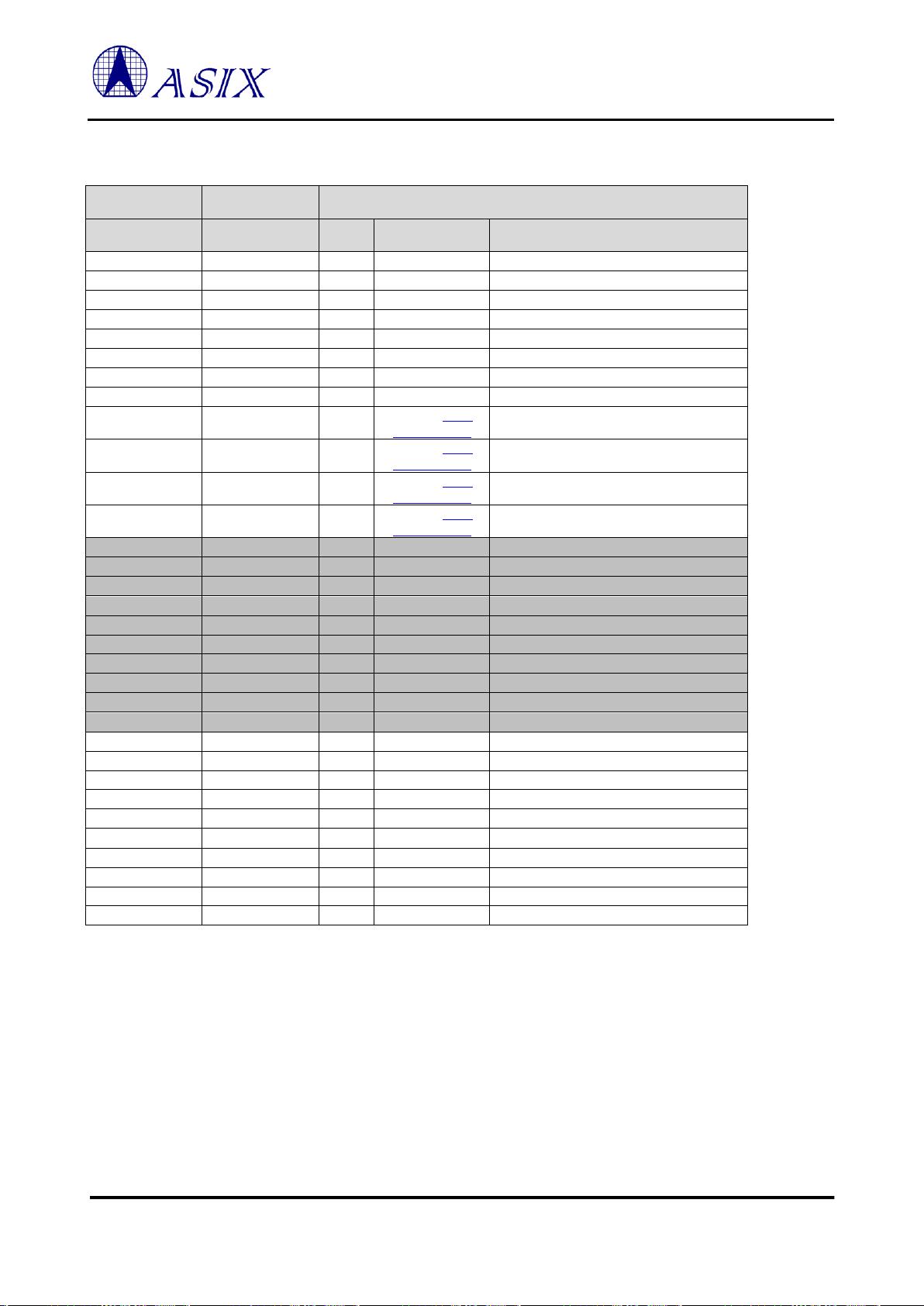

Embedded Ethernet PHY

PHY_ID [4:0]

External Media Interface

PHY_ID [4:0]

{Secondary PHY_ID [4:1], 0}

Note: The value of Secondary PHY_ID [4:0] is defined in EEPROM memory map 4.1.6

Table 3 : PHY_ID Definition Source