Verilog HDL模块通信深度探索

"这篇资源是关于Verilog HDL模块间通信的学习笔记,作者通过一系列的书籍和笔记,逐步深入地探讨了Verilog HDL的基本语法、建模技术、步骤和时钟的概念,以及最终的核心主题——模块的沟通。"

Verilog HDL是一种广泛使用的硬件描述语言,用于设计和验证数字电子系统,如CPLD和FPGA。在Verilog HDL中,模块是构成设计的基本单元,它们代表硬件电路的各个部分。模块间的沟通是实现复杂系统的关键,因为一个实际的电路通常由多个功能部件组成,这些部件需要协同工作。

模块通信主要包括以下几方面:

1. **输入和输出接口**:模块通过输入端口接收信号,并通过输出端口传递信号。这是最基本的通信方式,包括简单的线性连接和复杂的接口协议。

2. **双向接口**:除了单向通信,Verilog还支持双向数据传输,如`inout`类型的端口,允许数据同时流向两个方向。

3. **内部信号连接**:在模块内部,可以使用信号(wire或reg类型)进行数据交换,这些信号可以作为计算的结果或者控制流的标志。

4. **参数化设计**:通过参数化,可以创建可重用的模块,其中参数可以定制模块的行为。这有助于实现设计的模块化和可扩展性。

5. **任务(Task)和函数(Function)**:这两个特性允许定义自定义的操作,可以在不同模块中调用,增强了代码的复用性和模块间的协同。

6. **接口(Interface)**:接口是另一种组织和管理模块间通信的方式,它可以封装一组相关信号和方法,提供更清晰的抽象层次。

7. **例化(Instantiation)**:在Verilog中,通过例化可以创建模块的实例,将已定义的模块插入到更大的设计中,实例化时可以指定输入、输出信号的连接。

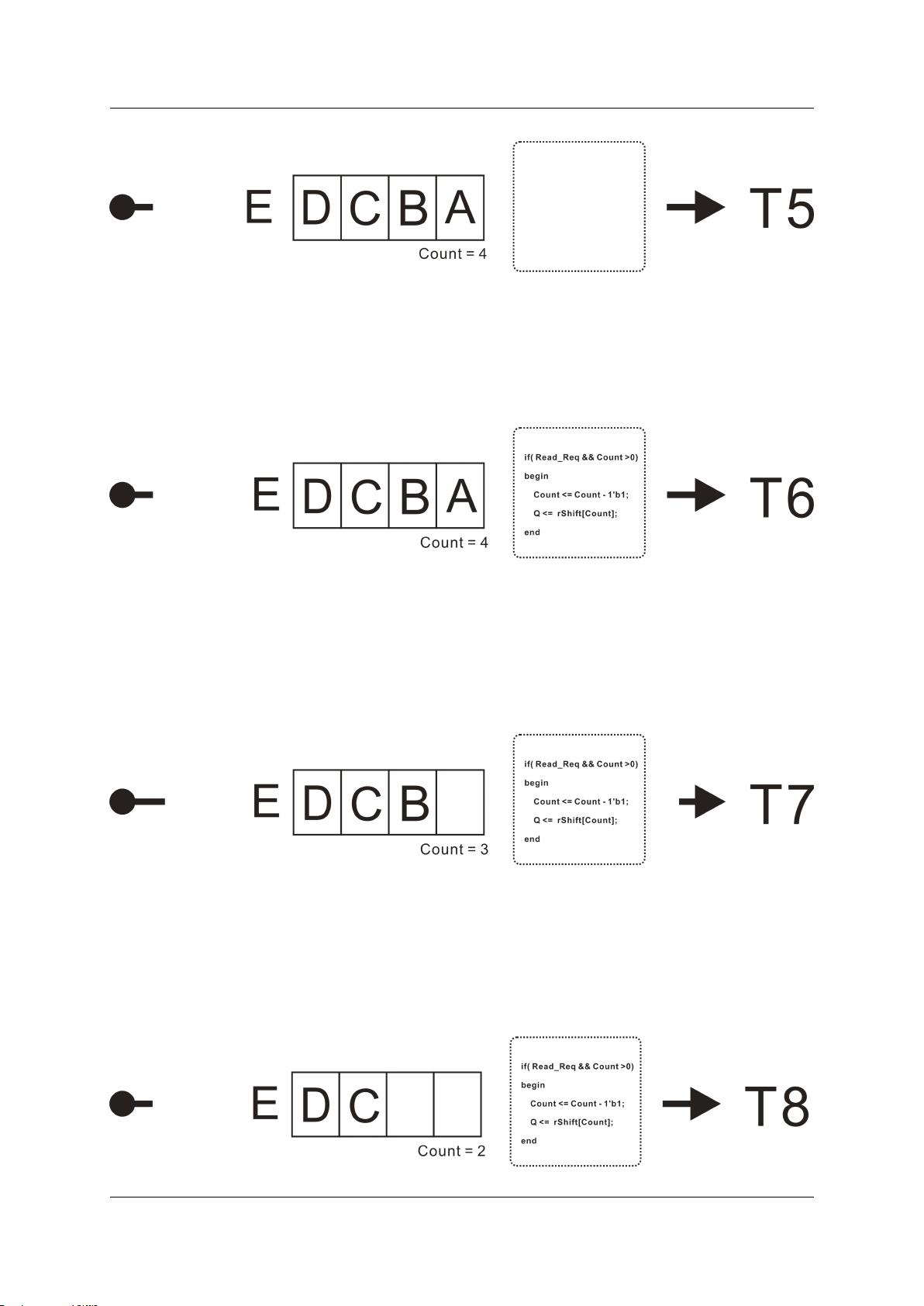

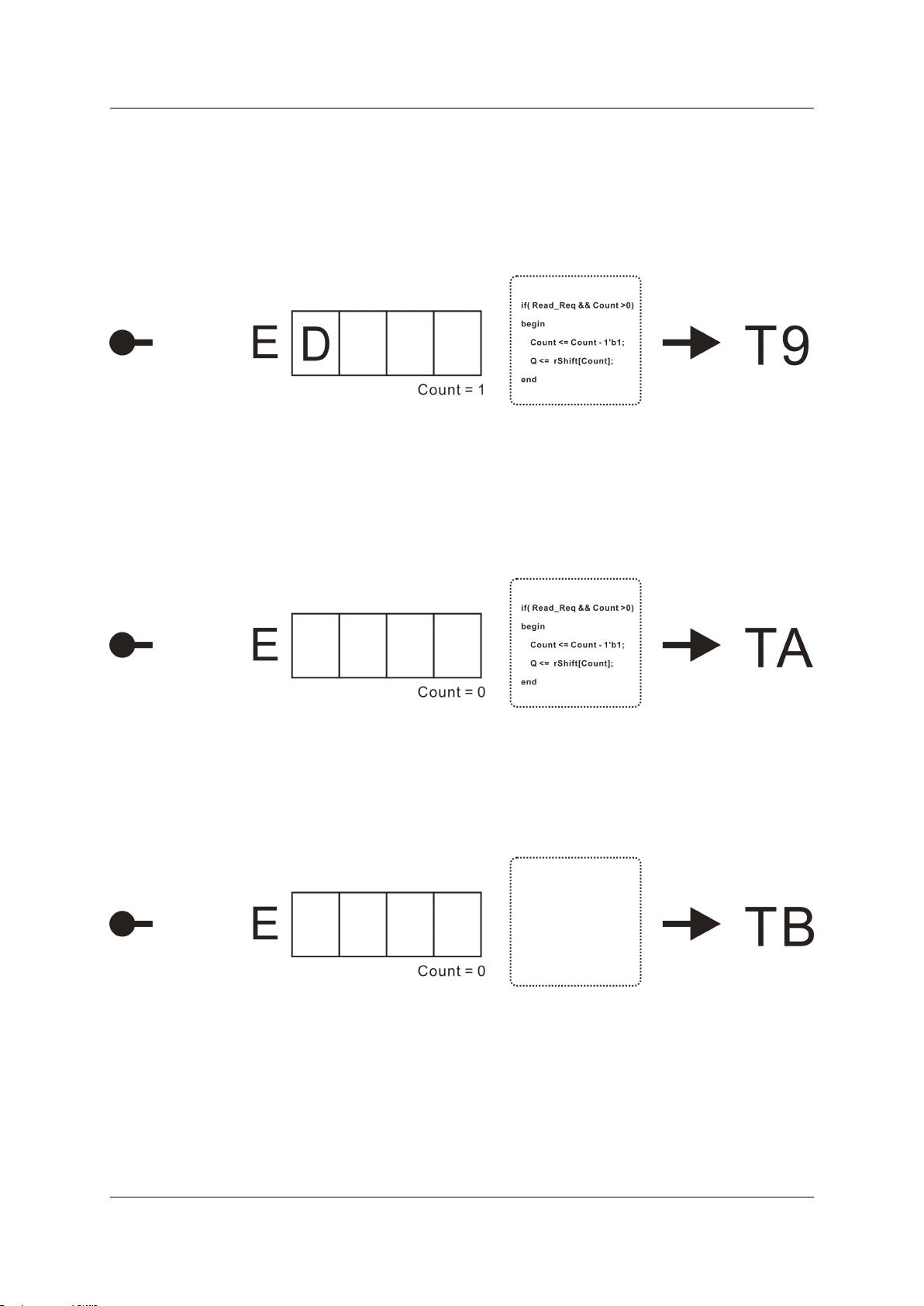

8. **事件驱动和时钟同步**:Verilog中的通信往往依赖于时钟边沿,模块间的数据交换需要考虑到时序约束,确保在正确的时钟周期内进行。

9. **非阻塞赋值(<=)和阻塞赋值(=)**:非阻塞赋值用于并行执行,而阻塞赋值则在当前时钟周期完成操作。理解这两者之间的区别对于正确描述并发行为至关重要。

10. **边界信号和接口(Boundary-Signal Interface, BSI)**:在系统级设计中,BSI允许不同IP核之间的通信,确保它们的时序匹配。

11. **高级建模技术**:例如,使用`always_comb`、`always_latch`和`always_ff`块来更精确地描述组合逻辑、边沿敏感的存储元素和同步逻辑。

作者在笔记中强调,理解步骤和时钟在Verilog HDL建模中的作用至关重要,因为它们定义了信号如何随着时间变化和模块如何交互。模块间的有效沟通需要对这些概念有深刻的理解,才能避免时序错误和设计缺陷。通过从基础语法开始,逐步深入到复杂的建模技巧,作者希望读者能够逐步掌握Verilog HDL的精髓,实现高效且可靠的硬件设计。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2012-12-23 上传

2019-07-11 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

2018-09-04 上传

ourearth2010

- 粉丝: 0

- 资源: 8

最新资源

- CricScore

- MIC24085芯片设计的DC12V-DC5V降压稳压电路模块ALTIUM设计硬件原理图+PCB工程文件.zip

- eStruts-1.1-开源

- 管理系统系列--运动会管理系统.zip

- 消灭JavaScript怪兽第三季ES6/7/8新特性(10-12)

- 电子功用-多功能电子墙壁挂画

- LibCK3.Tokens:LibCK3的CK3令牌信息

- star-wars-app

- 应用于 POS 机、收银机等80mm 高速微型打印机(原理图、上位机、程序源码)-电路方案

- 消灭JavaScript怪兽第三季ES6/7/8新特性(5-9)

- 管理系统系列--在线学习管理系统,SSM框架的简单实践.zip

- vicinity-neighbourhood-manager:基于Web的应用程序,用于管理在VICINITY Neighbourhood Manager中注册的设备和服务

- python参数校验jsonschema

- vai-passar:在困难时刻提供帮助的应用程序

- 电子功用-基于聚偏氟乙烯压电薄膜的光声气体传感装置

- LogisticRegression_SpamOpinion