Intel Quartus Prime FPGA设计约束与I/O管理

需积分: 9 105 浏览量

更新于2024-07-16

收藏 1.32MB PDF 举报

"ALTERA FPGA设计约束主要涉及对FPGA设计的定时、逻辑以及I/O分配的详细控制,以优化编译过程并确保设计满足性能要求。本文档更新至Intel® Quartus® Prime Design Suite的18.1版本,提供了在GUI和Tcl脚本中设定设计约束的方法,以及管理设备I/O引脚的策略。"

在ALTERA FPGA设计中,约束起着至关重要的作用,它们指导编译器如何高效地实现设计,确保满足关键的时序要求和逻辑功能。以下是对这些知识点的详细解释:

1. **设计约束**:

- **全局约束与分配**:全局约束涉及整个设计的属性,如全局时钟网络、电源电压设置等。它们影响设计的总体性能和功耗。

- **节点、实体和实例级约束**:这些约束针对设计中的特定部分,如特定逻辑门或模块,用于指定它们的时序、电源和布局需求。

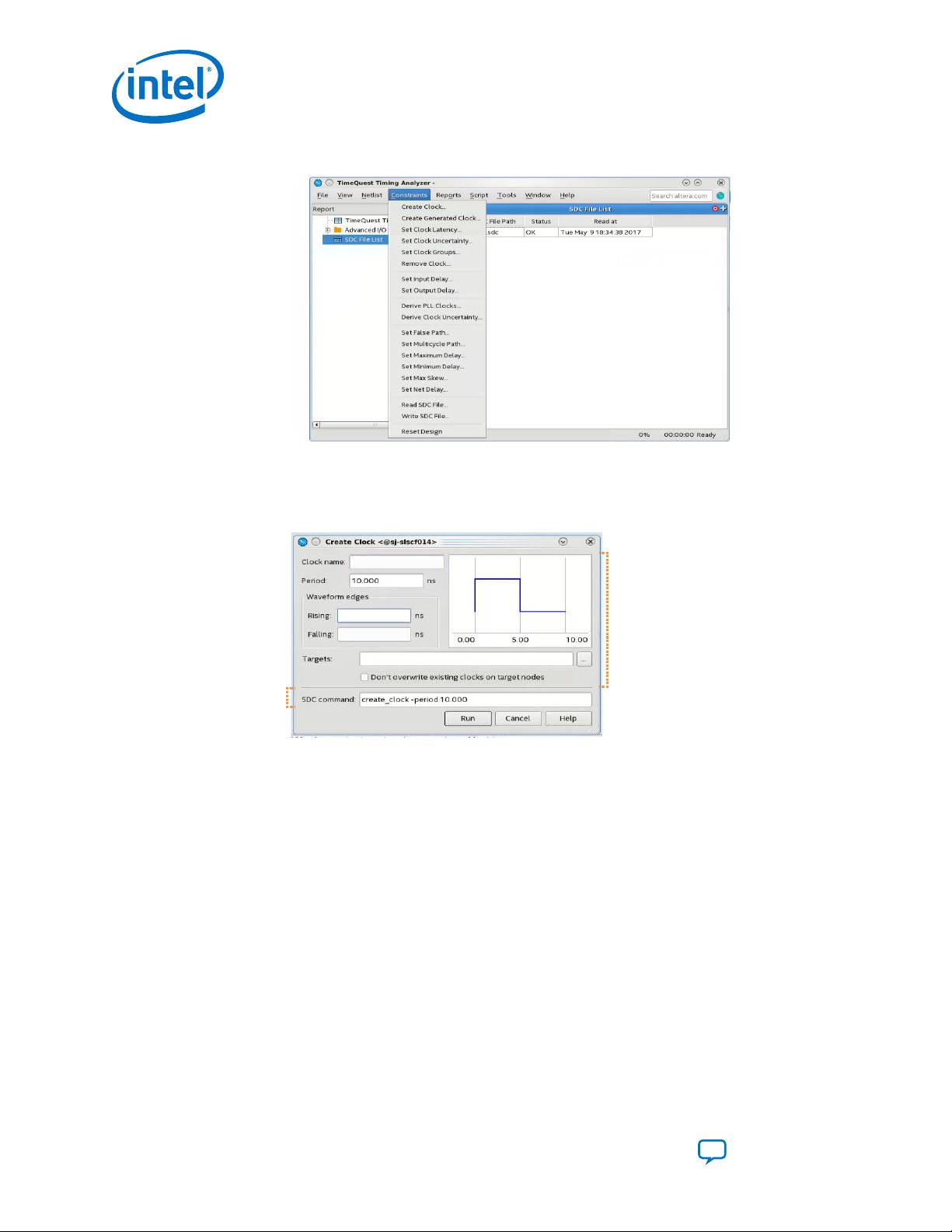

- **在Intel Quartus Prime GUI中探查组件**:用户可以通过GUI来检查和分析设计中的不同组件,以便更好地理解它们之间的相互作用和时序关系。

- **时序约束**:在GUI中设置时序约束,如建立时间、保持时间和路径延迟限制,以确保设计在预定的速度下正确运行。

2. **Tcl脚本约束设计**:

- **创建项目并应用约束**:通过编写Tcl脚本可以自动化设计流程,包括初始化项目和应用设计约束。

- **分配引脚**:Tcl脚本可以直接指定逻辑单元到特定引脚的映射,实现更精确的硬件布局。

- **生成Intel Quartus Prime设置文件**:这些设置文件保存了设计的配置和约束,可用于重复的编译过程。

- **Synopsys Design Constraint (SDC) 文件**:SDC文件是时序约束的标准格式,可在多个工具间共享,以确保一致性。

- **Tcl-only Script Flows**:完全使用Tcl脚本进行设计流程,提供更高的灵活性和自定义性。

3. **迭代脚本流程**:一个完全迭代的脚本流程允许用户反复调整约束和设计参数,以达到最佳性能。

4. **管理设备I/O引脚**:

- **I/O规划概述**:I/O规划是设计的重要组成部分,涉及到如何有效地利用FPGA的输入/输出资源。

- **基本I/O规划流程**:包括定义I/O标准、分配引脚和验证I/O布局。

- **集成PCB设计工具**:与PCB设计软件的集成使得FPGA与PCB的协同设计成为可能,确保电气和物理兼容性。

- **Intel Device Terms**:ALTERA设备特有的术语,用于描述引脚的行为和特性。

- **分配I/O引脚**:可以分配给特定的引脚组,以满足信号速率和驱动强度的需求,同时考虑信号完整性和电磁干扰。

通过理解并应用这些约束,设计者可以有效地优化ALTERA FPGA的设计,提高其性能,降低功耗,并确保与外部系统的正确通信。无论是通过直观的GUI界面还是强大的Tcl脚本,都能实现对设计的精细化管理,满足各种复杂的应用场景。

2013-07-23 上传

点击了解资源详情

点击了解资源详情

2023-10-03 上传

2012-07-20 上传

2021-10-03 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

liujie19862008

- 粉丝: 0

- 资源: 4

最新资源

- PIEROutil:PIERO的AR客户端库(http

- terraform-courses

- bender:JIRA微管理助手

- phywcri,c语言曲线拟合源码下载,c语言

- PersonAttributeExt:人物属性提取

- 基于JAVA图书馆座位预约管理系统计算机毕业设计源码+数据库+lw文档+系统+部署

- poordub:可怜的人的PyDub

- system-simulation:使用 networkx python 库在图上模拟医院位置

- 4411513,socket源码c语言,c语言

- 52挂Q v1.3

- app-status

- srpagotest

- kettle的web版本,自己编译的war包,直接放到tomcat下运行,然后http://localhost:8080/web

- Ksdacllp-Backend:Ksdacllp后端

- chromedriver-linux64-V124.0.6367.91 稳定版

- php-pdf-filler