Cortex-M3 技术参考手册:内核与中断管理详解

"Cortex-M3 技术参考手册.pdf"

Cortex-M3 是 ARM 公司设计的一款基于 ARMv7-M 架构的微处理器内核,广泛应用于嵌入式领域,尤其在微控制器(MCU)中非常常见。这份技术参考手册详细介绍了 Cortex-M3 的各个方面,是学习和开发基于 Cortex-M3 内核芯片的基础资料。

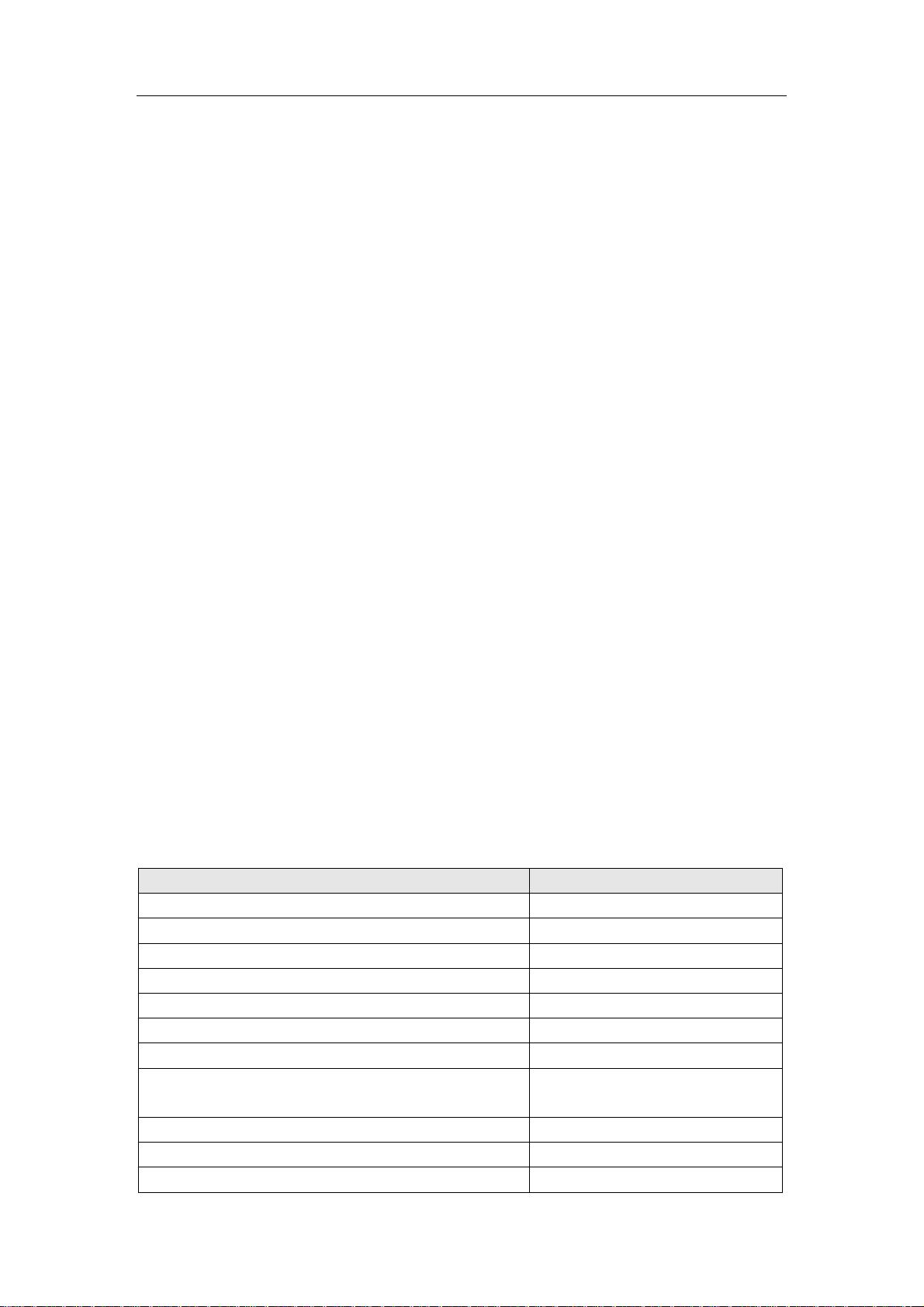

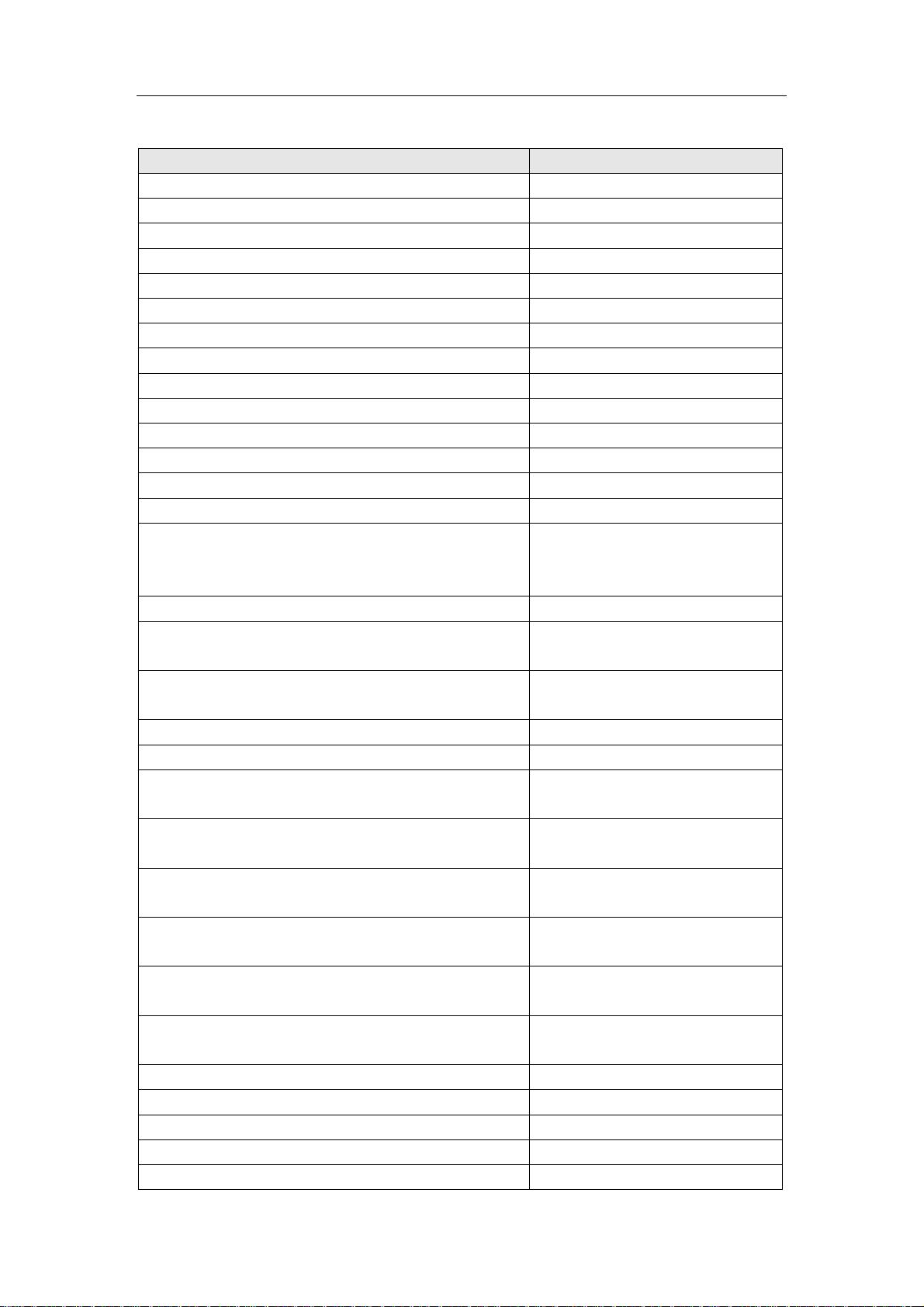

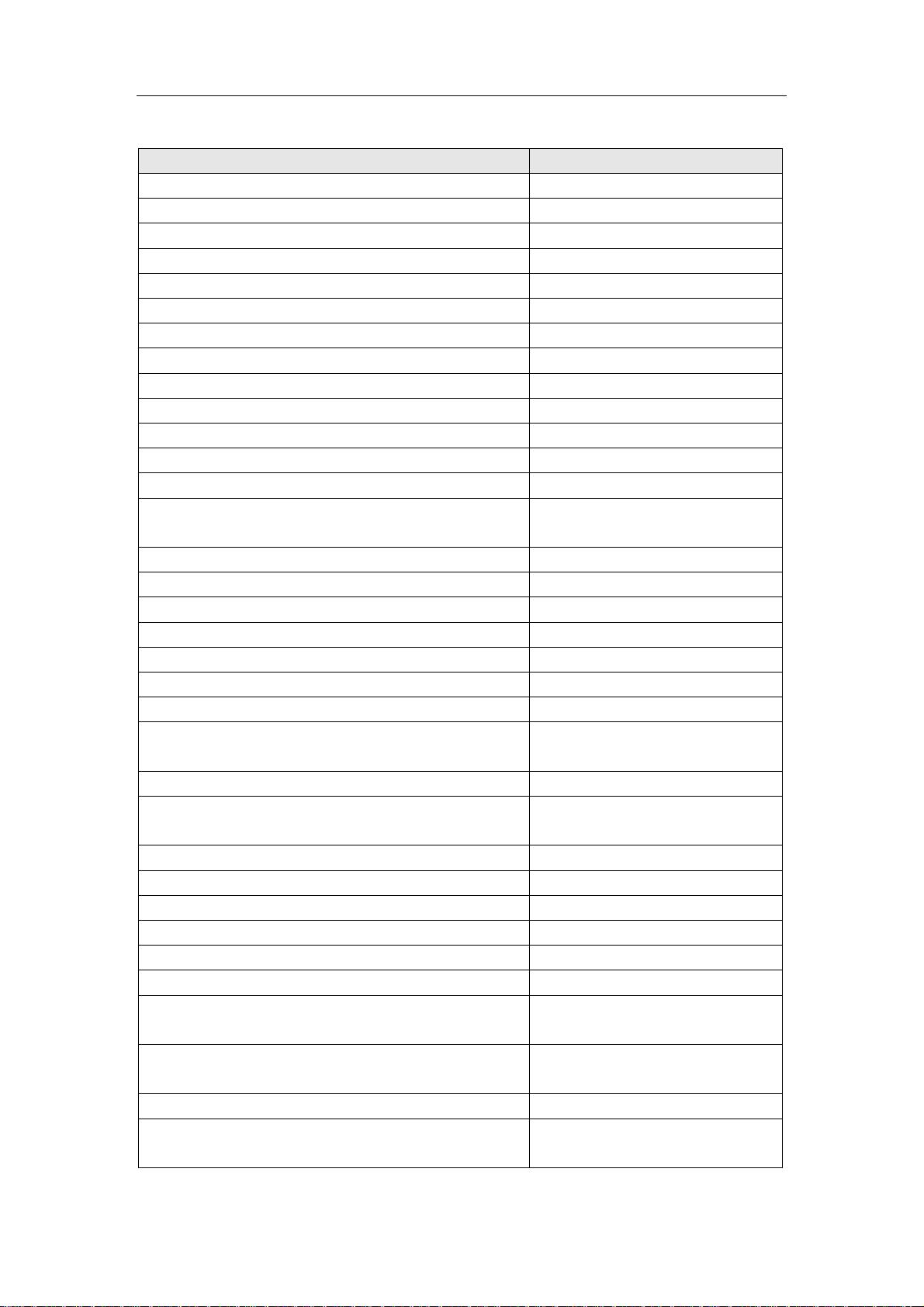

手册首先介绍了 Cortex-M3 的概述,包括处理器的基本特性、组件以及可配置的选项。处理器由多个组件构成,如处理器内核、嵌套向量中断控制器(NVIC)、总线矩阵、快闪程序存储器分页缓冲(FPB)、数据写入跟踪(DWT)、仪器触发模块(ITM)、内存保护单元(MPU)、嵌入式跟踪宏单元(ETM)、测试协议接口单元(TPIU)等。这些组件共同构成了 Cortex-M3 内核的完整功能。

编程模型部分详细阐述了 Cortex-M3 的工作模式、状态、寄存器布局、数据类型、存储器格式和指令集。处理器具有多种工作模式,如系统模式和线程模式,以及不同的工作状态,如Thumb和Thumb-2指令集。寄存器包括通用寄存器和特殊用途的程序状态寄存器(xPSR)。数据类型覆盖了不同宽度的整型和浮点型,而存储器格式则涉及到字对齐和半字对齐等。指令集包含了 Thumb-2 指令,这是一种高效节能的16/32位混合指令集。

系统控制章节涉及了处理器的寄存器,包括 NVIC、调试相关寄存器、MPU、TPIU 和 ETM 等的寄存器结构,这些寄存器用于配置和控制处理器的运行行为。

存储器映射部分详细解释了 Cortex-M3 中存储器的组织方式,如 bit-banding 技术,它允许对单个位进行直接操作,还有 ROM 存储器表,这对于了解和管理程序的静态存储区域至关重要。

异常模型是 Cortex-M3 处理中断和异常的基础,手册中描述了异常的分类、优先级、处理流程、堆栈管理、占先机制、末尾连锁、迟来和退出过程。异常模型还包括复位处理,包括复位向量表和启动顺序,这对于系统初始化和异常恢复非常重要。

整体来看,Cortex-M3 技术参考手册提供了全面深入的技术信息,对于理解和开发基于 Cortex-M3 的嵌入式系统具有极高的价值。通过学习这份手册,开发者能够掌握 Cortex-M3 的核心特性,编写高效的嵌入式代码,并有效地调试和优化系统。

点击了解资源详情

510 浏览量

点击了解资源详情

2021-11-24 上传

193 浏览量

170 浏览量

4026 浏览量

441 浏览量

2021-11-27 上传

_Sam大叔

- 粉丝: 0

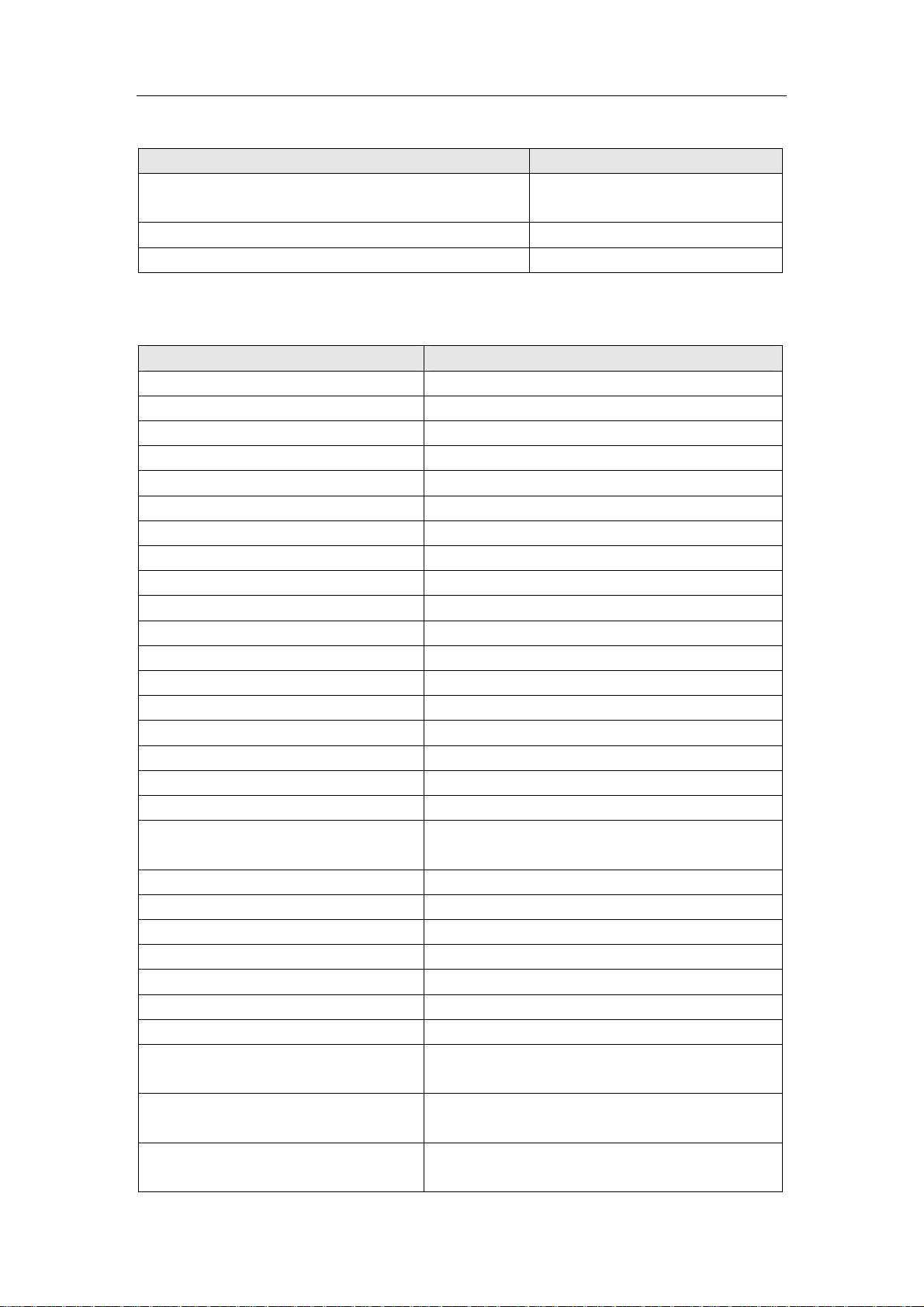

最新资源

- QCo-editor:跨平台Cocos2d-x开源编辑器

- cocos2d-x 2.14版本SneakyJoystick API修改详解

- 石材辅助工具1.0快捷键RC自动编号功能评测

- 蚁群算法C语言实现及详细解析

- 将SQL数据高效转换为XML格式的方法

- C#实现RSA加密算法的示例教程

- dot_vim:Champion Champion的Vim插件和配置管理指南

- SSH框架人力资源系统开发指南

- 使用qt进行串口通信测试的方法与实践

- React封装Ladda按钮:加载指示器实现指南

- 云数据库CouchDB与Cloudant搜索的Docker集成实现

- 蚁群算法在VB中的实现及详细解析

- Easyxy图形界面实现Devcpp学生管理系统

- 飞凌-MX6UL GPS模块测试流程与连接指南

- MAYA建模插件精选合集:提升3D建模效率

- 无需权限的PHP文件上传模块实现