Cortex-M3技术参考手册:单片机编程精华

需积分: 48 51 浏览量

更新于2024-07-25

收藏 1.67MB PDF 举报

“Cortex-M3技术参考手册.pdf”是一份由周功写(周立功)翻译的经典技术文档,详细介绍了ARM Cortex-M3处理器的技术细节和编程模型。

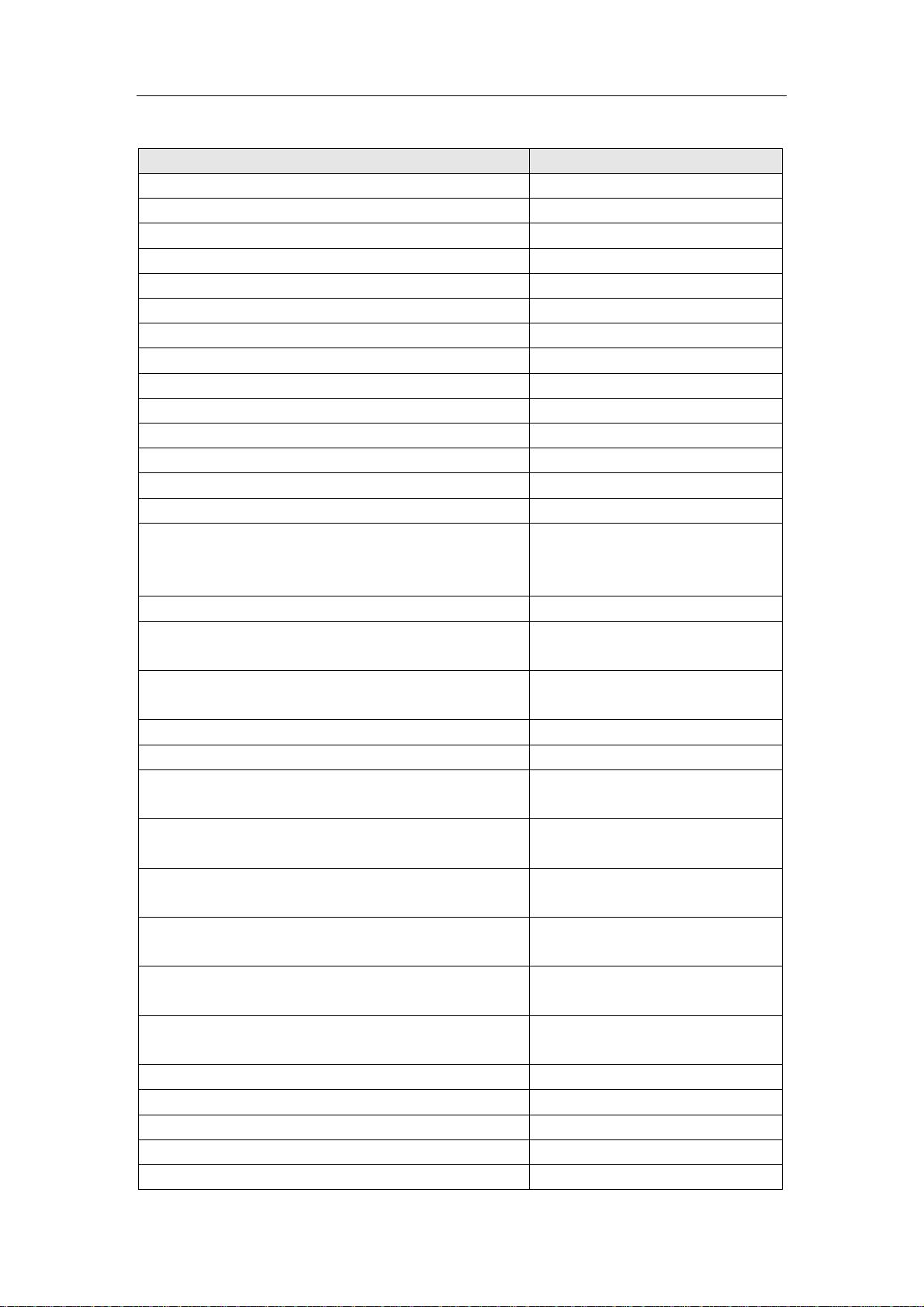

Cortex-M3是ARM公司设计的一种高效能、低功耗的微控制器核心,广泛应用于嵌入式系统。手册首先对Cortex-M3处理器进行了概述,包括处理器的基本结构和组件。处理器的组件包括处理器内核、嵌套向量中断控制器(NVIC)、总线矩阵、快存配置块(FPB)、数据写监视器(DWT)、仪器触发模块(ITM)、内存保护单元(MPU)、嵌入式跟踪宏单元(ETM)、 tracesnoop 终端接口单元(TPIU)、软件/ JTAG调试端口(SW/JTAG-DP)等。

手册详细阐述了可配置的选项,如中断支持的灵活性、MPU的配置以及ETM的使用。中断系统是Cortex-M3中的关键部分,允许处理器响应外部事件。MPU允许对内存区域进行权限控制,防止非法访问。ETM则用于调试目的,提供执行跟踪功能。

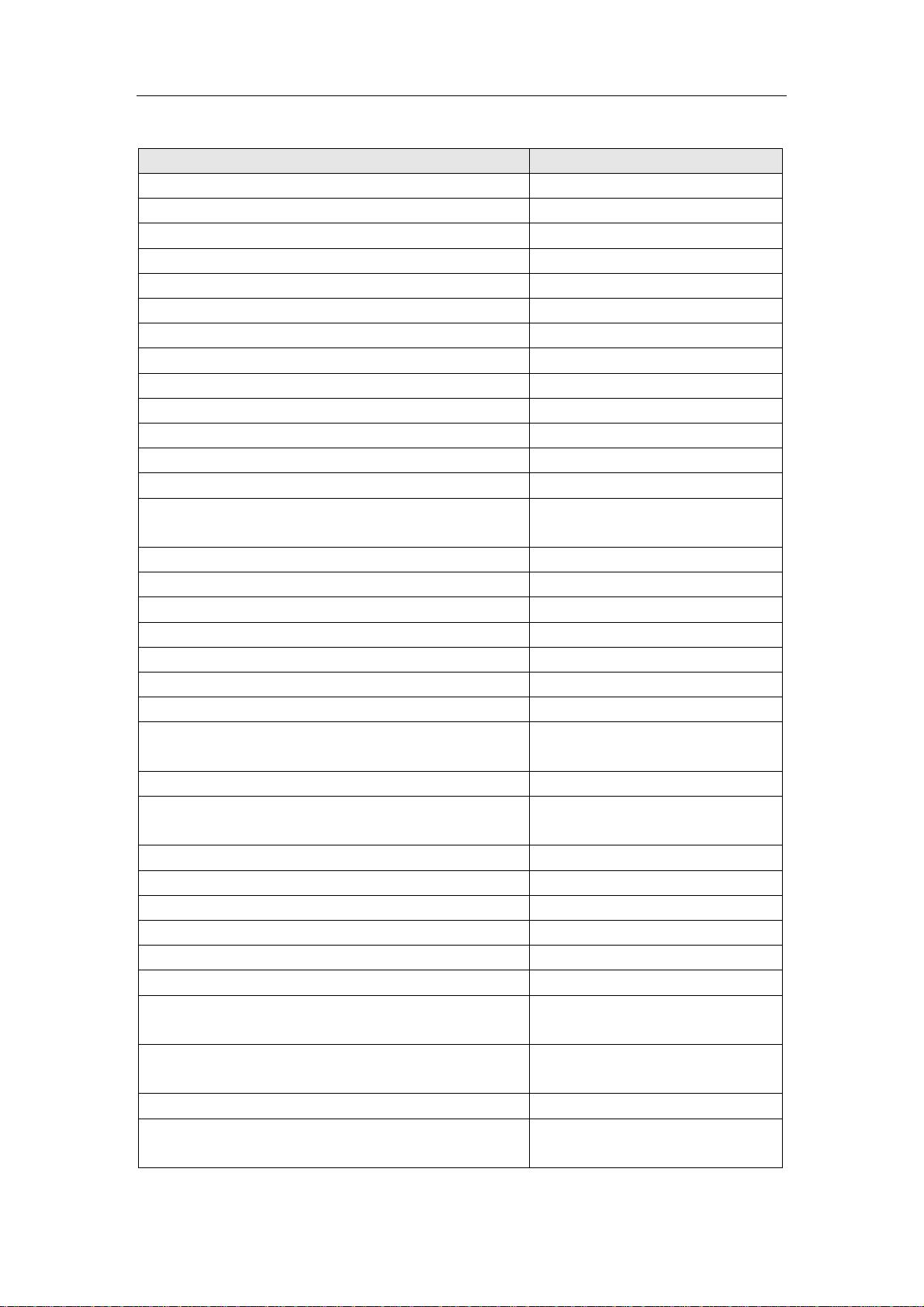

编程模型章节解释了Cortex-M3的运行环境,包括工作模式(如系统模式、handler模式等)和工作状态(如THUMB和ARM状态)。手册还详细描述了寄存器布局,通用寄存器、程序状态寄存器(xPSR)的功能,以及不同数据类型的存储格式。此外,存储器格式和指令集也得到了详尽的阐述,帮助开发者理解如何在Cortex-M3上编写高效的代码。

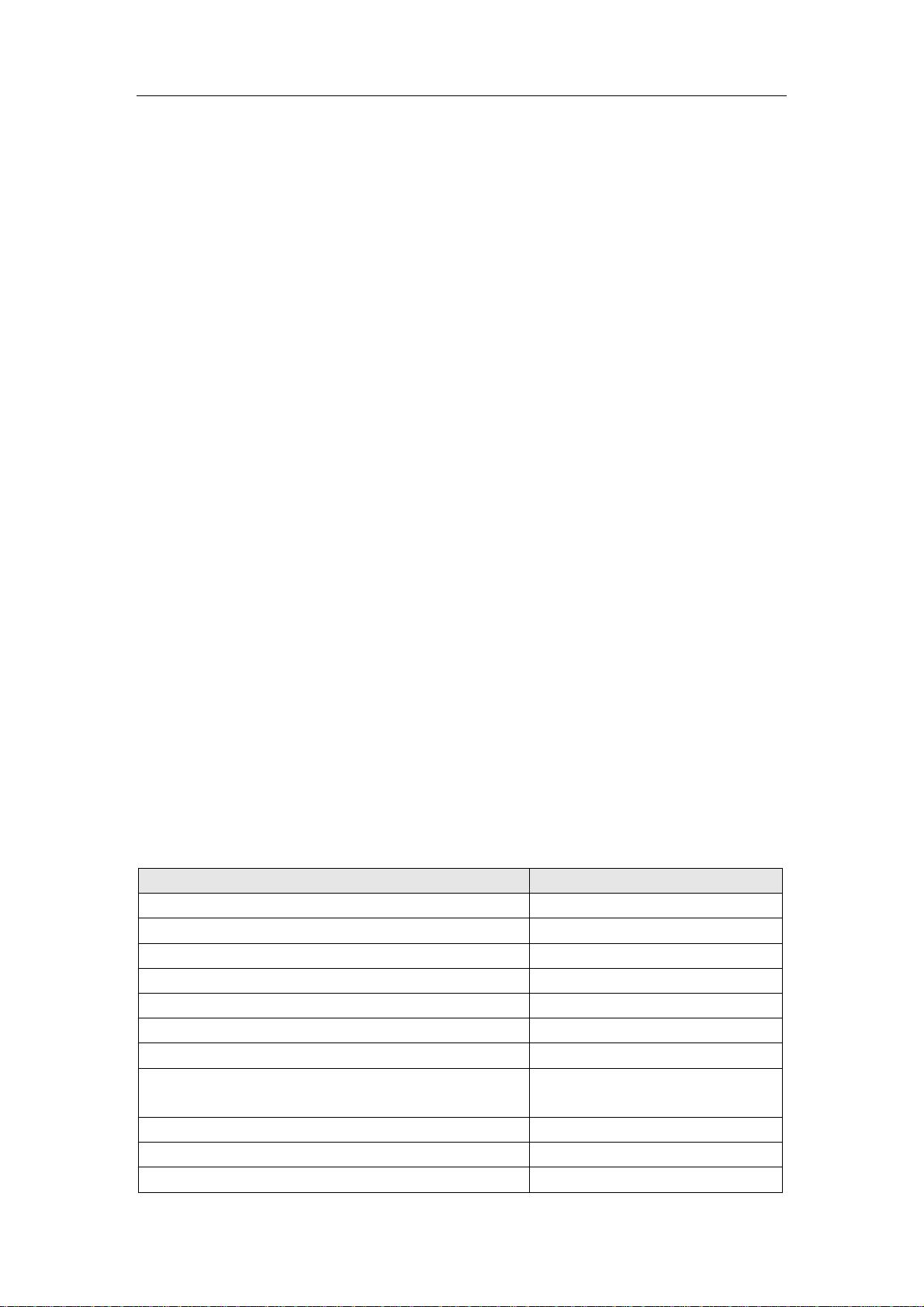

系统控制部分涉及处理器的各种寄存器,包括NVIC、调试和系统调试寄存器,以及与存储器保护和跟踪相关的寄存器。这些寄存器是理解和配置Cortex-M3系统的关键。

存储器映射章节讨论了如何在物理地址空间中组织和访问不同的存储区域,包括bit-banding特性,这是一种允许直接操作单个比特的技术。ROM存储器表则提供了关于固件存储的信息。

异常模型是Cortex-M3处理中断和异常的核心机制。手册详细讲解了异常的类型、优先级、处理流程、堆栈管理以及复位过程。异常模型的设计使得Cortex-M3能够有效地响应并处理各种运行时事件。

这份Cortex-M3技术参考手册是深入理解该处理器架构、编程模型和系统设计的宝贵资源,对于开发基于Cortex-M3的嵌入式系统工程师来说极具价值。

2009-03-15 上传

222 浏览量

2010-08-18 上传

2013-04-25 上传

355 浏览量

2017-10-19 上传

2021-11-27 上传

2022-03-15 上传

107 浏览量

gqb666

- 粉丝: 439

- 资源: 121

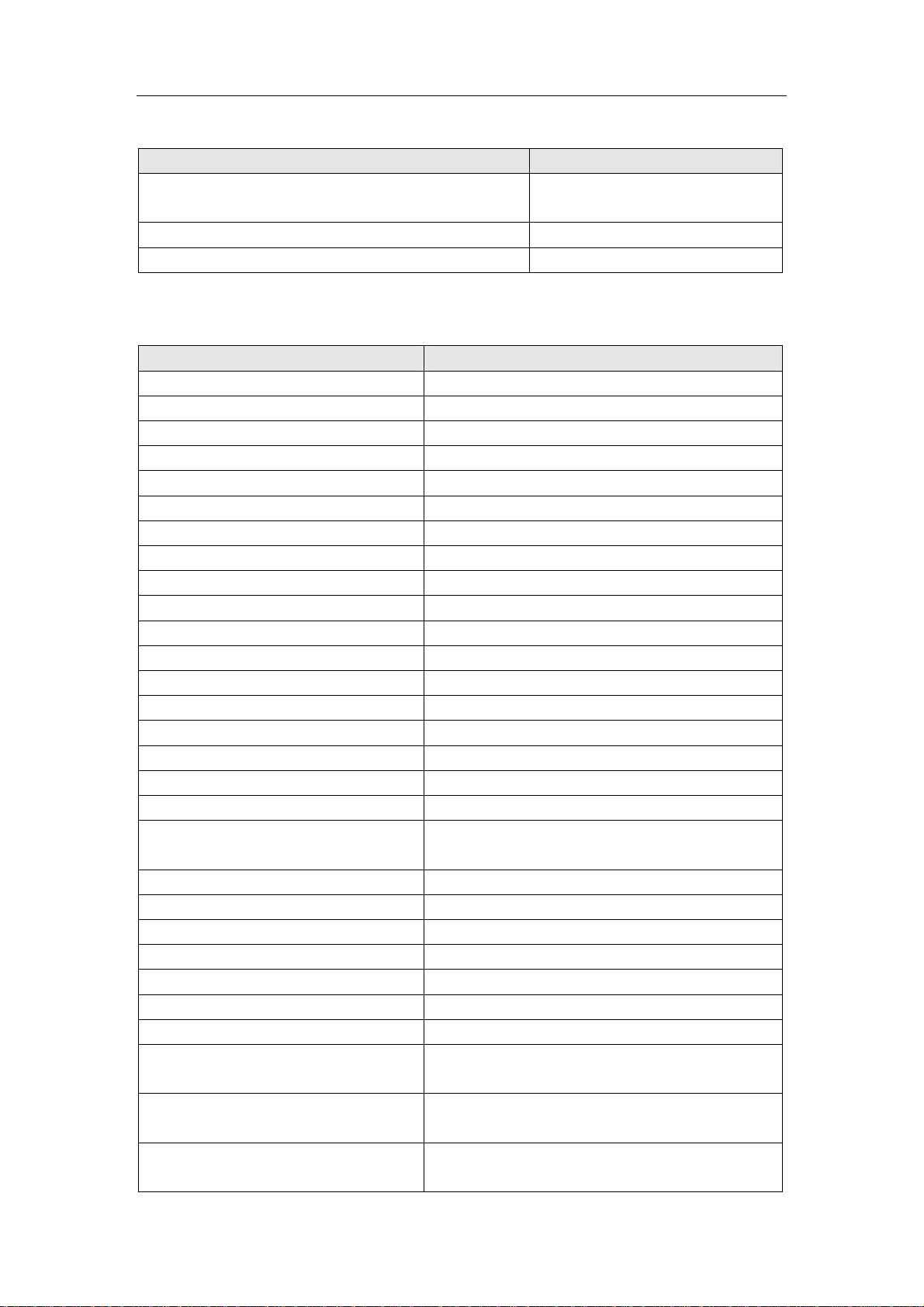

最新资源

- StarModAPI: StarMade 模组开发的Java API工具包

- PHP疫情上报管理系统开发与数据库实现详解

- 中秋节特献:明月祝福Flash动画素材

- Java GUI界面RPi-kee_Pilot:RPi-kee专用控制工具

- 电脑端APK信息提取工具APK Messenger功能介绍

- 探索矩阵连乘算法在C++中的应用

- Airflow教程:入门到工作流程创建

- MIP在Matlab中实现黑白图像处理的开源解决方案

- 图像切割感知分组框架:Matlab中的PG-framework实现

- 计算机科学中的经典算法与应用场景解析

- MiniZinc 编译器:高效解决离散优化问题

- MATLAB工具用于测量静态接触角的开源代码解析

- Python网络服务器项目合作指南

- 使用Matlab实现基础水族馆鱼类跟踪的代码解析

- vagga:基于Rust的用户空间容器化开发工具

- PPAP: 多语言支持的PHP邮政地址解析器项目