1–6 Chapter 1: About This MegaCore Function

Performance and Resource Utilization

FFT MegaCore Function User Guide © November 2009 Altera Corporation

Table 1–7 lists resource usage with burst data flow architecture, using the 4 multipliers

/2 adders complex multiplier structure, for data and twiddle width 16, for Cyclone III

(EP3C10F256C6) devices.

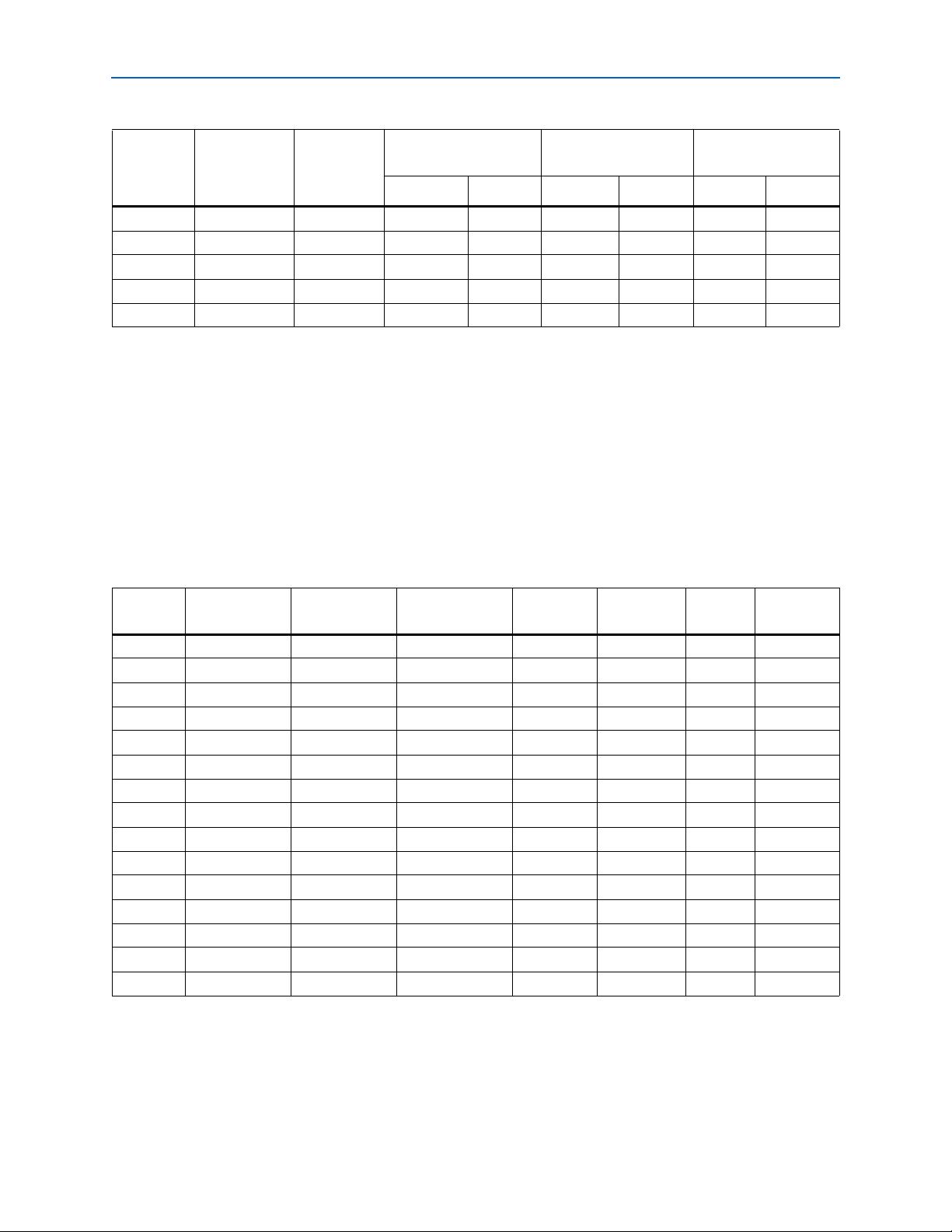

1,024 (5) 2 220 557 2.53 1,581 7.18 1,163 5.28

4,096 2 231 2,607 11.28 6,703 29.01 5,133 22.22

256 4 215 118 0.55 347 1.61 283 1.32

1,024 4 206 340 1.65 1,364 6.61 1,099 5.33

4,096 4 207 1,378 6.64 5,474 26.38 4,633 22.33

Notes to Table 1–6:

(1) When using the buffered burst architecture, you can specify the number of quad-output engines in the FFT MegaWizard interface. You may

choose from one, two, or four quad-output engines in parallel.

(2) In a buffered burst data flow architecture, transform time is defined as the time from when the N-sample input block is loaded until the first

output sample is ready for output. Transform time does not include the additional N-1 clock cycle to unload the full output data block.

(3) Block throughput is the minimum number of cycles between two successive start-of-packet (sink_sop) pulses.

(4) EP3C10F256C6 device.

(5) EP3C16F484C6 device.

Table 1–6. Performance with the Buffered Burst Data Flow Architecture—Cyclone III Devices (Part 2 of 2)

Points

Number of

Engines (1)

fMAX

(MHz)

Transform Calculation

Time (2)

Data Load & Transform

Calculation

Block Throughput

(3)

Cycles Time (s) Cycles Time (s) Cycles Time (s)

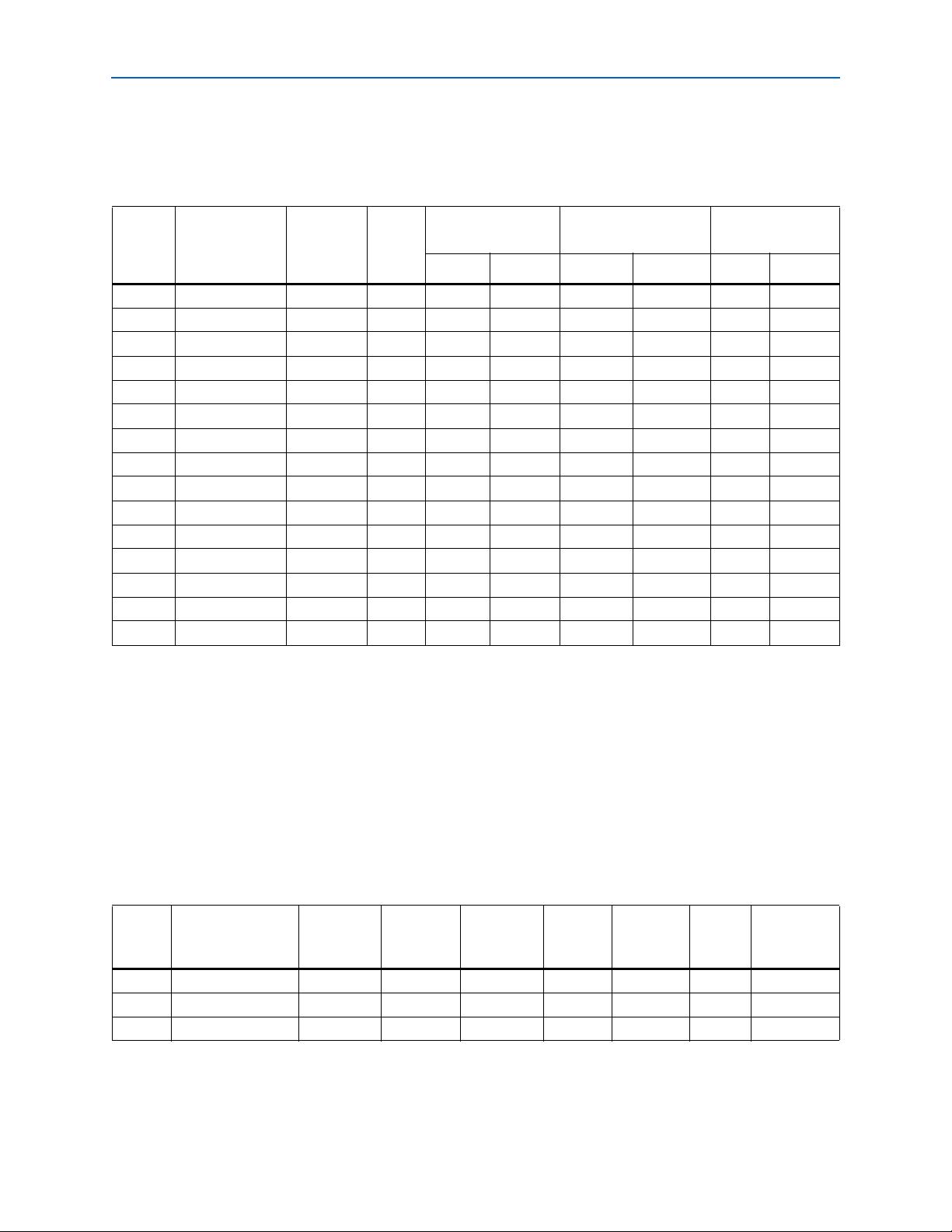

Table 1–7. Resource Usage with the Burst Data Flow Architecture—Cyclone III Devices

Points

Engine

Architecture

Number of

Engines (2)

Combinational

LUTs

Logic

Registers

Memory

(Bits)

Memory

(M9K)

9 × 9

Blocks

256 Quad Output 1 3,110 3,672 14,592 8 24

1,024 Quad Output 1 4,207 5,023 175,392 20 24

4,096 Quad Output 1 3,278 4,022 229,632 28 24

256 Quad Output 2 5,093 5,824 14,592 15 48

1,024 Quad Output 2 5,189 6,016 57,600 15 48

4,096 Quad Output 2 5,270 6,192 229,632 28 48

256 Quad Output 4 8,906 10,556 14,592 28 96

1,024 Quad Output 4 9,017 10,765 57,600 28 96

4,096 Quad Output 4 9,128 10,955 229,632 28 96

256 Single Output 1 1,465 1,495 9,472 3 8

1,024 Single Output 1 1,528 1,541 37,120 6 8

4,096 Single Output 1 1,620 1,587 147,712 19 8

256 Single Output 2 2,079 2,406 14,592 9 16

1,024 Single Output 2 2,131 2,482 57,600 11 16

4,096 Single Output 2 2,194 2,558 229,632 28 16

Notes to Table 1–7:

(1) When using the burst data flow architecture, you can specify the number of engines in the FFT MegaWizard interface. You may choose from

one to two single-output engines in parallel, or from one, two, or four quad-output engines in parallel.